Eisenfaust

Banned

- Registriert

- Feb. 2007

- Beiträge

- 1.212

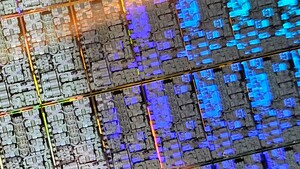

Irgendwann muß einmal Zäsur sein. PCI ist ein Relikt, das Chipsätze und Platinen teuer macht. Die Leitungsverlegung kostet Zeit, Material, Platz auf der Platine und ist letztlich fraglich in der Verwendbarkeit.

Intel hat Fakten geschaffen. Die Chipsätze beherbegen keinen PCI Controller merh. PCI Funktionalität muß über einen Brückenbaustein realisiert werden. Habt ihr euch schon mal überlegt, wo dieser Brückenbaustein denn angebunden werden muß? Richtig, vermutlich konsumiert er ein der wenigen PCIe-Lanes der MCH. Leider "quetschen" Billighersteller wie ASUS, GigaByte, MSI, ASRock und viele andere auf diese wenigen PCIe-Lanes des MCH alles, was man so an Peripherie gerne haben möchte. Da wären dann Netzwerkchips, manchmal sogar zwei davon (und meistens wird die Intel-eigene PHYS gar nicht benutzt!), da sind die USB 3.0-Controller mit ihrer enormen Bandbreite (na, klingelt es, wieso sind wohl nur zwei Ports verbaut? Scheint MSI nachgedacht zu haben?), da sind eventuell noch weitere Chips für eSATA und additive SATA Ports und, nicht zuletzt, PCIe Slots, die neben den Slots für PEG zu den von der CPU bereitgestellten PCIe Lanes angeboten werden. Mal davon abgesehen, daß das DMI 2.0 schon jetzt bei einem Z68 reichlich auf dem letzten Loch pfeifft, was Bandbreitenangebot betrifft, darf man getrost sagen, daß bei der üppigen Ausstattung so mancher Boards dieses Problem der Bandbreite gar nicht mehr bis zum DMI 2.0 reicht, denn die "Verstopfung" tritt bereits an der einen oder anderen rücksichtslos überladenen PCIe Lane auf!

In solchen Fällen hilft oft ein Blick in die technischen Manuale des Mainboards. Allerdings gewähren Spezialisten im Überladen wie ASUS und GigaByte nur in den seltensten Fällen Einblicke in das Routing der Verbindungen ihrer kundenfangtauglichen AddOns.

Dann ist weniger oft mehr!

Wenn der X79 das geworden wäre, was Intel noch zur CES 2011 unterschwellig in Aussicht gestellt hatte, wäre dieser Chip eigentlich das geworden, was man von einem wirklichen Highend MCH für den echten Profieinsatz hätte erwarten können. Das DMI 3.0 mit seinen 4 PCIe 3.0 Lanes hätte das Gröbste abfangen können und bis auf USB 3.0 war ja eigentlich mit SAS 2.0 alles an Bord, was man braucht, um eine echte Workstation zu bauen, die nicht an irgendeiner latenten Verstopfung krankt. Aber nein, es kam ja anders, auch dieser Kater muste kastriert werden. Schnipp-Schnapp, Eier ab.

Tragt doch bitte Eure archaischen PCI Karten zu Grabe. Habe ich auch schweren Herzens getan. Hier liegt eine teure Soundkarte von MAudio. Nun unbrauchbar geworden, da kein PCI Steckplatz vorhanden. Aber so ist das nun mal. Jeder muß im Gefolge der Innovation auch ein Opfer bringen. Und mit etwas Weitblick wird man für die Zukunft eben etwas teurer und moderner einkaufen und nicht den Kinderkram fürs Kinderzimmer!

Addendum:

Was noch fehlt ist eine Beschreibung der Lane-Verteilung bei den Slost, die von der CPU bedient werden. Soweit ich weiß kann der PCIe Rootkomplex (der ja beim Sandy-Bridge-E erstmal nur auf PCIe 2.0 arbeiten wird) Diverse Knotenkonfigurationen bereitstellen, ohne daß ein zusätzlicher Switchbaustein nötig ist. Ich vermute, daß bei den Platinen mit mehr als zwei 16x PEGs der dritte Peg, wenn belegt, 8 Lanes von einem Nachbarn abgreift und den Nachbarn dann zu einem 8Lane Slot macht. Bei vier PEGs werden bei Bestückung dann wohl die vier je mit 8 Lanes versorgt.

Aber: SB-E hat ja 36 Lanes (abgezogen habe ich schon die 4 Lanes für das DMI). Vier 8-Lanes oder 2 16-Lanes PEG lassen 4 Lanes über. Ich sehe aber keinen physikalischen 8x oder 4x Slot, sondern nur 1x Slots. Wird MSI etwa die PCIe Lanes des MCH gar nicht nutzen und nur die Lanes der CPU verteilen?

Intel hat Fakten geschaffen. Die Chipsätze beherbegen keinen PCI Controller merh. PCI Funktionalität muß über einen Brückenbaustein realisiert werden. Habt ihr euch schon mal überlegt, wo dieser Brückenbaustein denn angebunden werden muß? Richtig, vermutlich konsumiert er ein der wenigen PCIe-Lanes der MCH. Leider "quetschen" Billighersteller wie ASUS, GigaByte, MSI, ASRock und viele andere auf diese wenigen PCIe-Lanes des MCH alles, was man so an Peripherie gerne haben möchte. Da wären dann Netzwerkchips, manchmal sogar zwei davon (und meistens wird die Intel-eigene PHYS gar nicht benutzt!), da sind die USB 3.0-Controller mit ihrer enormen Bandbreite (na, klingelt es, wieso sind wohl nur zwei Ports verbaut? Scheint MSI nachgedacht zu haben?), da sind eventuell noch weitere Chips für eSATA und additive SATA Ports und, nicht zuletzt, PCIe Slots, die neben den Slots für PEG zu den von der CPU bereitgestellten PCIe Lanes angeboten werden. Mal davon abgesehen, daß das DMI 2.0 schon jetzt bei einem Z68 reichlich auf dem letzten Loch pfeifft, was Bandbreitenangebot betrifft, darf man getrost sagen, daß bei der üppigen Ausstattung so mancher Boards dieses Problem der Bandbreite gar nicht mehr bis zum DMI 2.0 reicht, denn die "Verstopfung" tritt bereits an der einen oder anderen rücksichtslos überladenen PCIe Lane auf!

In solchen Fällen hilft oft ein Blick in die technischen Manuale des Mainboards. Allerdings gewähren Spezialisten im Überladen wie ASUS und GigaByte nur in den seltensten Fällen Einblicke in das Routing der Verbindungen ihrer kundenfangtauglichen AddOns.

Dann ist weniger oft mehr!

Wenn der X79 das geworden wäre, was Intel noch zur CES 2011 unterschwellig in Aussicht gestellt hatte, wäre dieser Chip eigentlich das geworden, was man von einem wirklichen Highend MCH für den echten Profieinsatz hätte erwarten können. Das DMI 3.0 mit seinen 4 PCIe 3.0 Lanes hätte das Gröbste abfangen können und bis auf USB 3.0 war ja eigentlich mit SAS 2.0 alles an Bord, was man braucht, um eine echte Workstation zu bauen, die nicht an irgendeiner latenten Verstopfung krankt. Aber nein, es kam ja anders, auch dieser Kater muste kastriert werden. Schnipp-Schnapp, Eier ab.

Tragt doch bitte Eure archaischen PCI Karten zu Grabe. Habe ich auch schweren Herzens getan. Hier liegt eine teure Soundkarte von MAudio. Nun unbrauchbar geworden, da kein PCI Steckplatz vorhanden. Aber so ist das nun mal. Jeder muß im Gefolge der Innovation auch ein Opfer bringen. Und mit etwas Weitblick wird man für die Zukunft eben etwas teurer und moderner einkaufen und nicht den Kinderkram fürs Kinderzimmer!

Addendum:

Was noch fehlt ist eine Beschreibung der Lane-Verteilung bei den Slost, die von der CPU bedient werden. Soweit ich weiß kann der PCIe Rootkomplex (der ja beim Sandy-Bridge-E erstmal nur auf PCIe 2.0 arbeiten wird) Diverse Knotenkonfigurationen bereitstellen, ohne daß ein zusätzlicher Switchbaustein nötig ist. Ich vermute, daß bei den Platinen mit mehr als zwei 16x PEGs der dritte Peg, wenn belegt, 8 Lanes von einem Nachbarn abgreift und den Nachbarn dann zu einem 8Lane Slot macht. Bei vier PEGs werden bei Bestückung dann wohl die vier je mit 8 Lanes versorgt.

Aber: SB-E hat ja 36 Lanes (abgezogen habe ich schon die 4 Lanes für das DMI). Vier 8-Lanes oder 2 16-Lanes PEG lassen 4 Lanes über. Ich sehe aber keinen physikalischen 8x oder 4x Slot, sondern nur 1x Slots. Wird MSI etwa die PCIe Lanes des MCH gar nicht nutzen und nur die Lanes der CPU verteilen?

Zuletzt bearbeitet: