S

Stuntmp02

Gast

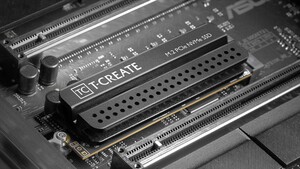

Ich habe ein Gigabyte X299 UD4 zusammen mit einer Samsung 960 Pro im Einsatz und bekomme hier leider nicht die Performance, die beispielsweise Computerbase mit einem viel billigeren Chipsatz Z170 auf Basis von Core i7 6700K bekommt. Vor allem die sequential read und sequential write Werte sind für die 960 Pro bei mir deutlich zu niedrig und scheinen eine Art Limit bei der Verwendung der Schnittstelle zu haben, die bei etwa 2,9GB/s liegt, anstatt der 3,5GB/s bei dem Computerbase Testsystem.

Folgende Einstellungen sind getätigt:

- Energiesparplan "High Performance" ausgewählt

- Spectre/Meltdown Patches sind deaktiviert

- BIOS Factory Reset gemacht

- Die PCIe Lanes des M.2 Slots teilen sich Bandbreite mit SATA 4,5,6,7 - alle genannten SATA-Ports sind im BIOS deaktiviert und nichts daran angeschlossen

- Läuft laut Samsung Magician mit PCIe Gen. 3 x 4

- Samsung NVMe Treiber ist installiert (Mit Windows Treiber sind die Ergebnisse noch schlechter)

- SSD Optimization von Windows 10 durchgeführt

- Windows 10 wurde frisch auf die neue SSD installiert, kein Klon oder sowas

Hat irgendjemand eine Idee, wie ich die volle Leistung der 960 Pro abrufen kann?

Folgende Einstellungen sind getätigt:

- Energiesparplan "High Performance" ausgewählt

- Spectre/Meltdown Patches sind deaktiviert

- BIOS Factory Reset gemacht

- Die PCIe Lanes des M.2 Slots teilen sich Bandbreite mit SATA 4,5,6,7 - alle genannten SATA-Ports sind im BIOS deaktiviert und nichts daran angeschlossen

- Läuft laut Samsung Magician mit PCIe Gen. 3 x 4

- Samsung NVMe Treiber ist installiert (Mit Windows Treiber sind die Ergebnisse noch schlechter)

- SSD Optimization von Windows 10 durchgeführt

- Windows 10 wurde frisch auf die neue SSD installiert, kein Klon oder sowas

Hat irgendjemand eine Idee, wie ich die volle Leistung der 960 Pro abrufen kann?