Angebliche Packaging-Probleme: Nvidia Rubin Ultra reizt CoWoS-L von TSMC aus

Seit Wochenbeginn wird spekuliert, ob Nvidias Rubin Ultra wirklich wie geplant Ende 2027 kommen wird. Laut aktuellen Gerüchten, die sich auf Analysten berufen, scheint es Probleme beim Packaging bei TSMC zu geben. Demnach ist das Produkt wohl zu groß und zu komplex und überreizt so das CoWoS-Design.

Nvidia bringt TSMCs CoWoS ans Limit

Seit 2021 bereits in Produktion, hat sich CoWoS (Chips on Wafer on Substrate) zum Kassenschlager entwickelt. Kein moderner größerer Chip ist ohne diese Technologie verfügbar. Von CoWoS-S verlagerte sich der Prozess zuletzt zu CoWoS-L, das noch größere Chips erlauben wird. Bei CoWoS-S war bei der 3,3-fachen Größe der theoretischen Einzelchips auf einem Interposer das Limit erreicht, bei CoWoS-L wird dies unter anderem durch den viel größeren Interposer von 120 × 150 mm aber auch zusätzliche integrierte Features wie Spannungsregler (FIVR, Fully Integrated Voltage Regulator) nun schon einmal auf bis zu 9,5-fache Reticle-Größe gestreckt.

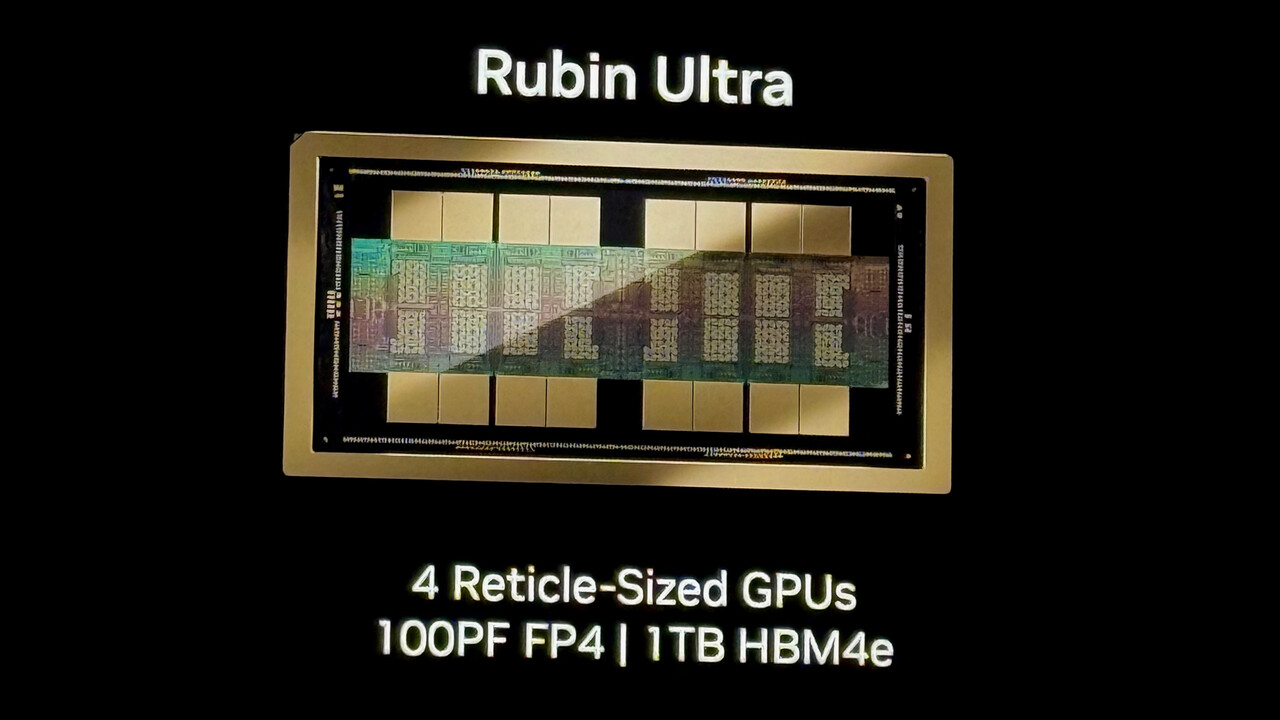

Als Reticle-Size-Limit in der Branche gilt die Maximalgröße eines einzelnen Chips, der mit gängigen Belichtungsmaschinen Kantenlängen von bis zu 26 × 33 mm bzw. 858 mm² haben kann. Im Jahr 2027 können so zusammengepackte Riesenchips erscheinen, die mindestens vier Chips flankiert von I/O und 12 HBM4E-Stacks beherbergen.

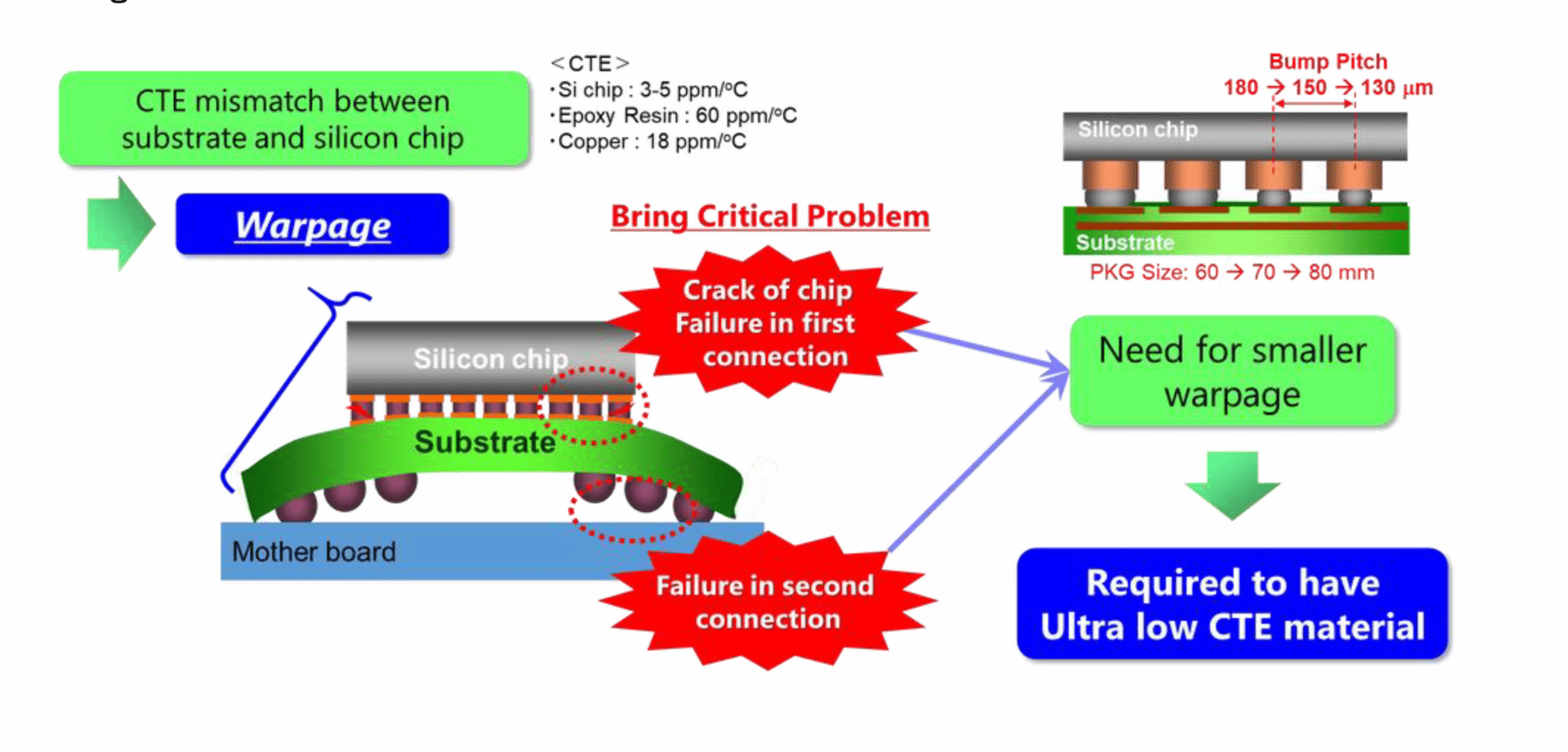

„Warpage“ bei Rubin Ultra

Die Rubin-Ausbaustufe Rubin Ultra setzt laut bisherigen Gerüchten genau auf so ein Design, während der Nachfolger Feynman erstmals Die-Stacking nutzen wird. Rubin Ultra mit seinen insgesamt 4 Dies nebst HBM4e wird zuvor das reguläre Packaging dabei wohl nahezu voll ausreizen, weshalb nun angeblich Probleme zum Vorschein kamen. So sei in ersten Testläufen vermehrt das sogenannte „Warpage“ aufgetreten, also Verformungen des am Ende zusammengesetzten Chip, der so mitunter nicht mehr wie gewollt oder gar nicht funktioniert.

Das Problem ist vor allem bei größeren Multi-Chip-Packages nicht neu, nun jedoch zurück. Der Ausweg scheint, dass Rubin Ultra auch auf einen 2-Die-Design basiert, das dann nur für die Maximalkonfiguration mit einem zweiten Chip kombiniert wird.

Interesting. It seems the reason there have been so many recent CoPoS rumors is that Rubin Ultra may have had a warpage issue in packaging.

— Jukan (@jukan05) March 31, 2026

Rubin Ultra’s warpage issue could accelerate the adoption of CoPoS. pic.twitter.com/eKlHixAwdB

Die andere Alternative sind neue Packaging-Methoden. Glas-Substrat ist viel weniger anfällig für Warpage – allerdings noch Jahre von einem großen Serieneinsatz entfernt. Aber auch der Einsatz von CoPoS, Chips on Panel on Substrate, könnte dem Sichverziehen teilweise entgegenwirken. Hier kamen zuletzt sehr viele Gerüchte über diese Packaging-Methode auf, und auch, dass TSMC sie wohl schnell umsetzen will.

Da diese Neuheiten aber wohl alle kaum rechtzeitig fertig werden, um mit Nvidias Roadmap einherzugehen, wird es wohl auf einen angepassten Chip für Rubin Ultra hinauslaufen. Wie genau dieser jedoch aussieht, bleibt ein Gerücht.

Here are some small notes about $NVDA Rubin Ultra:

— Aaron (@Arronwei3n) March 30, 2026

1. Conclusion: TSMC is indeed planning to manufacture a dual-die Rubin Ultra.

2. Original expectation: One substrate with two interposers; each interposer would carry two Rubin Ultra dies and eight HBM stacks.

3. Current… https://t.co/n3X22LpOkf pic.twitter.com/rUJkGg8Gtk