Intel Roadmap: Von 10- und 7-nm- bis zu 2,5D- und 3D-Chips

Zur International Solid-State Circuits Conference (ISSCC) wird Intel in mehreren Vorträgen kleine Einblicke in die eigene Entwicklung geben. Ein Roundtable wird sich unter anderem mit der Fertigungstechnik befassen, in der sich Intel weiterhin auf einem guten Weg zu 10 nm sieht, da die Fehler des Vorgängers vermieden werden.

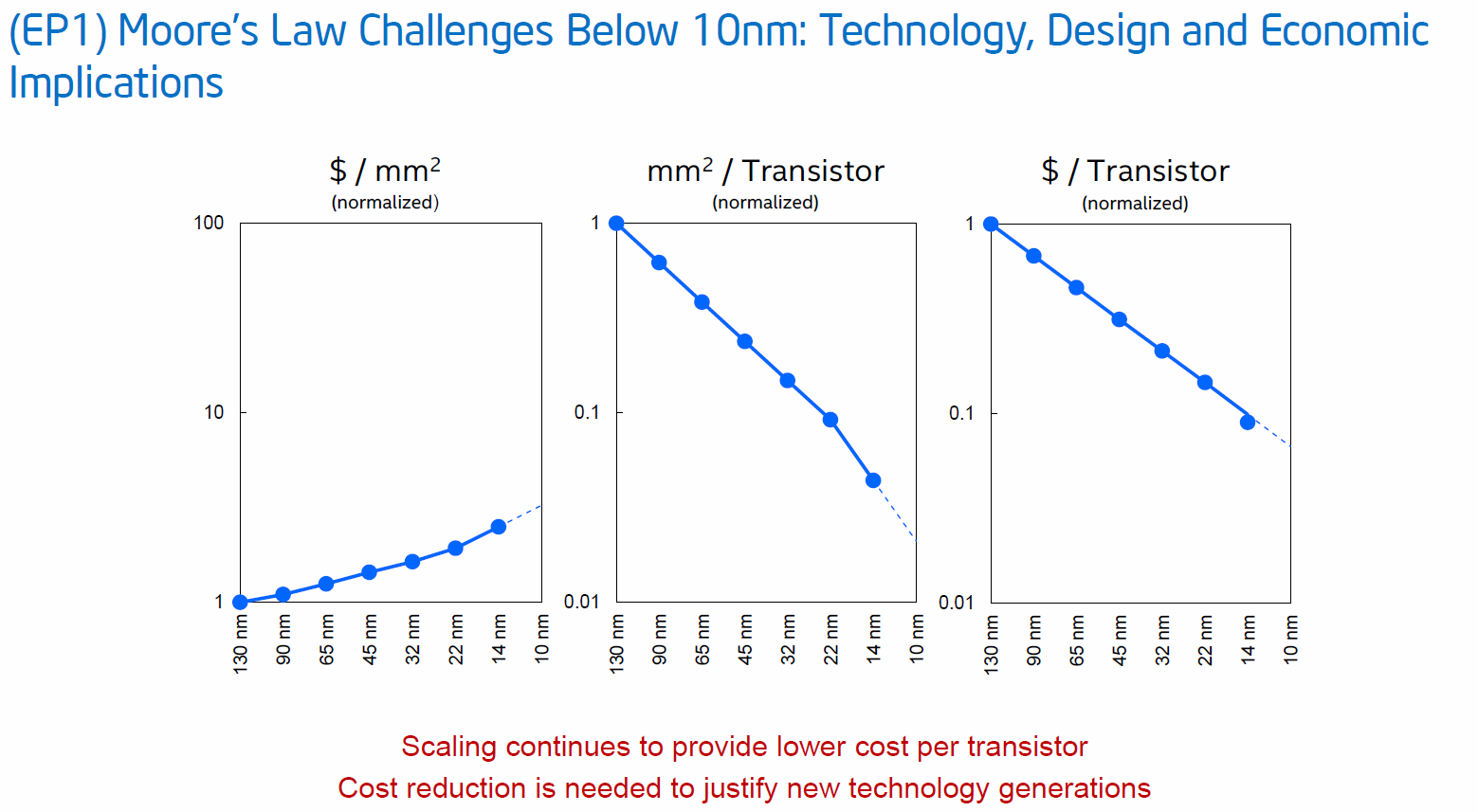

Mark Bohr, Intel Senior Fellow für das Logic Technology Development, gab in einen Webcast mit Journalisten in der letzten Woche preis, dass die Entwicklung bei 10-nm-Chips gut 50 Prozent schneller voranschreite als bei der deutlich verzögerten 14-nm-Fertigung. Diese Entwicklung hatte sich in den letzten Monaten bereits angedeutet. Bohr betonte dabei, dass die Zusammenarbeit zwischen Fertigern und Chip-Design-Teams in Zukunft noch wichtiger werde, um den größtmöglichen Nutzen aus einer neuen Fertigung ziehen zu können – dies war in der Vergangenheit auch bei Intel nicht immer der Fall, was zu Verzögerungen beim Start neuer Produkte führte. Leisten können sich die schnelle Entwicklung ohnehin kaum noch eine Handvoll Firmen, auch wenn die entsprechende, immer kleiner werdende Skalierung, am Ende große Vorteile verspricht. Doch zuvor müssen Milliarden in Forschung und Entwicklung investiert werden.

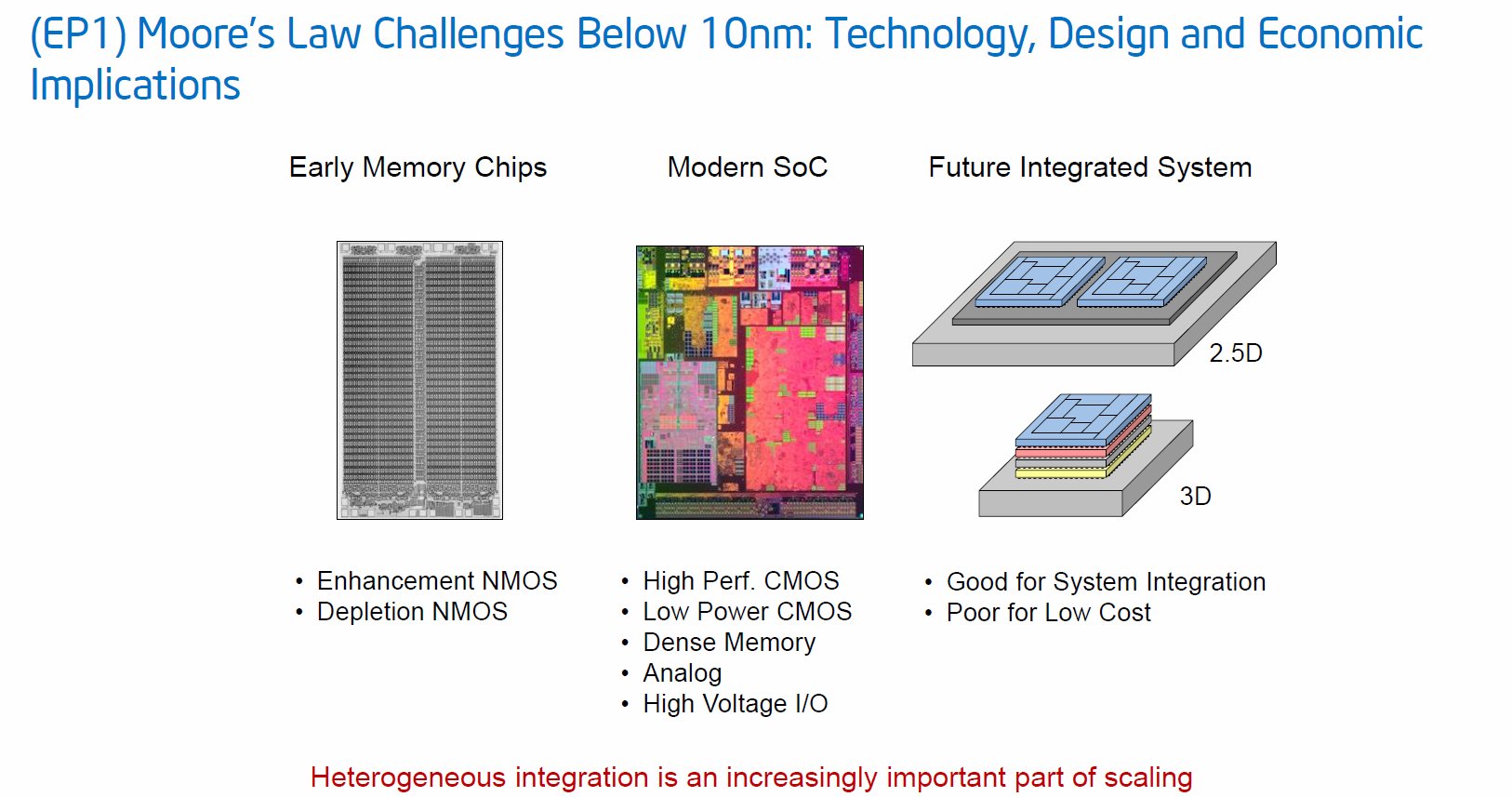

Die Zukunft liegt deshalb nicht allein bei klassischen Chips oder SoC-Designs. Sogenannte 2,5D-Produkte versprechen dank Nutzung von nur einem Package mit mehreren Chips, wie beispielsweise CPU/GPU und Speicher – Stichwort Intel Knights Landing oder AMD Fiji – eine sehr hohe Leistung, während reine 3D-Chips eher für Low-Power-Designs geeignet sind. Beide Technologien sind bereits marktreif, aber im Vergleich zur klassischen Bauweise sehr teuer, weshalb die Einführung zögerlich erfolgt. Mit Anpassungen in der Fertigung wird beiden Lösungen für die Zukunft jedoch deutlich mehr Gewicht zukommen.

Die Fertigungstechnologien waren in den letzten Wochen und Monaten oft Gesprächsstoff, da jeder der großen Hersteller seine Technologie im Vorteil sieht. Nach Samsungs Ankündigung der 14-nm-Smartphone-Chips hat Intel in dieser Woche noch einmal Öl ins Feuer gegossen. Die eigentlich nicht für Medien sondern Analysten bestimmte Präsentation wurde prompt im Internet veröffentlicht.

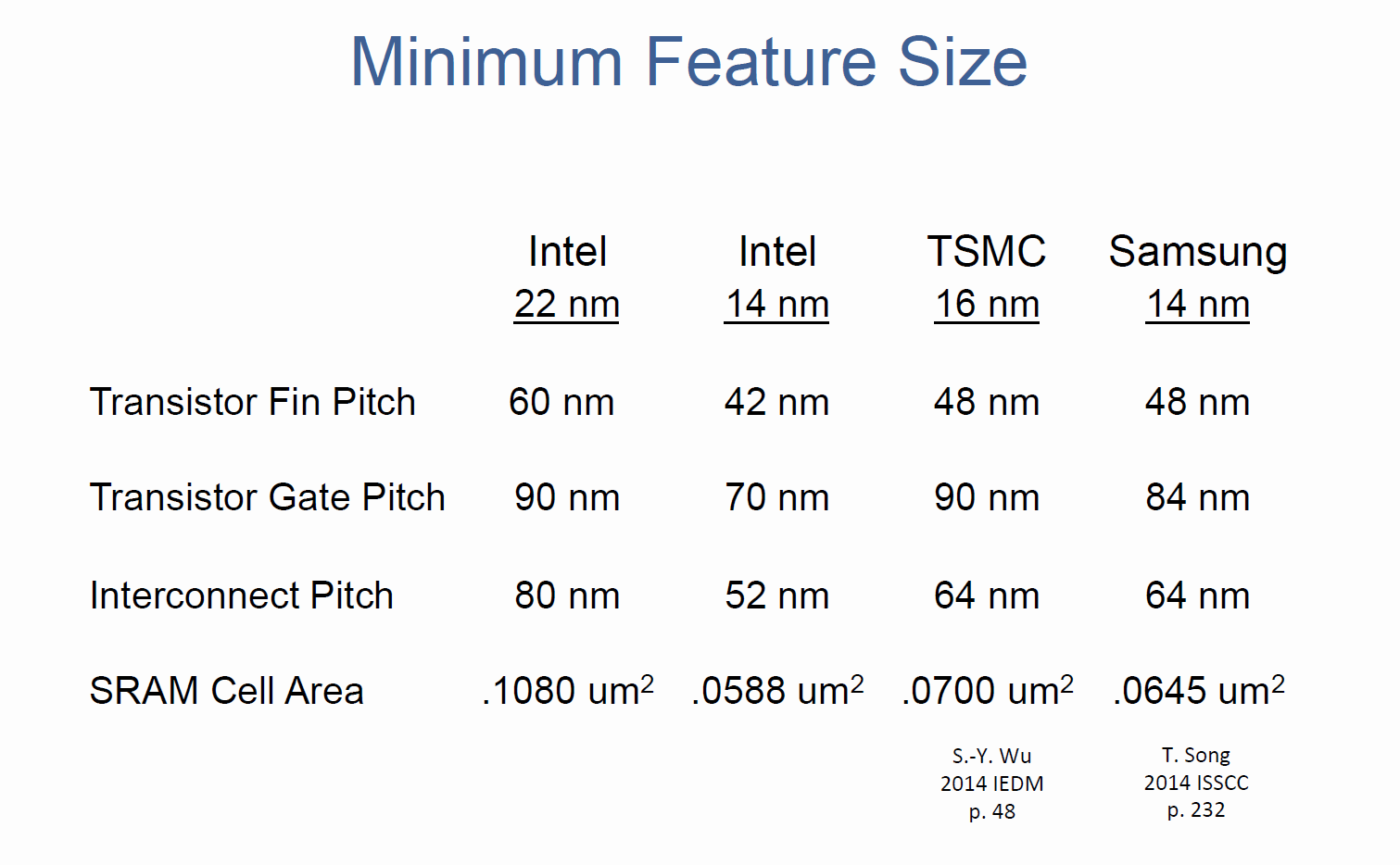

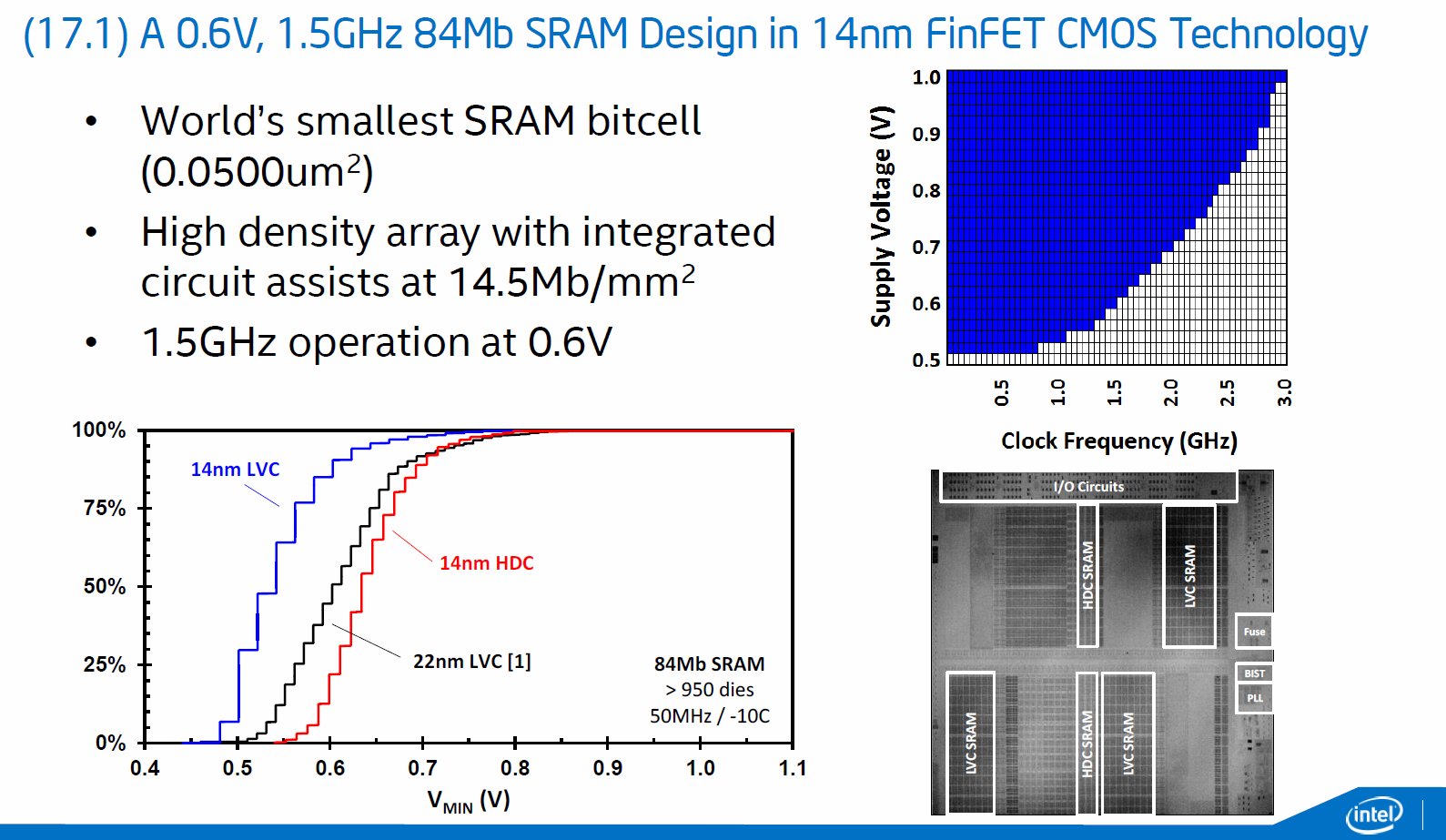

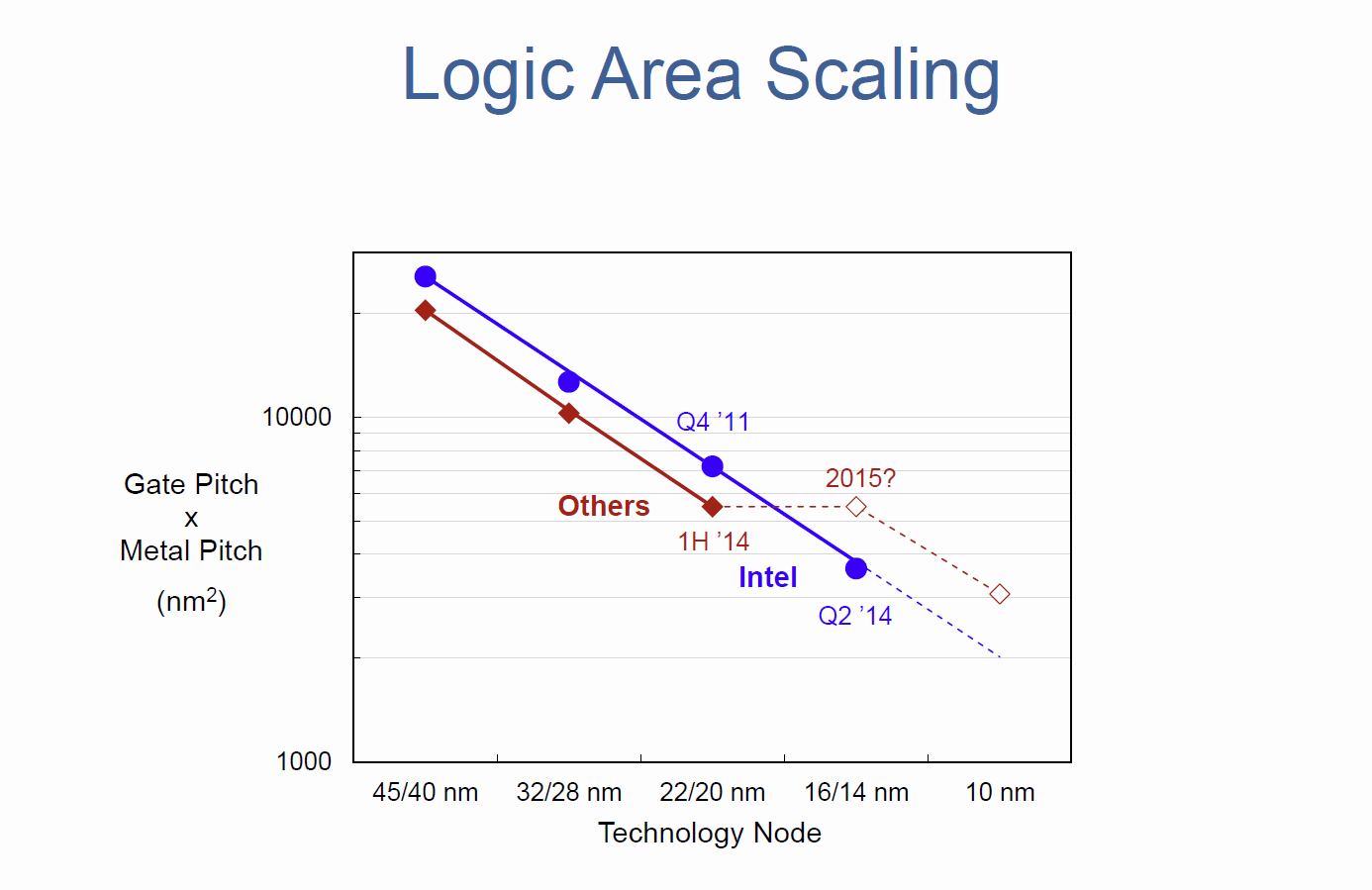

Der Vergleich soll zeigen, dass Intels 14-nm-Fertigung die derzeit beste ist, da die Konkurrenten in allen Bereichen schlechter aufgestellt sind. Diese Folie zeigt erneut auch, dass die Bezeichnungen der Firmen für ihre Fertigung nur noch Makulatur sind und dem vorbestimmten Schema folgen. Dieses, seit einigen Jahren genutzte Vorgehen, hatte Intel bereits im letzten Sommer gegenüber ComputerBase bestätigt. Wirklich Verlass ist auf derartige Folien eines Herstellers zudem ohnehin nicht, da die Informationen keinerlei Weiterentwicklungen berücksichtigen – ein Grund, warum Intel diese nicht an die Medien geben wollte. Denn es ist auch Intel selbst, das neueste Entwicklungen vermissen lässt: die Fläche der SRAM-Cell wurde noch einmal verkleinert, von 0,0588 auf 0,05 µm². Die SRAM-Cell ist jedoch eine der unwichtigsten Indikatoren in der Fertigung und deshalb für den gesamten Fertigungsprozess mit Milliarden an Transistoren für einen komplexen Chip kaum noch aussagekräftig.

Intels Bestrebungen und Vergleiche mit der Konkurrenz in dem Bereich kommen nicht von ungefähr. Früher undenkbar, will sich Intel mehr und mehr als Foundry, also als Auftragsfertiger, im Markt positionieren. Bohr betonte bereits letzten Sommer, dass mit der in seinen Augen besten Fertigung natürlich auch Geld verdient werden soll. Denn während die Mitbewerber erst jetzt den Schritt zu FinFET gehen, hat Intel einen bisherigen Scaling-Rückstand in eine Führung umgewandelt. Samsungs und TSMCs 14/16-nm-Fertigung basiert zum großen Teil noch auf 20 nm zuzüglich neuer FinFETs. SemiWikis Analysen hatten bereits im letzten Jahr gezeigt, dass sich der Gate- und Metal-Pitch bei TSMC und Samsung/Globalfoundries gegenüber der 20-nm-Fertigung teilweise sogar verschlechtere, weshalb die daraus resultierende Flächengröße im besten Fall gleich bleibt bzw. nur minimal kleiner wird. Erst bei der als 10 nm bezeichneten Fertigung soll diese wieder schrumpfen, nach bisherigen Informationen wird aber auch dort Intel die Führung behaupten können.

Was bei 7 nm passiert, ist offen. Große Know-How-Lieferanten in dem Bereich wie Synopsys, bei denen Intel mit über zehn Prozent vom Gesamtumsatz der größte Kunde ist, sind aktuell noch in der Forschung und Entwicklung der entsprechenden Werkzeuge, sowohl für die 7- als auch bereits die 5-nm-Fertigung, wie der Konzern in dieser Woche bestätigte. Intel betonte dazu noch einmal, dass die 7-nm-Fertigung auch ohne die EUV-Lithografie möglich sein wird. Diese mache zwar Fortschritte, wie ASML zeigt, jedoch nicht schnell genug, sodass Alternativen in Betracht gezogen werden müssen. TSMC setzt mit multiplen Bestellungen von EUV-Ausrüstung bei ASML ein klares Zeichen in diese Richtung und will als einer der ersten von den positiven Effekten profitieren. Doch wann genau diese eintreten werden, ist nach unzähligen Verschiebungen in den letzten 10 Jahren auch heute ungewiss. Zuletzt war von einer Serienproduktion ab Ende 2016 die Rede, aber auch nur in ersten, ausgewählten Bereichen.