Skylake-SP: Der Ringbus ist tot, es lebe das Mesh

Die ersten Die-Shots der neuen Skylake-High-End-Prozessoren ließen es schon erahnen, jetzt macht Intel es offiziell: Der mit Nehalem eingeführte Ringbus-Interconnect ist Geschichte. Kerne, Cache oder System Agent sind jetzt über ein so genanntes Mesh-Netzwerk verknüpft, wie es Intel bereits bei Knights Landing eingeführt hatte.

Der Ringbus ist nach neun Jahren am Limit/Ende

Der Ringbus als Interconnect wurde anno 2008 mit der Nehalem-Architektur eingeführt, wurde bei Westmere-EX schon in doppelter Form und optimierter genutzt, spätestens seit Sandy Bridge Anfang 2011 war er dann überall im Einsatz. Seine Aufgabe war immer, interne Bauteile miteinander kommunizieren zu lassen. Doch mittlerweile ist diese Lösung in die Jahre gekommen – und gerade im Server-Segment an einigen Stellen am oder bereits über dem Limit angelangt.

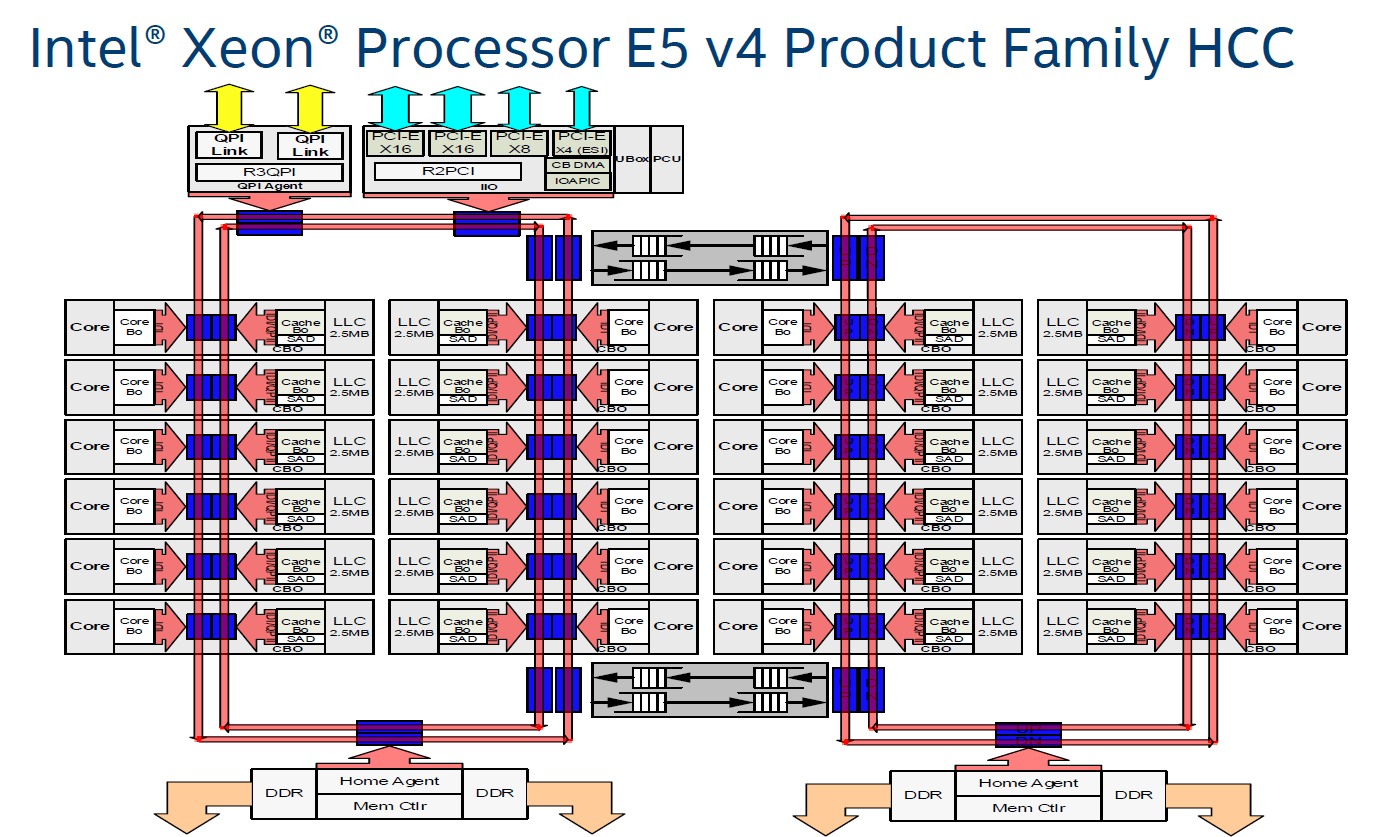

Denn was als einzelner Ring für Notebook- und Desktop-CPUs startete, war bereits auf drei Ringe mit Ivy Bridge-EP und später vier bidirektionale Ringe bei Broadwell-EP ausgebaut worden. Doch in den immer größeren Prozessoren wurde die Wegstrecke vom „letzten“ bis zum ersten Kern über zwei Ringe und einen Buffer-Switch immer größer, Latenzen stiegen deutlich an, Worst-Case-Szenarien führten zu geringerer Leistung.

Ein Mesh übernimmt die Kommunikation aller Teile in der CPU

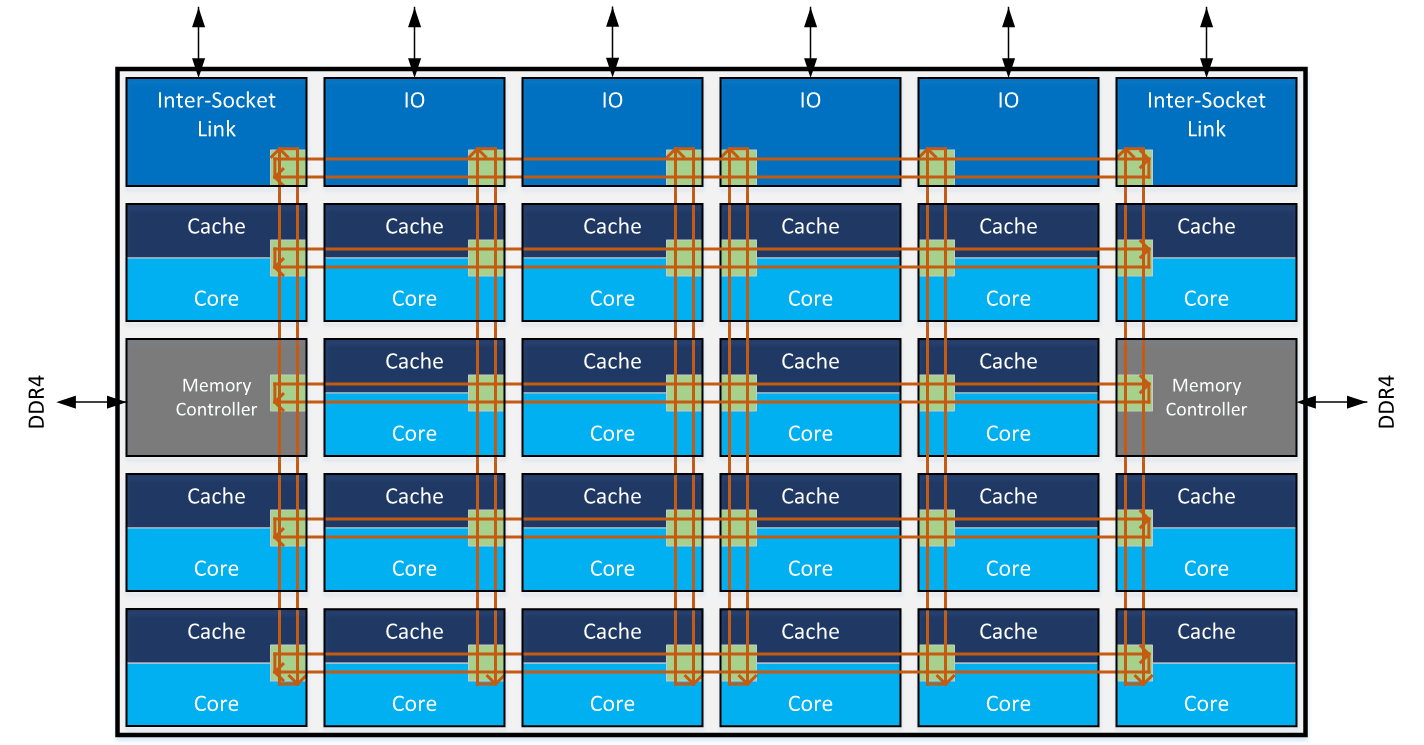

Im Rahmen eines Server-Workshops in Hillsboro, Oregon, hat Intel weitere Details zu den neuen Prozessoren verraten. Das Netzwerk aus Doppelkreuzen (Mesh, #) als Nachfolger des Ringbuses soll sehr niedrige Latenzen und eine hohe Bandbreite bieten, während es Prozessorkerne, Caches, die Speichercontroller und die I/O-Komponenten miteinander verbindet. Die kürzeren weil oftmals direkten Wege, die zudem vielfältiger ausfallen und über Kreuzungen jederzeit die Richtung ändern können, eliminieren viele der mit dem Ringbus in der letzten Ausbaustufe aufgetauchten Probleme. Jeder Knoten im Netzwerk ist für die Kommunikation im Netzwerk verantwortlich, es gibt keine Sackgassen.

So kann das Netzwerk mit einer niedrigeren Taktrate und Spannung arbeiten und ist trotzdem am Ende bei geringerer Latenz noch deutlich leistungsstärker und effizienter, erklärte Intel als Ausblick auf die neuen Serverprozessoren. Auch hilft es bei der Skalierbarkeit zu noch mehr Prozessorkernen ohne in große Strafzeiten bei der Latenz zu verfallen – die genaue Anzahl wird heute noch nicht offiziell verraten, Gerüchte sprachen zuletzt stets von bis zu 28 Kernen für die CPU.

Mit größer werdenden Caches ist das Mesh-Netzwerk ebenfalls dem Ringbus überlegen, erläuterte der Chef-Architekt der neuen Server-CPU, da schneller über kürzere Wege an die Daten gelangt werden kann, selbst an die, die nicht direkt am Kern anliegen. Dies hilft dabei, unter anderem den Last Level Cache (L3) auch als eigentlich verstreute Lösung über den kompletten Die am Ende als Unified-Lösung ansprechen zu können. Dies wiederum hat weitere Auswirkungen für den Zugriff auf den Speichercontroller und das I/O-Interface, wenn Daten aus diesem zugezogen werden müssen. Em Ende verspricht Intel in gewissen Szenarien massive Leistungsgewinne gegenüber dem Vorgänger – wie viel genau, darf heute aber ebenfalls noch nicht verraten werden. Diese sowie alle weiteren Informationen zu den Skylake-SP alias Xeon SP stehen derzeit noch unter NDA und werden in Kürze in einem Bericht folgen.

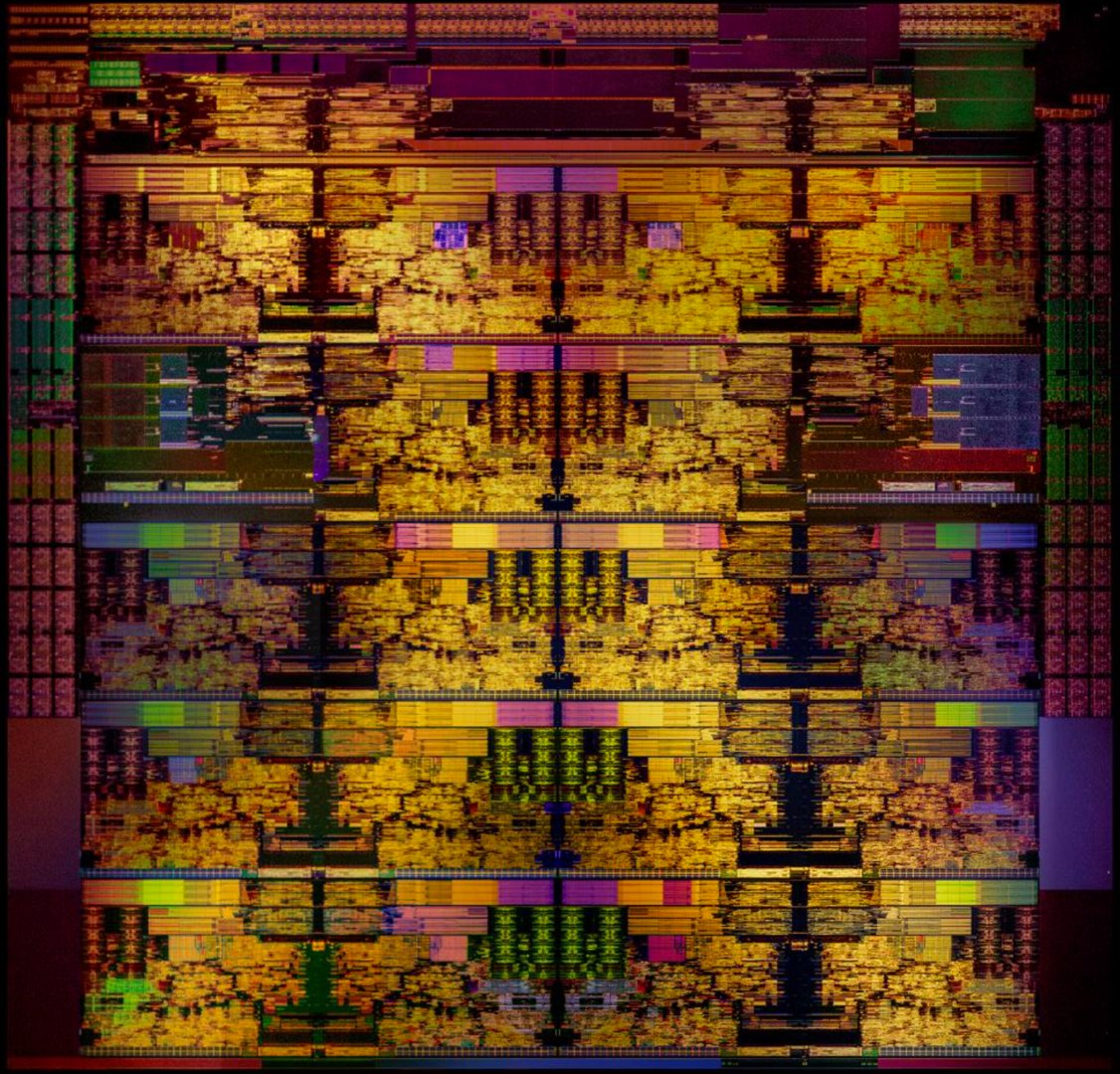

So sieht das in „echt“ aus

Ein Blick in das bereits vor zwei Wochen bereitgestellte (aber ebenfalls bearbeitete) und um 90 Grad gedrehte Bild des Die des 18-Kern-Prozessors zeigt mit dem Zusatz an neuen Informationen nun, wie die Implementierung von Mesh in „echt“ aussehen wird. Klar zu erkennen sind jetzt die Speichercontroller an den beiden Seiten, jeweils drei an der Zahl – dies entspricht den Gerüchten über das Sechs-Kanal-Speicherinterface. PCI Express ist ebenfalls ganz klar an der oberen Kante auszumachen.

Die CPU-Kerne sind ebenso wie die angeflanschten Cache-Slices auszumachen. Während die erste, dritte, vierte und fünfte Reihe (v.o.n.u.) je vier Kerne enthalten, sind es zwischen den beiden Speichercontrollern in der zweiten Reihe von oben noch zwei Kerne – summa summarum 18 Kerne.

Wie die Skalierbarkeit zu Modellen mit weniger oder mehr Prozessorkernen dann aussehen wird, lässt sich bereits erahnen: Eine oder zwei Reihen/Spalten weniger oder mehr, schon ist ein Low-Core-Count-Die oder der High-End-Ableger geschaffen. Ein Bild von exakt diesem 28-Kern-Die hatte Intel bereits vor Ende März veröffentlicht, doch auch dieser wird erst jetzt mit den neuen Informationen klarer lesbar. Bereits damals deutete sich jedoch eine massive Änderung zu bisherigen Server-CPUs an.