TSMC: 3D-Packaging ist das nächste große Ding

3D-Packaging ist nicht erst seit AMDs Ankündigung von gestapeltem L3-Cache auf neuen Ryzen-Prozessoren noch in diesem Jahr auf den Roadmaps der Foundrys. Denn während das Zweidimensionale schnell an Limits stößt, geht in der dritten Dimension noch einiges mehr – und als Kombination aus beidem richtig viel.

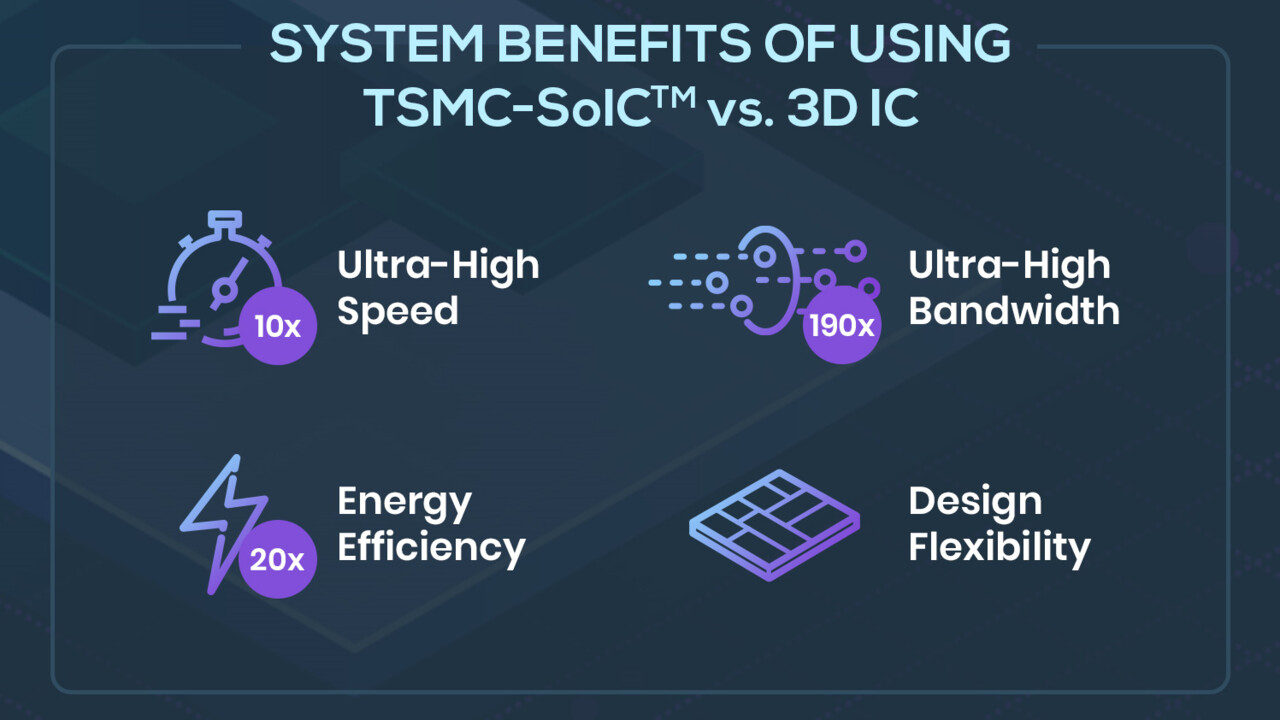

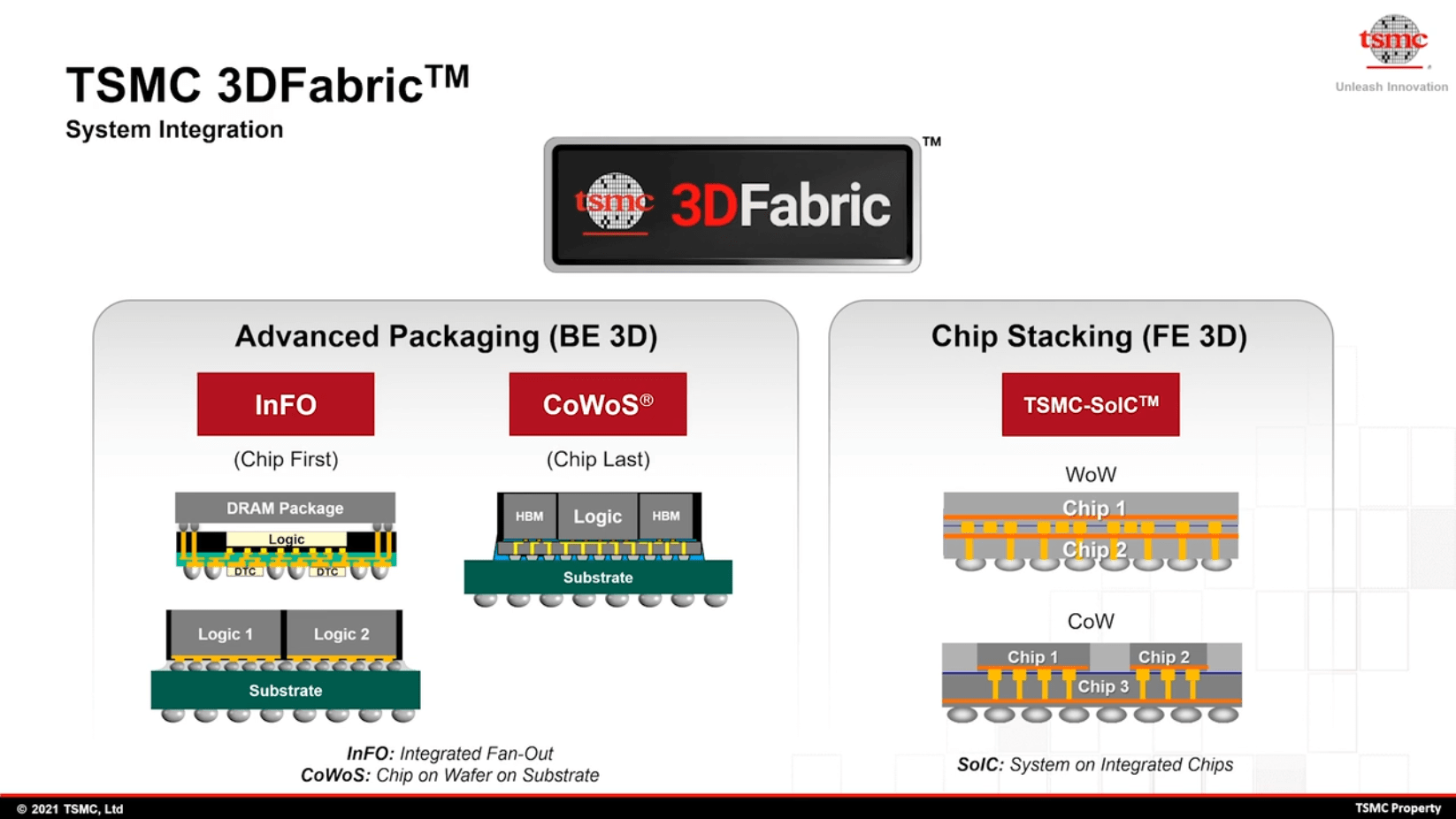

TSMC-SoIC (System on Integrated Chips) heißt die Technik hinter AMDs Prototyp. Sie markiert den letzten Meilenstein, der aus ersten Gehversuchen mit Multi-Chip-Modulen über Lösungen mit Interposern und weiteren Erfahrungswerten wie beispielsweise DRAM gestapelt über Smartphone-SoCs entstanden ist. All diese Technologien gibt es auch weiterhin und auch sie werden noch optimiert, aber SoIC ist das aktuell fortschrittlichste Produkt.

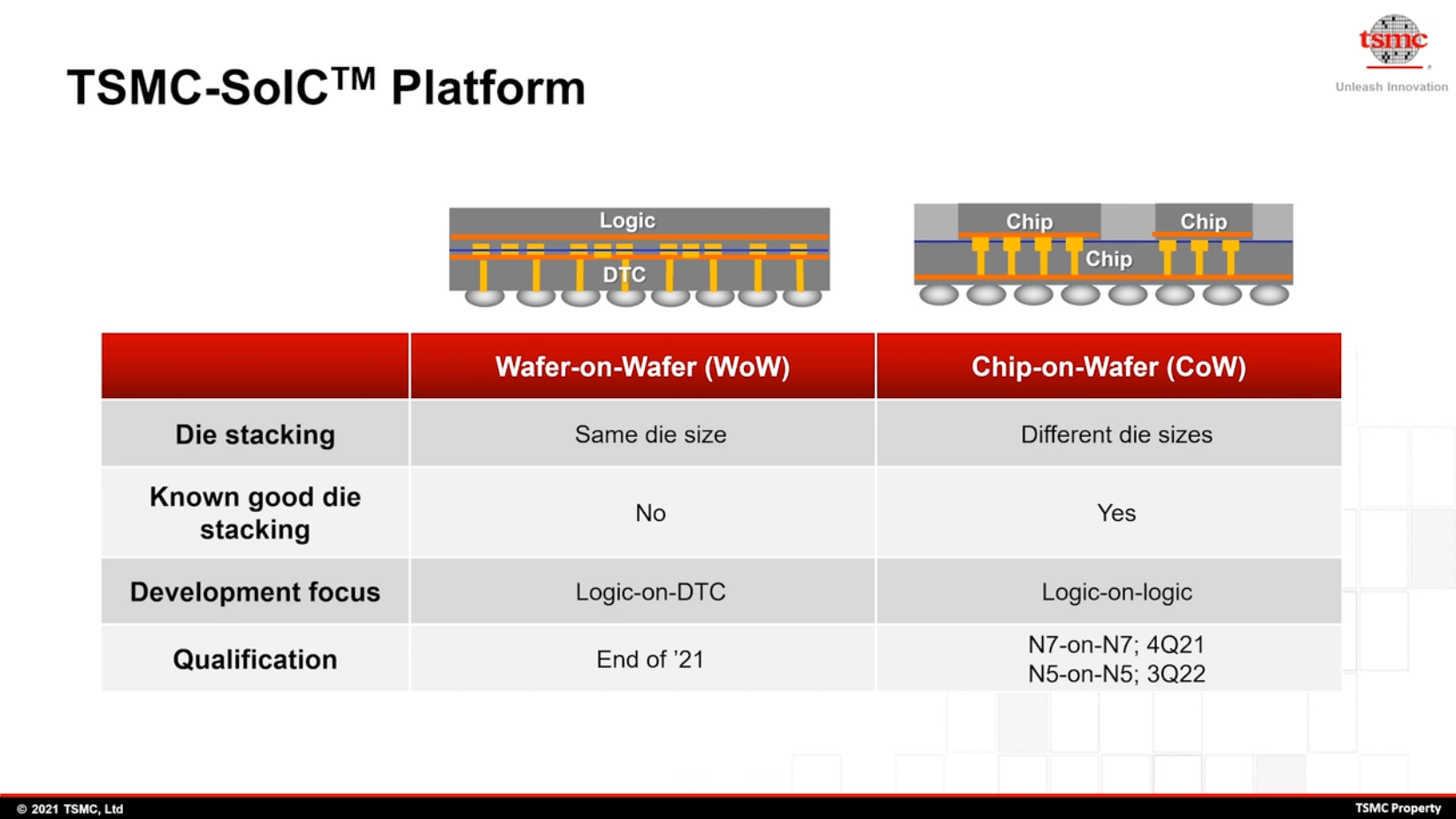

TSMC unterscheidet beim neuen Chip-Stacking zwischen zwei Varianten: Wafer on Wafer und Chip on Wafer – AMD folgt der zweiten Lösung. Sie erlaubt es, unterschiedlich große Dies zu stapeln, im Fall von AMD ein 81 mm² CPU-Die als Basischip, auf den ein 36 mm² Cache-Die gesetzt wird.

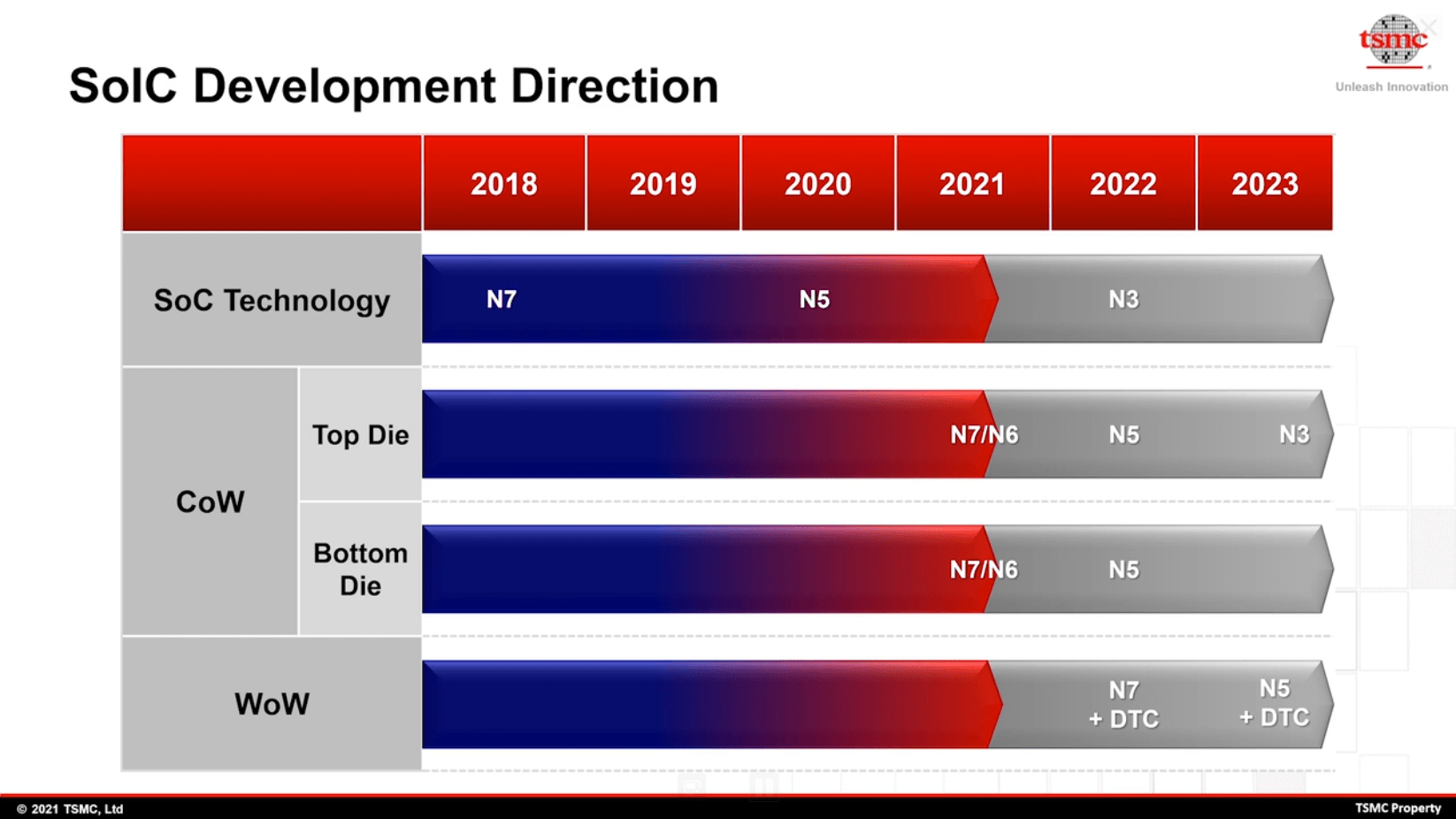

Warum AMD erst Ende des Jahres damit fertig wird, erklärt TSMC auch: Sie werden erst im vierten Quartal dieses Jahres mit der Technologie bereit zur Serienproduktion sein. Und dass es dabei keinen moderneren Fertigungsschritt als 7 nm geben wird, macht TSMC auch klar, denn bisher wurde nur damit gearbeitet und dieser wird zu Beginn als einziges qualifiziert sein. Binnen eines knappen Jahres soll dann jedoch eine Lösung für N5-on-N5 zur Verfügung stehen: Q3/2022 könnte zufällig genau passend für AMD Zen 4 sein.

Die Roadmap für den Bereich zeigt, dass TSMC noch schneller werden will und entsprechend viel vor hat. Ab der 3-nm-Fertigung soll das Stacking nur noch gut ein Jahr hinter reinen Logic-Lösungen hinterherlaufen, was für viele Partner ein entscheidendes Kriterium sein dürfte. Bereits heute sind zumeist HPC-Lösungen als primäre Kundschaft dafür gar nicht die Nutzer der ersten Stunde der State-of-the-Art-Fertigung, die an kleine SoCs für Smartphones geht, sondern folgen erst im Jahr darauf oder noch später. Sie wären dann perfekte Nutznießer. 2023/2024 könnte ein gestapelter High-Performance-Chip, bestehend nur aus 3-nm-Chips, zur Verfügung stehen.

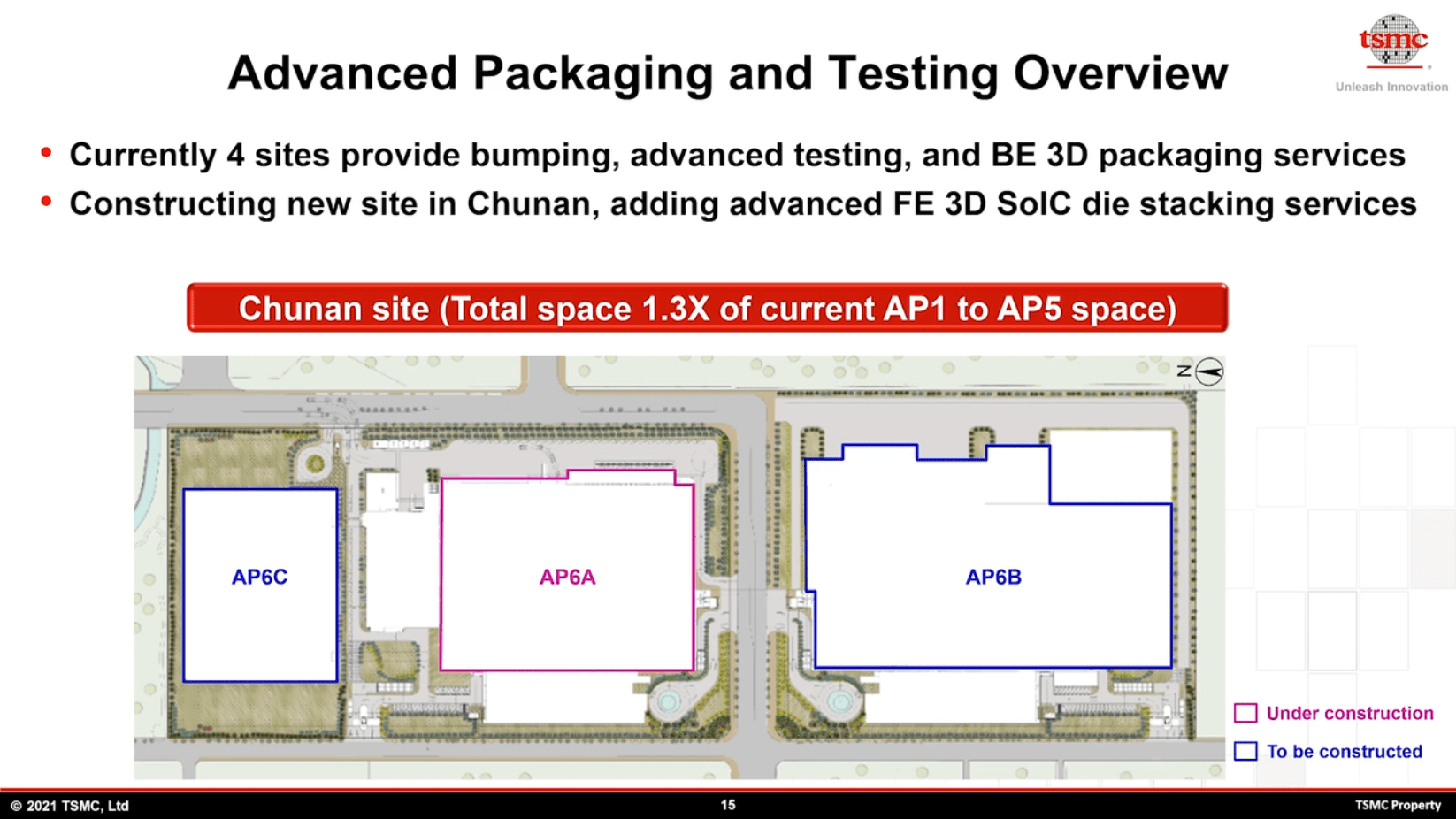

Um der Kundschaft auch genügend fertig gestapelte Chips anbieten zu können, baut TSMC gerade eine neue riesige Fabrik, die primär für dieses Stacking ausgelegt ist. AP6 heißt der Komplex und soll in drei Phasen mehr Platz bieten, als alle bisherigen TSMC-Package/Backend-Zentren zusammen.