- Registriert

- Juni 2001

- Beiträge

- 19.925

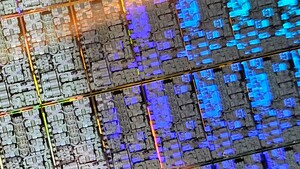

3D-Packaging ist nicht erst seit AMDs Ankündigung von gestapeltem L3-Cache auf neuen Ryzen-Prozessoren noch in diesem Jahr auf den Roadmaps der Foundrys. Denn während das Zweidimensionale schnell an Limits stößt, geht in der dritten Dimension noch einiges mehr – und als Kombination aus beidem richtig viel.

Zur News: TSMC: 3D-Packaging ist das nächste große Ding

Zur News: TSMC: 3D-Packaging ist das nächste große Ding