Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Notiz AMD Epyc 7004: Embedded-Roadmap bestätigt über 64 Kerne für Genoa

- Ersteller MichaG

- Erstellt am

- Zur Notiz: AMD Epyc 7004: Embedded-Roadmap bestätigt über 64 Kerne für Genoa

icemanspirit

Ensign

- Registriert

- Aug. 2019

- Beiträge

- 169

Tada100 schrieb:Hans zu Anton " ...Ich brauche so um die 96e Kerne für meine Simulation,

Mega viele PCI-E Lanes für meine Exabyte an Daten, sonst läufst nicht rund ..."

Anton " Und wovon träumst du nachts"

(...)

Du meinst diesen Anton hier?

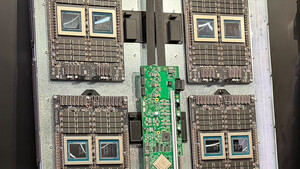

"The Anton 3 ASIC: a Fire-Breathing Monster for Molecular Dynamics Simulations", i.e. DE Shaw Research's eigenen Chip fuer Molekulardynamik? Der ist naemlich gar nicht so weit weg von Deinen Traeumen oben wie man denkt. Ist aber natuerlich keine general-purpose CPU

Zuletzt bearbeitet:

(Anpassung Laenge von Zitat)

YforU

Captain

- Registriert

- März 2001

- Beiträge

- 3.499

Richy1981 schrieb:Und selbst wenn das am Ende 320Watt zur Folge hat, ist das unterm Strich immer noch viel weniger Abwärme, als vor ein paar Jahren von 2 x 8 Kernen

Das täuscht. Selbst CPU Serien wie der E5-2667v2 /v3/v4 (8C/16T mit einem Basistakt von 3,2Ghz+) liegen bei 135-140W TDP.

Die gehen heute in refurbished Servern immer noch weg wie warme Semmeln. 2x8C mit hoher Taktfrequenz und ordentlich Arbeitsspeicher reicht für vieles und ist lizenztechnisch kostengünstig. Je nach Ausstattung (RAM, Storage, NICs) zieht beispielsweise ein HPE DL380 G9 mit ein paar VMs im Leerlauf 120-180W gesamt.

@pmkrefeld naja wenn man bedenkt dass es die 8C16T CPUs auch als U Variante mit 15W gibt passt das ganze auch so.

Der IO Die trägt bei der Rechnung in so einer CPU definitiv dazu bei dass in der Realität sogar weniger als die 3,3W Pro kern bleiben.

IO in 7 nm und die Chiplets in 5nm ist abzusehen. Dennoch kann man bei dieser CPU sicherlich 70W für den IO Die abziehen.

Deshalb ist die 5nm Effizienz trotz der Zuwächse bei der Geschwindigkeit gegeben wenn man bedenkt was für die 96 Kerne und all die Threads dann noch übrig bleibt

Der IO Die trägt bei der Rechnung in so einer CPU definitiv dazu bei dass in der Realität sogar weniger als die 3,3W Pro kern bleiben.

IO in 7 nm und die Chiplets in 5nm ist abzusehen. Dennoch kann man bei dieser CPU sicherlich 70W für den IO Die abziehen.

Deshalb ist die 5nm Effizienz trotz der Zuwächse bei der Geschwindigkeit gegeben wenn man bedenkt was für die 96 Kerne und all die Threads dann noch übrig bleibt

Ist doch nur ein Mockup. Ein bisschen Photoshop auf Basis von Rome oder Milan.Colindo schrieb:Wieso sehen die Chiplets in den beiden Grafiken denn gleich groß aus? Eins ist doch in N7 gefertigt, das andere in N5?

Ergänzung ()

Ohne die Taktraten zu kennen kann reichen die Möglichkeiten von mega effizient bis Säufer ohne Ende.ChrFr schrieb:50% mehr Kerne / Threads, 12 DD5 Speicherkanäle und 128 PCIe 5.0 Lanes und das mit NUR 40 Watt mehr, wenn sich das bewahrheitet, wäre das richtig krass. Gut die 5nm Fertigung wird den pro Core Verbrauch vermutlich gut senken. Dennoch, wenn die 40 Watt auch nur annähernd stimmen, würde die Effienz nochmal einen gewaltigen Sprung machen.

Aber TSMCs 5 nm kennen wir ja schon von Apple und Huawei. Der ist schon nochmal gut effizienter.

- Registriert

- Feb. 2012

- Beiträge

- 9.499

pmkrefeld schrieb:320 / 96 = 3.33 W/Kern

Bei einem 8 Kerner wären das gerade Mal 26.66 W.

Ist ja nichts ungewöhnliches. Bei den Notebook Chips gibts auch 15 Watt Versionen. Mit wenig Spannung und Takt sind die CPUs recht effizient. Erst die hohen Taktraten und damit verbundenen Spannungen sorgen für die relativ hohen Leistungsaufnahmen z.B. auf dem Desktop. Aber wenn man möchte, kann man jeden aktuellen Ryzen auch damit betrieben.

- Registriert

- Jan. 2018

- Beiträge

- 768

seufztTada100 schrieb:Anton seufts

https://www.duden.de/rechtschreibung/seufzen

Normalerweise hänge ich mich eher selten an der Rechtsschreibung auf, aber manche Sachen werden so oft falsch gemacht/falsch verwendet..... da kann ich dann nicht widerstehen

Mehr kerne auf einem Die bedeutet auch, dass die Kommunikation untereinander und zum IF komplexer wird. Das heißt, man braucht entweder mehr Strom und Transistoren, oder man schluckt die bittere Pille und erhöht die Latenz. Da Zen sowieso unter der erhöhten Latenz vom Infinity Fabric leidet, vermute ich eher, dass die Transistoren für noch mehr Cache draufgehen. Das wäre zumindest eine Erklärung für das längere und schmalere Format der Chips im Bild.jube schrieb:Schade, dass die 5nm Fertigung nicht genutzt werden kann, um mehr Kerne auf einem Die unterzubringen. Trotzdem wow!

Jetzt wo AMD bei den Marktanteilen im Serverbereich bald zweistellig wird, würde es sich da nicht lohnen zwei I/O-Dies zu machen? Eines mit nur maximal 8 DDR5-Kanällen und eins mit maximal 12 Kanällen? So ein 32-Kerner braucht ja eh keine 12 RAM-Kanälle... und die Threadripper werden gar nur mit 4 Kanällen betrieben, da müsste man ja mehr als die Hälfte des I/O-Chips deaktivieren.

@Innz

Intra-Die wird es nur komplizierter wenn alle cores in einem ccx sind. Was zugegeben wohl die Intention des Vorposters war, sonst hat man ja nicht viel davon.

IF Anbindung wird nicht wirklich komplizierter. Wird halt aufwändiger je mehr Kerne angebunden werden wollen. Ob auf einem oder mehreren Dies ist da weniger relevant. Was meinst du mit längere und schmalere Format? Gibt doch noch gar kein Bild vom Die oder?

@Convert

Das habe ich mir auch schon gedacht. AMD braucht irgendwie eine Plattform zwischen "AM5" und full size. Die meisten Server haben keine 64 Kerne verbaut und brauchen auch nicht zwingend das Maximum an Speicher.

Ich würde sogar bis 6 oder gar 4 Kanäle runter gehen und dann für maximal 4-8 Dies.

Ist die Frage ob das so viel bringt. Man braucht dann auch die passende Stückzahl.

Aber 16-32 Kerner wo dann so ein fetter IO-Die verbaut wird ist dann sicher nicht gerade Kosteneffizient.

Intra-Die wird es nur komplizierter wenn alle cores in einem ccx sind. Was zugegeben wohl die Intention des Vorposters war, sonst hat man ja nicht viel davon.

IF Anbindung wird nicht wirklich komplizierter. Wird halt aufwändiger je mehr Kerne angebunden werden wollen. Ob auf einem oder mehreren Dies ist da weniger relevant. Was meinst du mit längere und schmalere Format? Gibt doch noch gar kein Bild vom Die oder?

@Convert

Das habe ich mir auch schon gedacht. AMD braucht irgendwie eine Plattform zwischen "AM5" und full size. Die meisten Server haben keine 64 Kerne verbaut und brauchen auch nicht zwingend das Maximum an Speicher.

Ich würde sogar bis 6 oder gar 4 Kanäle runter gehen und dann für maximal 4-8 Dies.

Ist die Frage ob das so viel bringt. Man braucht dann auch die passende Stückzahl.

Aber 16-32 Kerner wo dann so ein fetter IO-Die verbaut wird ist dann sicher nicht gerade Kosteneffizient.

@bensen könnte mir aber auch vorstellen dass sie trotzdem immer das große package nehmen. AMD ist nicht gerade dafür bekannt zig verschiedene Sachen auf den Markt zu werfen.

Es gibt sicherlich wieder 8 Kerner und trotzdem volles IO und alle RAM Kanäle.

Ob sie jetzt aber auch noch eine Abstufung bauen bzw Milan einfach weiter läuft für die kleineren EPYCs ist noch nicht raus.

So wie sie bisher vorgegangen sind könnte ich mir vorstellen dass sie einfach Milan auf altem Sockel weiterlaufen lassen fürs untere Ende (evtl dann mit Zen 4 Chiplets falls das irgendwie geht) und der Rest geht mit minimal 12 Kernen auf maximal 12 Chiplets weiterhin ganz nach oben mir dem Maximum an RAM und IO.

Zwischenlösungen mit weniger Chiplets sehen wir sicher auch bei genoa, dann aber ohne Einschränkungen beim IO und RAM

Es gibt sicherlich wieder 8 Kerner und trotzdem volles IO und alle RAM Kanäle.

Ob sie jetzt aber auch noch eine Abstufung bauen bzw Milan einfach weiter läuft für die kleineren EPYCs ist noch nicht raus.

So wie sie bisher vorgegangen sind könnte ich mir vorstellen dass sie einfach Milan auf altem Sockel weiterlaufen lassen fürs untere Ende (evtl dann mit Zen 4 Chiplets falls das irgendwie geht) und der Rest geht mit minimal 12 Kernen auf maximal 12 Chiplets weiterhin ganz nach oben mir dem Maximum an RAM und IO.

Zwischenlösungen mit weniger Chiplets sehen wir sicher auch bei genoa, dann aber ohne Einschränkungen beim IO und RAM

Raucherdackel!

Banned

- Registriert

- Jan. 2014

- Beiträge

- 3.266

Die sind doch alle unterschiedlich?Colindo schrieb:Wieso sehen die Chiplets in den beiden Grafiken denn gleich groß aus? Eins ist doch in N7 gefertigt, das andere in N5?

Hier mein 2400G in 14nm, bei 3,75 GHz schon nur 1,97W pro Kern. cTDP auf 25W gesetzt, boostet allcore auch auf die 3,75 GHz.PS828 schrieb:@pmkrefeld naja wenn man bedenkt dass es die 8C16T CPUs auch als U Variante mit 15W gibt passt das ganze auch so.

Der IO Die trägt bei der Rechnung in so einer CPU definitiv dazu bei dass in der Realität sogar weniger als die 3,3W Pro kern bleiben.

Da geht in 5nm bestimmt über 4GHz bei 2W.

Zuletzt bearbeitet:

icemanspirit

Ensign

- Registriert

- Aug. 2019

- Beiträge

- 169

T

Teralios

Gast

Zen wir soll AVX512 bringen was die FPU in der Größe alleine bei den Alus verdoppelt. Dazu noch Doppelte Anzahl an registerColindo schrieb:Wieso sehen die Chiplets in den beiden Grafiken denn gleich groß aus? Eins ist doch in N7 gefertigt, das andere in N5?

Tzk

Commodore

- Registriert

- Nov. 2016

- Beiträge

- 4.708

Gibt es, aber anders als man sich das so denkt. Ich zitiere mal den Threadripper 3990x Test hier von CB. Hervorhebung durch mich:S.Kara schrieb:Ich denke nicht dass es da ein Limit gibt.

Link: https://www.computerbase.de/artikel/prozessoren/amd-ryzen-threadripper-3990x-test.70675/seite-264-Bit-Versionen von Windows teilen logische Prozessorkerne seit Windows 7 in Gruppen ein. Bis zu 64 logische Prozessoren – so viele, wie der Ryzen Threadripper 3970X bietet – werden in einer Gruppe zusammengefasst. Für den Ryzen Threadripper 3990X bedeutet das, dass es zwei Gruppen zu je 64 logischen Kernen gibt. Windows berücksichtigt dabei, wie die physischen und damit auch die logischen Kerne auf der CPU angeordnet sind, um die Gruppen möglichst leistungsoptional anzuordnen.

Damit eine Anwendung mehr als nur die Kerne aus einer Gruppe ansprechen kann, muss sie allerdings dafür ausgelegt sein, denn Windows weist einer Anwendung aus Kompatibilitätsgründen nur eine Gruppe zu, und zwar im Wechsel, um die Last auf beide Gruppen zu verteilen.

Was sagt uns das nun? Microsoft muss (mal wieder...) nachbessern. Denn eine 192 Thread Cpu hätte sogar drei dieser Gruppen. Sprich Anwendungen die nicht explizit mit diesem Limit umgehen können laufen hier nur auf 64 Threads und somit liegen 2/3 der Leistung brach. Klasse.

Wieso sollte sie brach liegen? 64 Threads laufen zwar in einem Numa Node und beim 64 Kerner mit aktivem SMT demzufolge 2 davon aber es gibt durchaus Software welche diese auch gleichzeitig ansprechen kann. Bei einem System mit mehreren Sockeln hat man den Effekt genauso. Zudem bezieht sich das auch nur auf einen einzelnen Prozess und auch nur wenn die Software nicht mehrere Nodes nutzen kann.

@holdes ich hab das Problem nicht weil ich nur 64 Threads habe, wie ist das bei deinen Anwendungen? Hast du da welche die nur eine node Nutzen?

Windows muss da evtl nachbessern oder halt die Hersteller wenn sowas immer häufiger wird.

Am ende wechselt man für solche Anwendungen halt auf ein anderes Betriebssystem wo es wieder passt

Windows muss da evtl nachbessern oder halt die Hersteller wenn sowas immer häufiger wird.

Am ende wechselt man für solche Anwendungen halt auf ein anderes Betriebssystem wo es wieder passt