Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

News Für kleinere Zen-6-Epyc-CPUs: AMDs neuer Sockel SP8 besitzt 5.572 Kontaktflächen

@stefan92x : Hast Recht, eingesetzt hat Intel aber AFAIK dann auch nur MRDIMMs.

Aber nicht elektrisch. SP6 wird denk ich wieder für die Zen6c Epycs sein, wogegen für die Zen6-Threadripper sicherlich wieder ein eigener Sockel kommen wird (der evt. auf SP6 aufbaut).stefan92x schrieb:sTR5 ist eine Variante von SP6, physisch sind die beiden Sockel identisch.

- Registriert

- Juni 2001

- Beiträge

- 19.910

Vielleicht sind sie aber auch mal so clever das endlich zu vereinen. Denn why!?

Es ist schon zuletzt nur noch mehr Aufwand für eigentlich das gleiche gewesen. Siena von threadripper trennen bei 99% Gemeinsamkeiten aber nem anderen Sockel .. sowas von nicht nachhaltig, vor allem da die eh ständig den Sockel wechseln in dem Bereich. Also reichen auch 2 anstatt 3.

Zumal Intel bei DMR ja den kleinen Sockel ganz killt, da gibs nur noch den großen.

Es ist schon zuletzt nur noch mehr Aufwand für eigentlich das gleiche gewesen. Siena von threadripper trennen bei 99% Gemeinsamkeiten aber nem anderen Sockel .. sowas von nicht nachhaltig, vor allem da die eh ständig den Sockel wechseln in dem Bereich. Also reichen auch 2 anstatt 3.

Zumal Intel bei DMR ja den kleinen Sockel ganz killt, da gibs nur noch den großen.

- Registriert

- Feb. 2012

- Beiträge

- 7.184

- Registriert

- Feb. 2012

- Beiträge

- 7.184

Schade. Dann pack Dir einfach als Besuchergeschenk ein Rack ein und nimm‘s mit nach Hause

So wie ich das damals bei SP6 vs sTR5 verstanden hatte, gings wohl um Kosten. SP6 sollte einfach billiger sein. Die 8004er Epycs unterstützen nur Hexa-Channel und die SP6-Mainboard haben auch keinen Chipsatz, der an die CPU angebunden werden muss (die 8004er Epycs agieren als SoC). sTR5-Mainboards hingegen haben noch einen Chipsatz (TRX50, WRX90). Zumindest was die Mainboard Preise angeht, nimmt sich aber sTR5 und SP6 nicht allzuviel. Von daher hab ich auch keine Ahnung, warum man diese Unterscheidung macht.Volker schrieb:Denn why!?

- Registriert

- Juni 2001

- Beiträge

- 19.910

Ja wobei ein Board ja nochmal was anderes als nur der Sockel ist. Nen Chipsatz bindet man ja auch nur über PCI-Lanes an, und die Threaddis kosten auch bis zu 12.000 Euro. Die Kosten der Infrastruktur würden vermutlich insgesamt heutzutage günstiger sein wenn es nur eine anstatt zwei Plattformen wären, wenn man den ganzen Rattenschwanz von der Entwicklung, Validierung, vielen separaten Dinge hier und da alles berücksichtigt. Zumal sie ja explizit viele 1P-Epycs vermarkten usw usw.

Doch, braucht es. Weil du für 16 Lanes nicht nur 16 Pins oder für 64 Bit nicht nur 64 Pins brauchst. Wir leben nicht mehr im Jahr 1980, als Signale auch ohne Geschwindigkeitsverlust hätten getrommelt werden können. Um die Signalintegrität bei den heutigen Highspeed-Verbindungen garantieren zu können, müssen die Signal-Pins durch Ground-Pins abgeschirmt werden - viele davon.Rickmer schrieb:Das erklärt nur 256 (oder ein paar mehr) der zusätzlichen 1440 Pins...

Gleichermaßen braucht PCIe auch nicht unendlich viele Pins.

Auch die Energieversorgung ist deutlich komplexer geworden. Nicht nur, weil die Chips inzwischen enorme Leistungsaufnahmen haben, sondern auch, weil die Leistungsaufnahme durch Energiesparmechanismen im Millisekundentakt extrem schwankt und dabei die Spannung trotzdem stabil bleiben muss. Dafür werden totsicher mehr Pins benötigt, als unter perfekten, gleichförmigen Bedingungen zum Transport der Ströme theoretisch nötig wären.

Ich glaube du vertust dich da. Die Data Pins mit den extrem hohen Frequenzen kannst du nicht dicht an dicht packen. Schau dir mal ein pinout an, wie viele VSS Pins zur Abschirmung dazwischen liegen. Da kommst du grob auf 24 Pins pro Lane.Rickmer schrieb:Das erklärt nur 256 (oder ein paar mehr) der zusätzlichen 1440 Pins...

Gleichermaßen braucht PCIe auch nicht unendlich viele Pins.

Das Problem ist nur, dass die Gerüchte von 128 PCIe Lanes ausgehen.

Könnten aber auch gut für mehr Power drauf gehen.

Edit: Zu langsam

TeeKayEV schrieb:Doch, braucht es. Weil du für 16 Lanes nicht nur 16 Pins oder für 64 Bit nicht nur 64 Pins brauchst. Wir leben nicht mehr im Jahr 1980, als Signale auch ohne Geschwindigkeitsverlust hätten getrommelt werden können. Um die Signalintegrität bei den heutigen Highspeed-Verbindungen garantieren zu können, müssen die Signal-Pins durch Ground-Pins abgeschirmt werden - viele davon.

bensen schrieb:Ich glaube du vertust dich da. Die Data Pins mit den extrem hohen Frequenzen kannst du nicht dicht an dicht packen. Schau dir mal ein pinout an, wie viele VSS Pins zur Abschirmung dazwischen liegen. Da kommst du grob auf 24 Pins pro Lane.

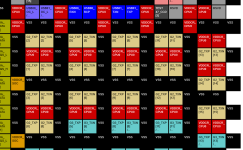

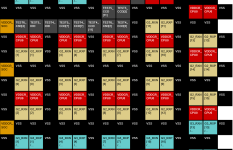

Es gibt von AMD öffentliche Pin Layout Maps. Hier für SP5:

https://upload.wikimedia.org/wikipedia/commons/9/94/Socket_SP5_pinmap.svg

Für Memory Channel A/G mal nachgezählt belegt der eine Fläche von 81x3 Pins, also 243 Pins insgesamt.

Wenn man noch die Flächen drumrum mit zählt kommt man auf maximal ca. 285 Pins für 2 Speicherkanäle.

Daher: auch wenn ich beim ersten Beitrag vergessen hatte, dass eine Signalleitung zwei Pins braucht, von den 1440 neuen Pins gehen nur ein Bruchteil an die Speicheranbindung.

[EDIT: Nevermind, ich sehe, dass der Speicherkanal-Block auf beiden Seiten der CPU gespiegelt vorhanden ist. Das sind dann 285 Pins pro 1 Speicherkanal. Okay.]

Gleichermaßen auch wenn man sich PCIe anschaut. Wie du auf 24 Pins pro Lane kommst, müsstest du mir mal im Detail anhand eines Screenshot erklären. Ich komme auf 60-70 Pins für einen 16 Lane Block.

Zuletzt bearbeitet:

Es sind 12. Hatte auf den Weg dorthin vergessen durch zwei zu teilen. Teilweise werden die Lücken mit VDD gefüllt, also eher 10, falls das Layout ähnlich ist. Ich hatte AM5 als Basis genommen.Rickmer schrieb:Gleichermaßen auch wenn man sich PCIe anschaut. Wie du auf 24 Pins pro Lane kommst, müsstest du mir mal im Detail anhand eines Screenshot erklären. Ich komme auf 60-70 Pins für einen 16 Lane Block.

Keine Ahnung wie du auf 60-70 kommen willst. Es sind ja schon je ein Pärchen pro Richtung, also 64 Data Pins.

Wie kommst du auf 256 Pins?Rickmer schrieb:Das erklärt nur 256 (oder ein paar mehr) der zusätzlichen 1440 Pins...

Gleichermaßen braucht PCIe auch nicht unendlich viele Pins.

Dir ist schon klar, dass ein DDR5 Sockel 288 Kontakte besitzt?

Vielleicht erstmal einlesen, statt komische Nummern präsentieren. ;-)

Ergänzung ()

TR sind halt einfach ein Abfallprodukt der EPCY. Nimm es oder lass es - der Markt wird zu klein sein, als dass sich dort großer Aufwand lohnt.Tigerfox schrieb:sTR5 wieder nur zwei Generationen - absolut genial AMD!

Mit der Herangehensweise wird der Markt auch nie größer werden. Enthusiasten sind zwar eher bereit, das ganze System auszutauschen als andere, aber bei Mainboardpreisen von 700 bis 1.000€ mit wenigen Ausnahmen unter 600€ sollte man doch eher höhere Lebensdauer als niedrige erwarten, vor allem ohne großen Mehrwert (was wird ein Mainboard Zen6 einem TRX50/WRX80 vorraus haben? Ggd. MRDIMM, sonst nichts).Nagilum99 schrieb:TR sind halt einfach ein Abfallprodukt der EPCY. Nimm es oder lass es - der Markt wird zu klein sein, als dass sich dort großer Aufwand lohnt.

Wie es im Serverbereich aussieht weiss ich nicht, aber ohne große Not wird hier doch wohla uch kein Geld zum Fenster rausgeschmissen.

So ganz Abfallprodukte ohne Entwicklungsaufwand sind die TR AFAIK aber nicht - Quadchannel und den IOD der kleinen TR gibt es bei Epyc nicht. Bin aber nicht im Bilde, ob das tatsächlich dedizierte Hardware oder nur softwareseitige Beschränkungen sind.

Dir ist schon klar, dass grob die Hälfte davon für Power oder (größtenteils) Ground sind, welches keine direkte Leitung zum CPU Socket benötigt?Nagilum99 schrieb:Dir ist schon klar, dass ein DDR5 Sockel 288 Kontakte besitzt?

Vielleicht erstmal einlesen, statt komische Nummern präsentieren. ;-)

Und vielleicht erst nochmal den Rest vom Thread lesen. Ich hatte schon realisiert, dass ich mich verzählt hatte. Aber nicht weil ein DDR5 Sockel 288 Kontakte besitzt.

PS: Der SO-DIMM Sockel hat nur 262 Kontakte und gleich viele Datenleitungen.

Ergänzung ()

Weil ich nicht gesehen hatte, dass RX und TX komplett über den Sockel gestreut sind.bensen schrieb:Keine Ahnung wie du auf 60-70 kommen willst. Es sind ja schon je ein Pärchen pro Richtung, also 64 Data Pins.

Ja, das passt schon eher zu dem was auf dem Screenshot zu sehen ist.bensen schrieb:Teilweise werden die Lücken mit VDD gefüllt, also eher 10, falls das Layout ähnlich ist. Ich hatte AM5 als Basis genommen.

Ich hätte auf grobe Schätzung eher 9 gesagt, aber 10 könnten auch passen. Die meisten VSS Pins kann man eh nicht eindeutig einem Funktionsblock zuordnen, da die zwischen Blöcken liegen.

Zuletzt bearbeitet:

Höhere Lebensdauer bedeutet auf neue Funktionen verzichten. Das ist nicht enthusiastisch.Tigerfox schrieb:sollte man doch eher höhere Lebensdauer als niedrige erwarten,

PCIe 6.0 und damit massiv mehr IO-Bandbreite. Und natürlich schnelleren RAM, wie du selbst erkannt hast. Also grob den doppelten Datendurchsatz, den ein WRX80 Board schaffen kann.Tigerfox schrieb:was wird ein Mainboard Zen6 einem TRX50/WRX80 vorraus haben?

Die sind aber tatsächlich nur beschnitten, keine extra Entwicklung.Tigerfox schrieb:Quadchannel und den IOD der kleinen TR gibt es bei Epyc nicht.

catch 22

Vice Admiral

- Registriert

- Mai 2019

- Beiträge

- 6.375

die Fragen für den Käufer eines solchen Racks sind doch eigentlich, wie wird der Redakteur in der Versandkiste gesichert? In Luftpolsterfolie oder klassische Styropor? Und muss man den dann durchfüttern, oder ist der Selbstversorgend? Und ganz wichtig, wie viele TFLOPS hat der?coxon schrieb:

Natürlich entsteht Aufwand, aber der ist stark reduziert. Da geht viel über Firmware/Konfiguration und bleib realistisch: Das ist eher Workstation- als Enthusiastenplattform. Wozu braucht ein normaler "Enthusiast" mehr als 32 (oder dann evtl. 48) Threads und 256 GB RAM?Tigerfox schrieb:Mit der Herangehensweise wird der Markt auch nie größer werden. Enthusiasten sind zwar eher bereit, das ganze System auszutauschen als andere, aber bei Mainboardpreisen von 700 bis 1.000€ mit wenigen Ausnahmen unter 600€ sollte man doch eher höhere Lebensdauer als niedrige erwarten, vor allem ohne großen Mehrwert (was wird ein Mainboard Zen6 einem TRX50/WRX80 vorraus haben? Ggd. MRDIMM, sonst nichts).

Wer die Dinger kauft, denkt eher selten an aufrüsten sondern kauft sowas meistens von Anbietern und das läuft, bis das System ersetzt wird. Dein Problem ist kein Problem des (finanziell relevanten) Marktes.

Allein durch den Sockel und die nötigen Routings, die TDP etc. sind Mainboardpreise von 2 oder 300 € Realitätsverlust.

Ich glaub nicht mal, dass der TR MRDIMM anbieten wird. Evtl. bring er PCIe 6 und 6400er RDIMM.