Silverhand

Ensign

- Registriert

- Jan. 2010

- Beiträge

- 185

Guten Morgen

Da ich nicht 100% sicher bin, wie die Verteilung der Bandbreite zwischen Graka und SSDs ist,

wollte ch das hier nachfragen.

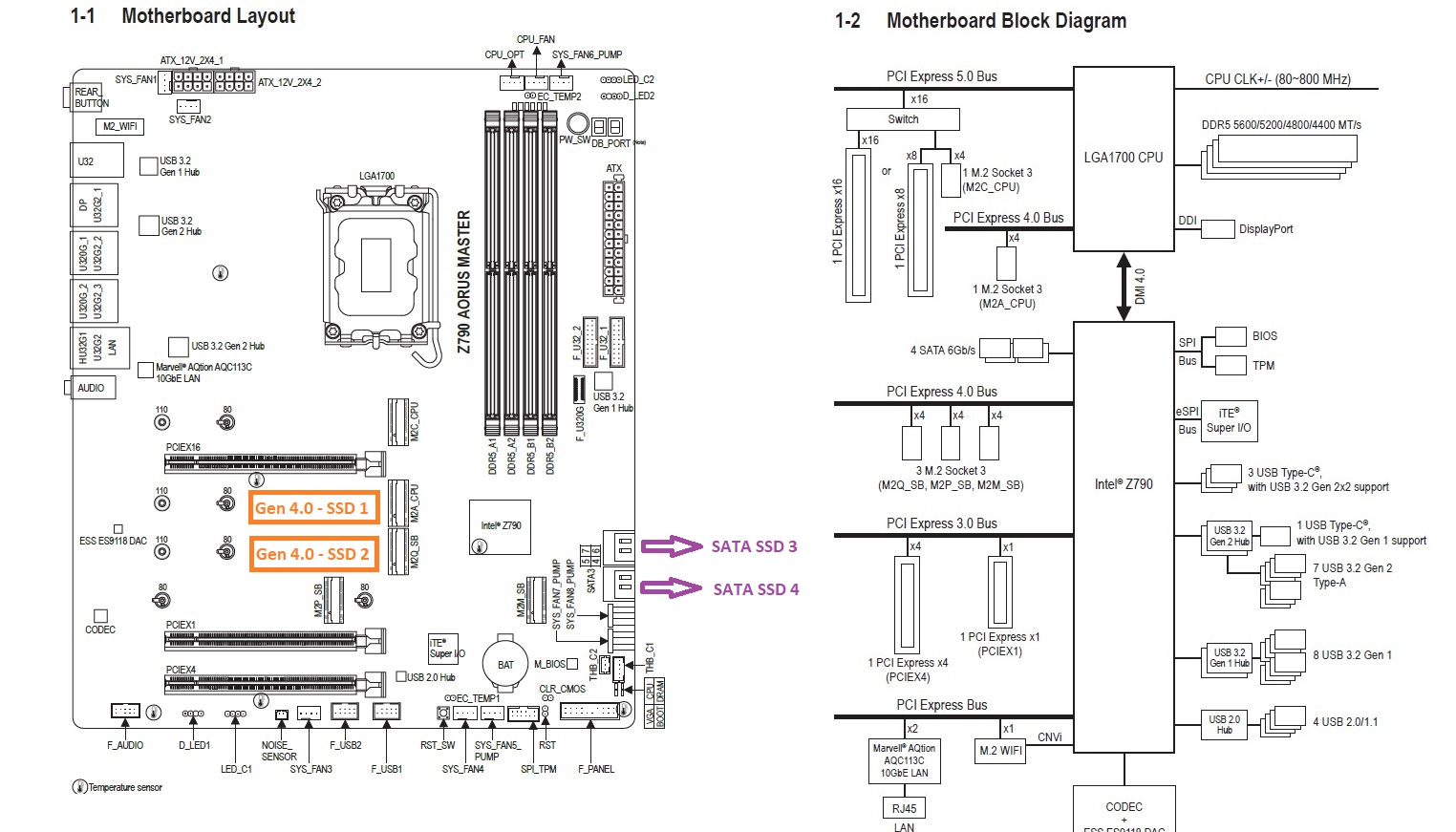

Ich habe 2 schnelle Gen. 4.0 - NVME SSD's und 2 normale SATA SSD's.

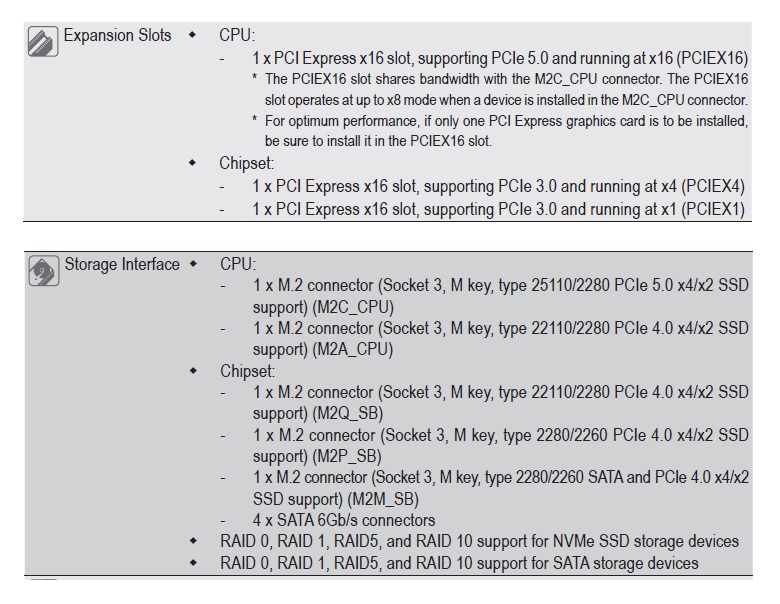

Im obersten NVME Slot (M2C_CPU), habe ich keine NVME angeschlossen, da dieser Slot die Bandbreite mit der Grafikkarten teilt. Habe ich das richtig verstanden?

"The PCIEX16 slot shares bandwidth with the M2C_CPU connector.

The PCIEX16 slot operates at up to x8 mode when a device is installed in the M2C_CPU connector."

Wenn ich jetzt meine 2 NVME in die Slots 2 & 3 anschliesse (wie auf der Skizze), haben die 2 NVME oder die Grafikkarte irgendwelche Leistungseinbussen? (egal in welchem Prozentbereich )

)

Meine zweite Frage.

Spielt es eine Rolle wenn ich 2 NVME + 2 SATA SSD's anschliesse (wie auf der Skizze),

oder beeinträchtigen die 2 SATA SSD's irgendwie die Leistung von den NVME oder der Grafikkarte?

Ich blicke da leider nicht so durch... vielen Dank für die Hilfe

CPU: i9-13900K

MOBO: Gigabyte Z790 AORUS MASTER

Graka: Palit RTX 4090 Gaming OC

NVME 1: Seagate FireCuda 530 (Gen. 4.0)

NVME 2: XPG Gammix S50 (Gen. 4.0)

SATA 1: Samsung 850 EVO

SATA 2: Samsung 840 PRO

Da ich nicht 100% sicher bin, wie die Verteilung der Bandbreite zwischen Graka und SSDs ist,

wollte ch das hier nachfragen.

Ich habe 2 schnelle Gen. 4.0 - NVME SSD's und 2 normale SATA SSD's.

Im obersten NVME Slot (M2C_CPU), habe ich keine NVME angeschlossen, da dieser Slot die Bandbreite mit der Grafikkarten teilt. Habe ich das richtig verstanden?

"The PCIEX16 slot shares bandwidth with the M2C_CPU connector.

The PCIEX16 slot operates at up to x8 mode when a device is installed in the M2C_CPU connector."

Wenn ich jetzt meine 2 NVME in die Slots 2 & 3 anschliesse (wie auf der Skizze), haben die 2 NVME oder die Grafikkarte irgendwelche Leistungseinbussen? (egal in welchem Prozentbereich

Meine zweite Frage.

Spielt es eine Rolle wenn ich 2 NVME + 2 SATA SSD's anschliesse (wie auf der Skizze),

oder beeinträchtigen die 2 SATA SSD's irgendwie die Leistung von den NVME oder der Grafikkarte?

Ich blicke da leider nicht so durch... vielen Dank für die Hilfe

CPU: i9-13900K

MOBO: Gigabyte Z790 AORUS MASTER

Graka: Palit RTX 4090 Gaming OC

NVME 1: Seagate FireCuda 530 (Gen. 4.0)

NVME 2: XPG Gammix S50 (Gen. 4.0)

SATA 1: Samsung 850 EVO

SATA 2: Samsung 840 PRO