Ich finde den Ton des Artikels ein bisschen seltsam.

Das Ausbalancieren der Cache-Hierarchie mit Größen und Latenzen ist notwendig, um aus einem Kern die erforderliche Performance herausholen zu können.

1 MByte L2-Cache ist eine Verdoppelung zum Zen 3. Es ist fast so viel wie beim Golden Cove. Es ist aber im Vergleich zum Firestorm-Kern wenig.

Raucherdackel! schrieb:

Interessant! Wenn AMD damit zu Intel (fast) aufschließt, dürfen wir auch die ungefähre Leistung der Performance Kerne erwarten.

Golden Cove und Zen 3 unterscheiden sich in einigen Punkten.

Die Größe des L2-Caches ist nur ein Punkt. Außerdem ist die Latenz ebenso wichtig wie die Größe des Caches. So wie ich es verstehe steigt mit der Größe des Caches auch seine Latenz.

incurable schrieb:

Vielleicht sollten wir erst abwarten, bei welchen Latenzen der größere L2 von AMD landet.

Es könnte gut sein, dass AMD hier auf den neuen Prozess gewartet hat.

Ich gehe davon aus, dass AMD intensiv getestet hat welches Set-up für die Caches die beste Performance bei akzeptablen Kosten hat.

bensen schrieb:

Vor allem wird durch kurze Strecken auch die Latenz nicht viel größer. Das ist schon revolutionär. Große und schnelle Caches.

Prinzipiell: Wenn man stapelt werden die Wege kürzer.

Wenn AMD die 96 MB auf eine Ebene gepackt hätte, wären die Wege viel länger und damit auch die Latenzen.

bensen schrieb:

Wie man das für den L2 Cache lösen wollte, wüsste ich nicht. Momentan sicherlich nicht sinnvoll möglich.

Zur Zeit noch.

Man muss das Stapeln auch hinbekommen. Es wird bisher nur bei Speichertechnologien (HBM und §D-NAND) und Kamerasensoren eingesetzt. Der 3D V-Cache ist meines Wissens das erste echte 3D-Stacking bei Logikschaltkreisen.

Beim Stapeln gibt es auch

Probleme:

- Fläche für die TSV und ihre Kontakte.

- Um die TSV muss man eine Keep out einrichten, weil dort die Schaltungen gestört werden könnten.

- Wärmeabfuhr

DevPandi schrieb:

Mehr Cache ist nicht unbedingt der heilige Gral, sondern ein möglicher Weg.

Ja.

Es gibt in der Technik und somit auch im Chipdesign keinen

heiligen Gral und auch keine

silver bullets.

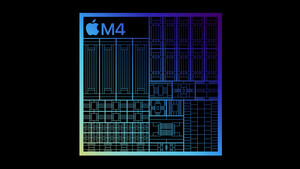

Vor allem sollte man sich Mal auf den

Die-Shots ansehen wie viel Fläche die L1- und L2-Caches und die zugehörigen Datenstrukturen benötigen:

Und mehr Cache spendiert man nur wenn der hohe Flächenverbrauch in mehr Performance umgesetzt werden kann. Und da wie schon gesagt die Latenz leidet gilt auch für Caches: Viel hilft viel tzrifft eben nicht zu. Extrem wichtig ist wie sie umgesetzt werden.