Halbleiterfertigung: IBM hat ersten 2-nm-Chip entwickelt

Auch wenn die Zahlen über die eigentlichen Strukturbreiten oder die Fortschrittlichkeit eines Chips nicht mehr viel aussagen, geht das Nanometer-Rennen weiter. IBM rühmt sich jetzt mit dem ersten 2-Nanometer-Chip. Der neue Herstellungsprozess verspricht große Fortschritte bei Leistung und Effizienz.

IBM nennt Vorzüge von 2 nm gegenüber 7 nm

Im Vergleich zu den „aktuell fortschrittlichsten 7-nm-Chips“ soll das von IBM entwickelte 2-nm-Verfahren Chips mit einer 45 Prozent höheren Leistung (in der Regel ist die Taktrate gemeint) oder 75 Prozent geringeren Leistungsaufnahme ermöglichen, so zumindest die Prognose. Mit welchem 7-nm-Verfahren IBM hier vergleicht, bleibt aber offen. Im weltweiten Halbleitergeschäft sind derzeit vor allem die 7-nm-Prozesse vom Auftragsfertiger TSMC sehr gefragt, aber auch Samsung fertigt in 7 nm. Bei Intel steht das 7-nm-Verfahren durch die Verzögerungen beim 10-nm-Prozess noch aus. TSMC fertigt den Apple A14 Bionic seit dem vergangenen Jahr bereits in 5 nm.

Demand for increased chip performance and energy efficiency continues to rise, especially in the era of hybrid cloud, AI, and the Internet of Things. IBM's new 2 nm chip technology helps advance the state-of-the-art in the semiconductor industry, addressing this growing demand. It is projected to achieve 45 percent higher performance, or 75 percent lower energy use, than today's most advanced 7 nm node chipsi.

iBased on the projected industry standard scaling roadmap

IBM

Schon bei 7 nm und 5 nm hatte IBM Research die ersten Chips entwickelt, bringt kommerzielle Produkte in 7 nm aber erst später in diesem Jahr in Form der Prozessorfamilie IBM Power10 auf den Markt. Bis zu einer Serienfertigung der 2-nm-Chips dürfte es also noch eine ganze Weile dauern und andere Hersteller könnten schon früher mit vergleichbar gefertigten Produkten am Markt sein. Die 7-nm-Chips von IBM werden von Samsung in Serie gefertigt, sodass bei 5 nm und 2 nm ebenfalls eine Partnerschaft wahrscheinlich ist. IBM ist vor allem ein Halbleiter-Forscher und weniger ein Halbleitermassenproduzent und hat erst im März eine Kooperation mit Intel angekündigt, die die Forschung und Entwicklung neuer Techniken umfasst.

Rekordverdächtige Transistordichte

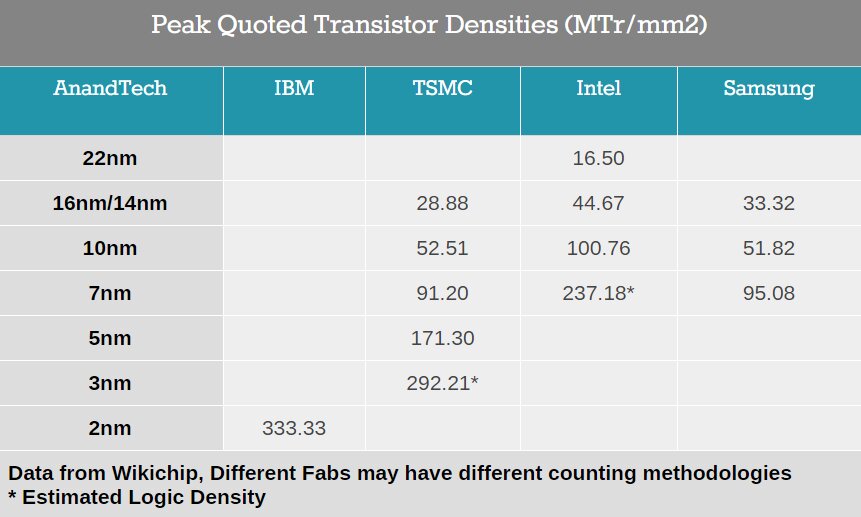

Während IBMs Pressemitteilung nur unpräzise technische Details wie „50 Milliarden Transistoren auf der Größe eines Daumennagels“ liefert, hatten US-Medien wie AnandTech die Gelegenheit, vorab mehr Informationen in Erfahrung zu bringen. Demnach sollen die 50 Milliarden Transistoren auf einer Fläche von rund 150 mm² unterkommen, was umgerechnet 333 Millionen Transistoren pro mm² (MTr/mm²) bedeutet. Dies ist laut den von AnandTech von der Website Wikichip zusammengetragenen Daten eine größere Transistordichte als die Schätzungen für die kommenden Prozesse 3 nm bei TSMC (292,21 MTr/mm²) oder 7 nm bei Intel (237,18 MTr/mm²). Das populäre 7-nm-Verfahren bei TSMC soll bei rund 91,2 MTr/mm² liegen.

Eine Abbildung von IBM zeigt die sogenannten „2nm Nanosheet Devices“ unter dem Mikroskop, die mit je drei übereinander gestapelten Gate-All-Around (GAA) bestückt sind. Auch TSMC will ab 2 nm GAA-Technik einsetzen, die der herkömmlichen FinFET-Technik überlegen ist. Bei Samsung stehen GAA-Transistoren für den kommenden 3-nm-Prozess auf dem Fahrplan.

-

IBMs 2 nm Technik im Überblick (Bild: IBM (via ZDNet))

IBMs 2 nm Technik im Überblick (Bild: IBM (via ZDNet))

Die „3-stack“-GAA-Zelle von IBMs 2-nm-Chip misst 75 nm in der Höhe und 40 nm in der Breite, während die Gate-Länge mit 12 nm und die Höhe der sogenannten Nanosheets mit 5 nm angegeben wird. Strukturen, die 2 nm messen, sucht man in der IBM-Folie vergebens. Die Nanometer-Bezeichnungen sind im Zeitalter der 3D-Transistoren vielmehr als Äquivalent zu einem 2D-Transistor-Design zu verstehen und geben dem Kind einen Namen.

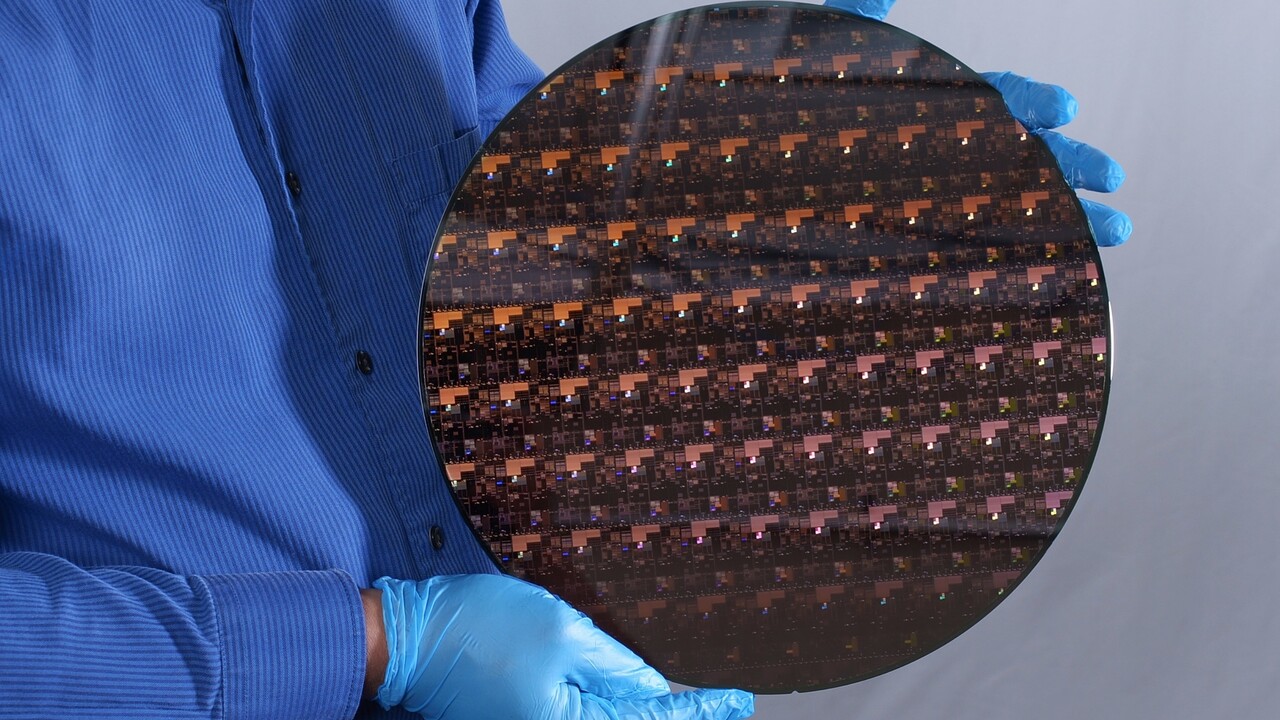

Testchips im Bild, Produkte Ende 2024

Die auf dem von IBM gezeigten Wafer zu sehenden 2-nm-Chips aus der Albany-Anlage von IBM Research sind noch keine fertigen Produkte und dienen nur zur Demonstration des neuen Herstellungsverfahrens. AnandTech mutmaßt, dass es sich um vereinfachte SRAM-Chips „mit ein wenig Logik“ handelt.

Wie ZDNet berichtet, hat IBM den Zeitraum für den Start der 2-nm-Serienfertigung auf Ende 2024 eingegrenzt. Bei welchem Halbleiterhersteller das 2-nm-Verfahren von IBM zum Einsatz kommen wird, bleibt aber abzuwarten. Dass die 2-nm-Fertigung nicht nur für die eigenen IBM-Power- und IBM-Z-Systeme Verwendung finden wird, ist wie auch eine Lizenzierung der Technik an Partner wahrscheinlich.

IBM hat noch einige Beispiele für die potenziellen Vorzüge entsprechender Chips formuliert, wie etwa eine Vervierfachung der Akkulaufzeit von Handys, eine drastische Reduzierung des Energiebedarfs von Rechenzentren, schnellere Laptops oder einer schnelleren Objekterfassung für selbstfahrende Autos. Was die Chips letztlich wirklich leisten werden, ist noch abzuwarten.