Hot Chips 33: TSMC zu Packaging, Kühlung und Silicon Photonics

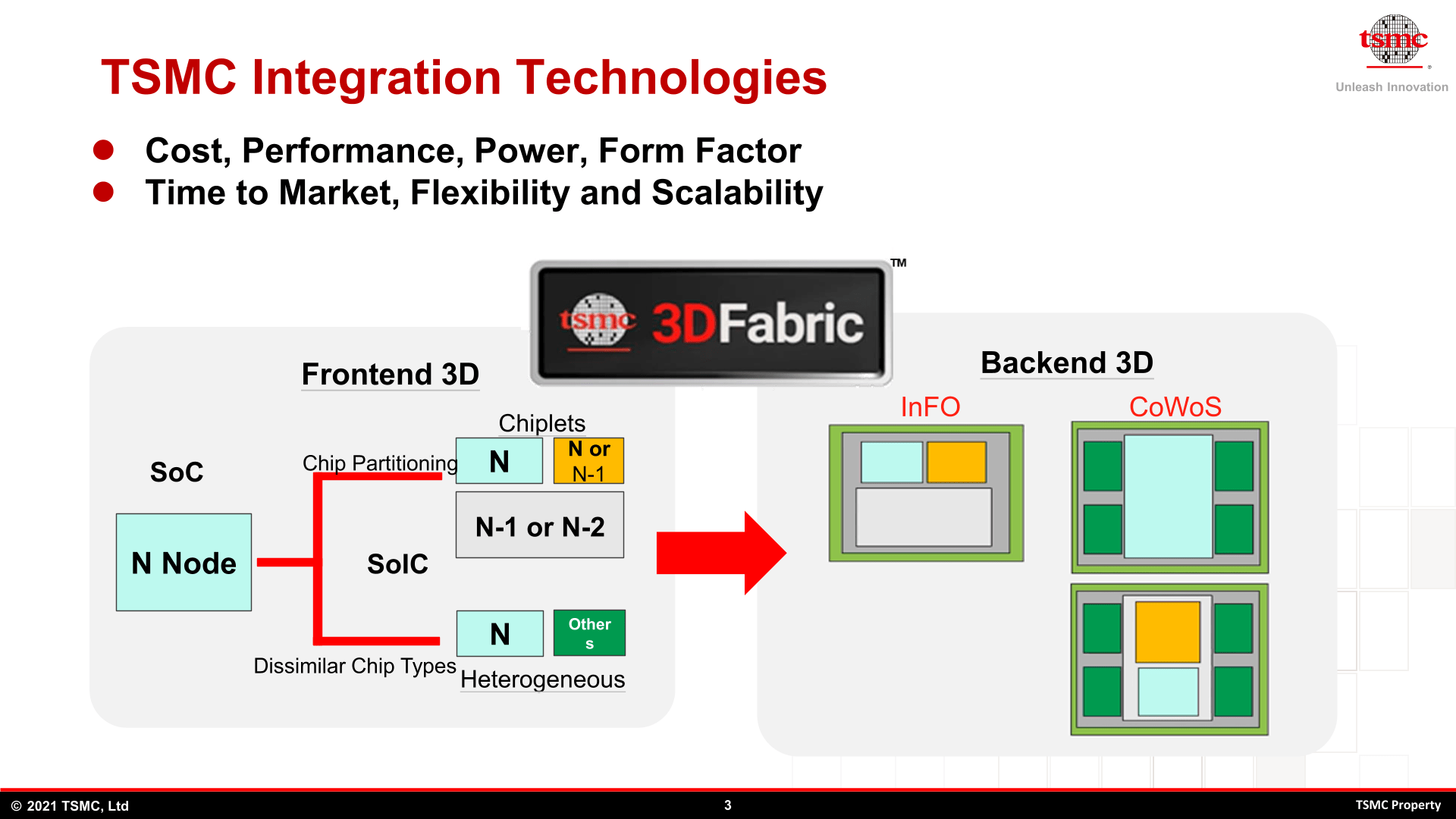

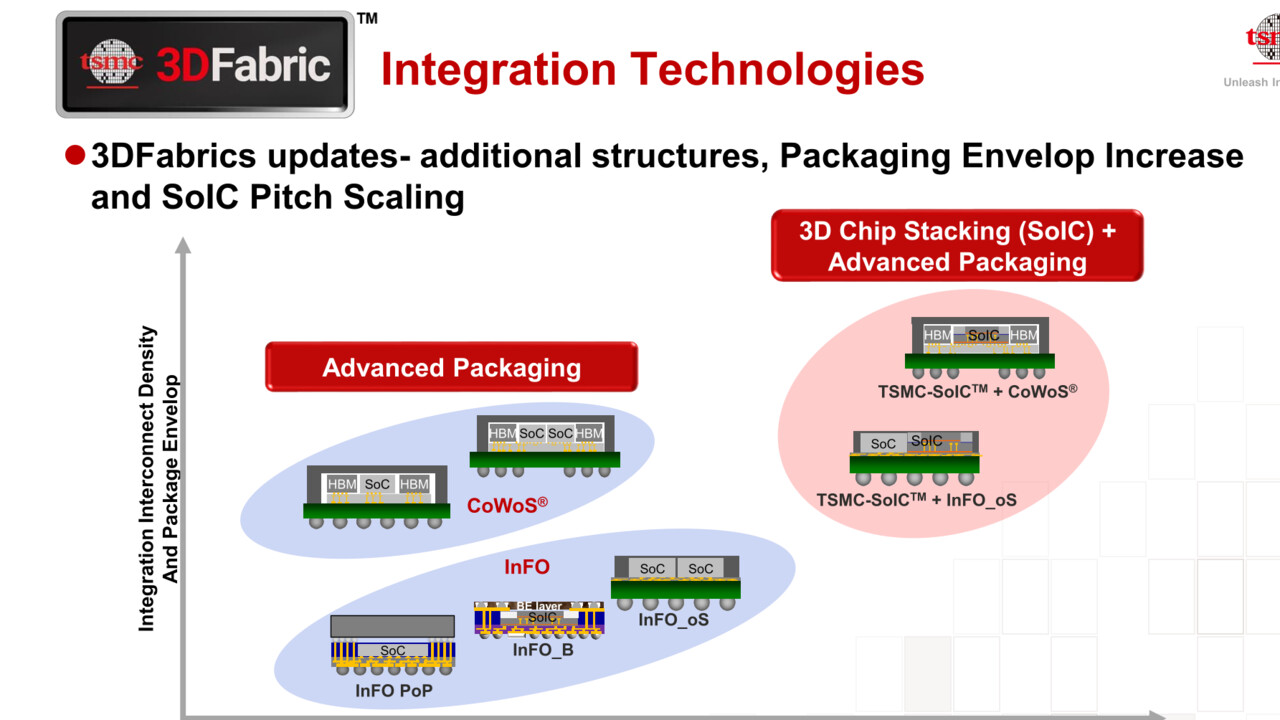

AMD und Intel reden beim Packaging von Marktführerschaft, doch der eigentliche Star ist TSMC, wie sie zur Hot Chips 33 erneut bewiesen. Vor allem das neue 3DFabric, unter dem Markenzeichen das Unternehmen die modernen Stacking- und Packaging-Verfahren bündelt, ist neben InFO und CoWoS der Weg in die Zukunft für TSMCs Kundschaft.

Über eine Stunde nahm sich TSMC im Rahmen von Hot Chips 33 Zeit um über die aktuellen und zukünftigen Formate nur in diesem Marktbereich zu sprechen. Gleich zu Beginn stellte TSMC klar, dass es diese vielen Technologien und Codenamen nicht gibt, um die Kundschaft zu verwirren. Es gibt für jedes Modell spezielle Einsatzgebiete mit Vorteilen, die ein Kunde nutzen kann.

An der Spitze der Hierarchie, im HPC-Segment, werden viele Neuerungen zuerst umgesetzt. Hier sind finanzielle Mittel oft großzügiger bemessen, wenngleich auch die Anforderungen ganz andere sind. Ganze Systeme werden hier beispielsweise auf einem Wafer realisiert, die selbst gegenüber fortgeschrittenen Multi-Chip-Modulen deutliche Vorteile bieten. Sie eigenen sich aber nur für extrem große Systeme und sind deshalb selbst im HPC-Segment noch echte Exoten, die ihre ganz eigenen Anforderungen beispielsweise auch an die Kühlung mitbringen: 7.000 Watt kann die passende Kühllösung abführen – zumindest im Labor bisher, gab TSMC auf Nachfrage zu verstehen.

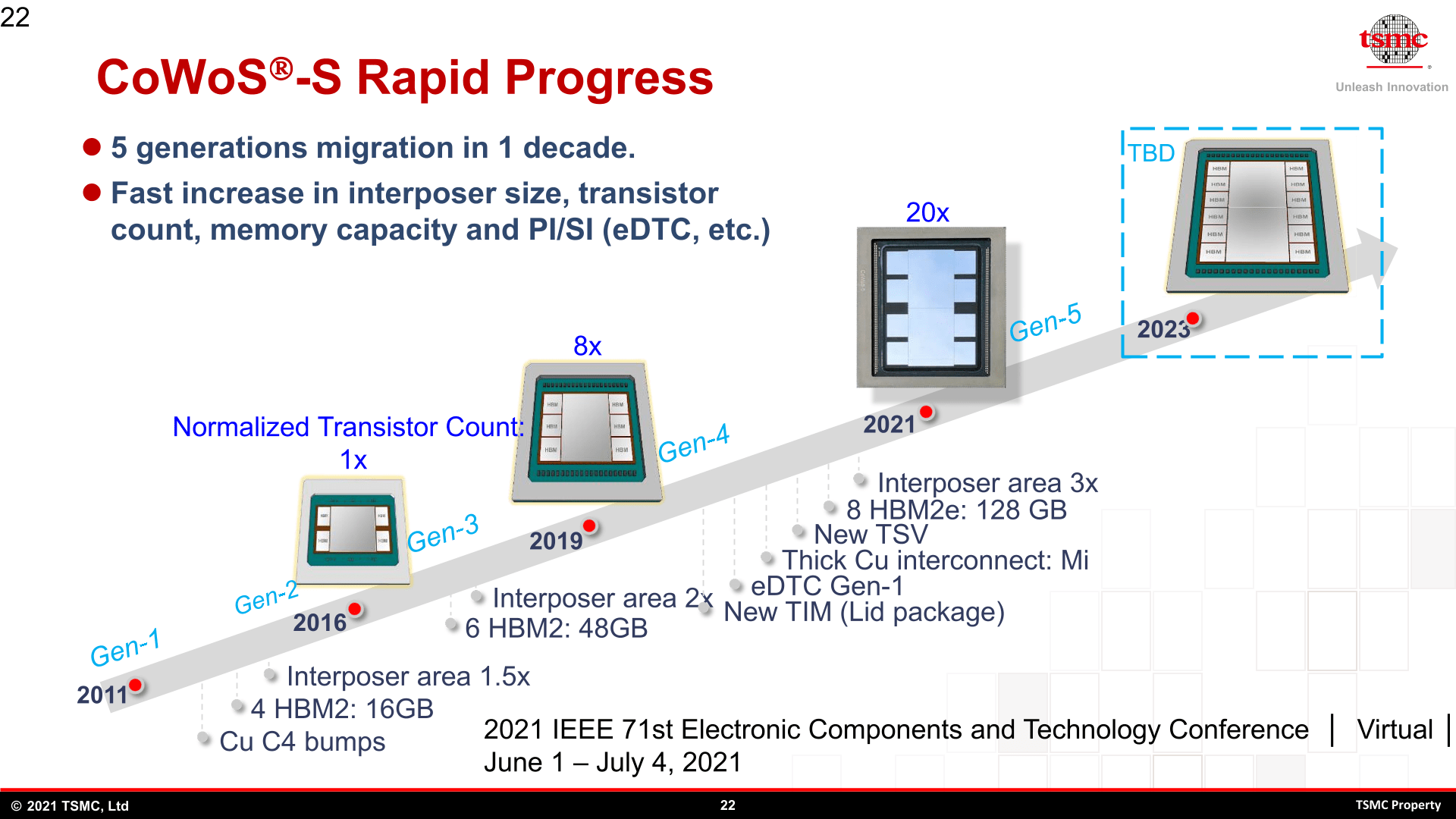

CoWoS steht für das bekannte 2,5D-System, welches bereits seit Jahren genutzt wird. Im einfachsten Sinne ist das ein Interposer, der auf dem Chip nebst Speicher verbaut ist, so bereits mehrfach beispielsweise bei Grafiklösungen gesehen. Eine Roadmap zeigt die bisherigen Errungenschaft aber auch das Ziel, noch mehr Chips auf einem Package unterzubringen. Ein 2.500 mm² großer Interposer mit zwei großen SoCs und 8 HBM-Chips sind das aktuelle Aushängeschild, in Zukunft wird die Anzahl weiter steigen.

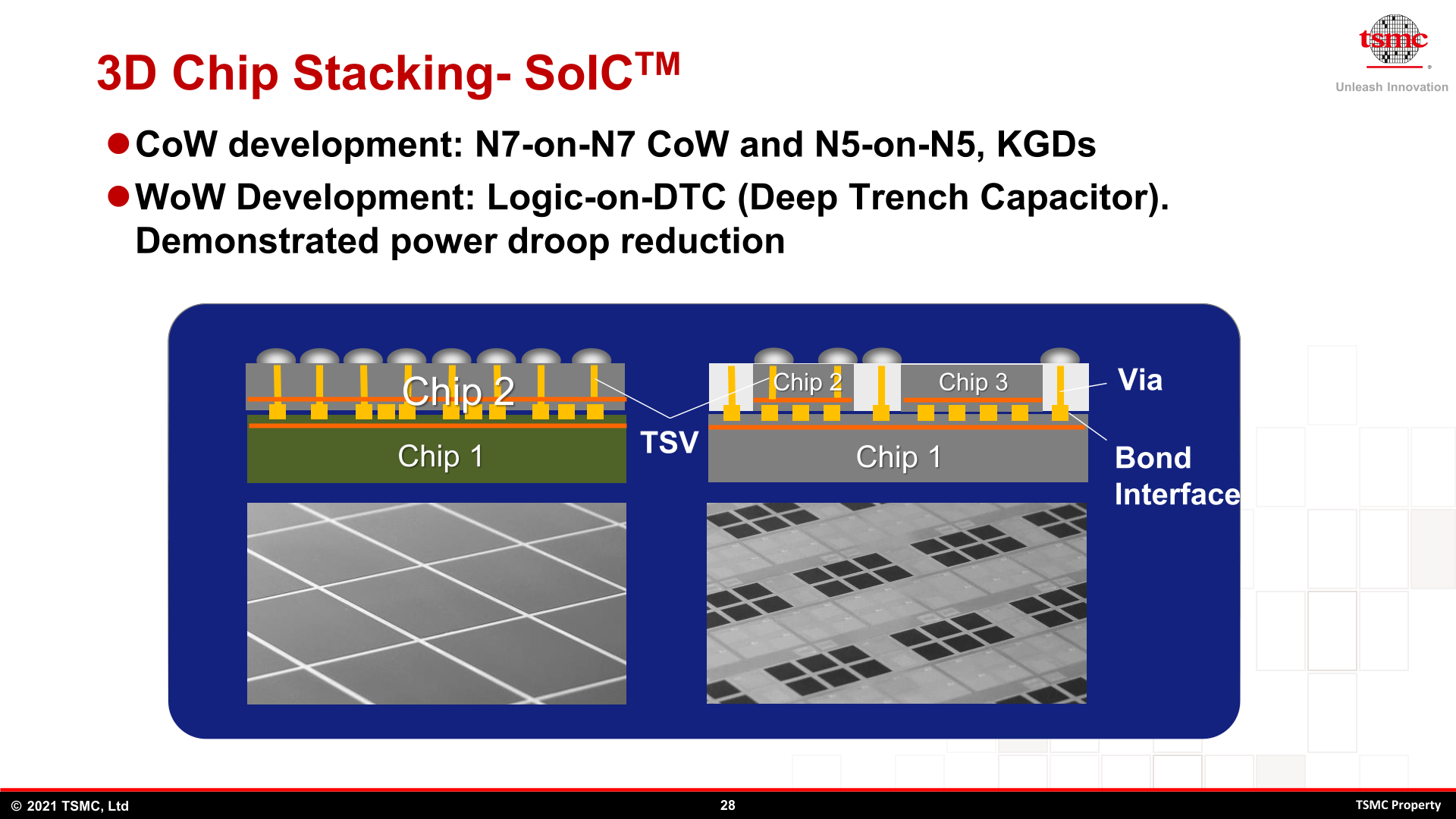

Zu CoW zählt auch die erste Lösung des 3D-Chip-Stacking, die AMD nutzen wird. Ein in N7 gefertigter Chip wird auf einen anderen in N7 gefertigten Chip gesetzt. Die Serienproduktion läuft zum Ende des Jahres an, bestätigt TSMC erneut, kurze Zeit später soll aber bereits N5 auf N7 folgen, N6 wird als schneller Zwischenschritt aber explizit auch genannt. Mischungen sind bisher nicht vorgesehen, dürften letztlich aber an irgend einem Punkt ebenfalls möglich werden. Die Roadmap gibt zudem erste Hinweise darauf beim Übergang zu N3. Das Verfahren Wafer on Wafer (WoW) dauert hingegen noch etwas länger.

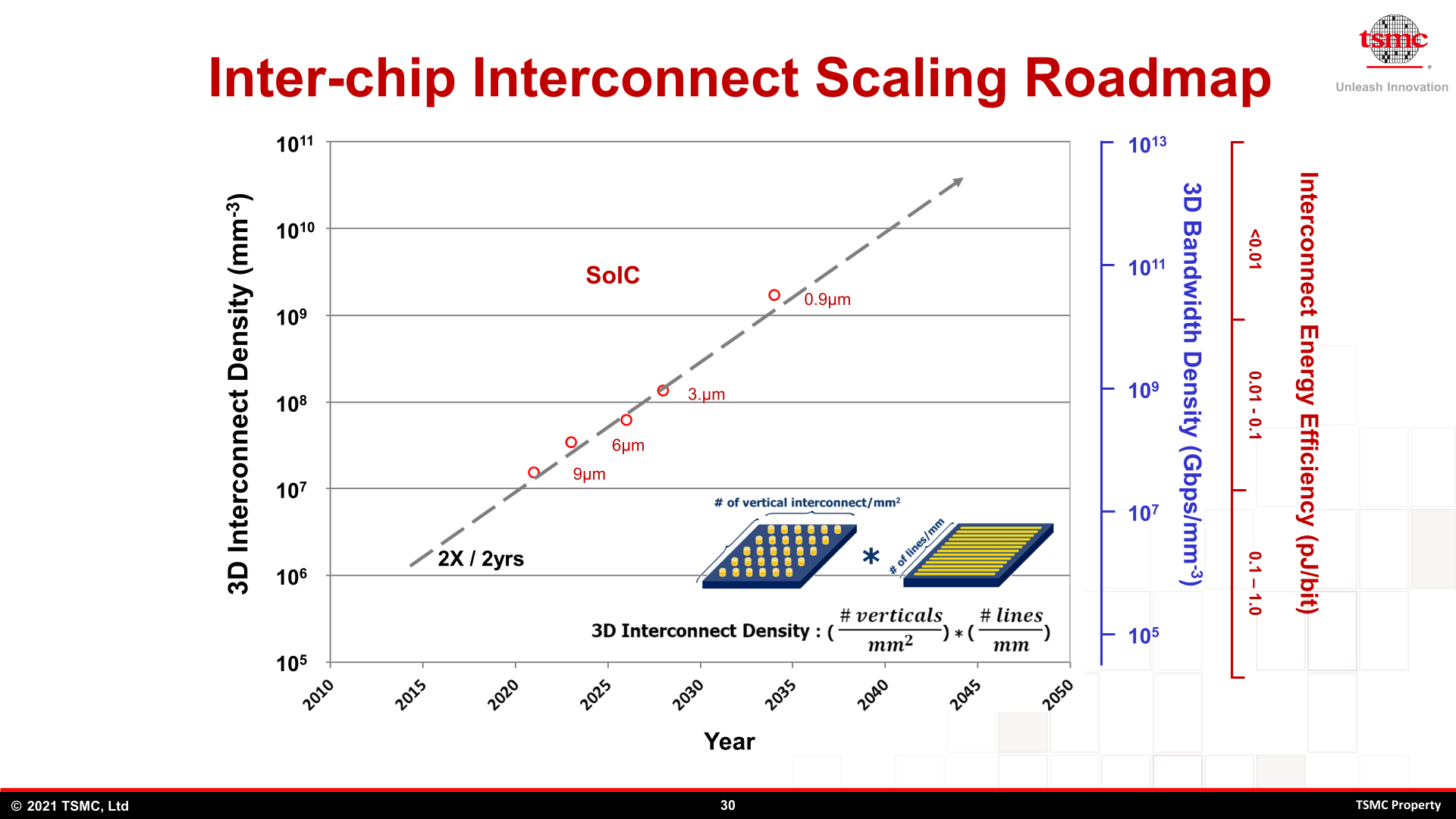

Interessant ist dabei die Scaling-Roadmap für die kleinen Interconnect-Verbindungen, die beim Stapeln benötigt werden. AMD gab bereits bekannt, dass der gestapelte L3-Cache bei den kommenden Ryzen-Prozessoren mit 3D V-Cache auf Verbindungen mit 9 µm Abstand setzt. TSMCs Roadmap sieht diverse Verkleinerungen bis hinab zu 0,9 µm vor – allerdings binnen über zehn Jahren.

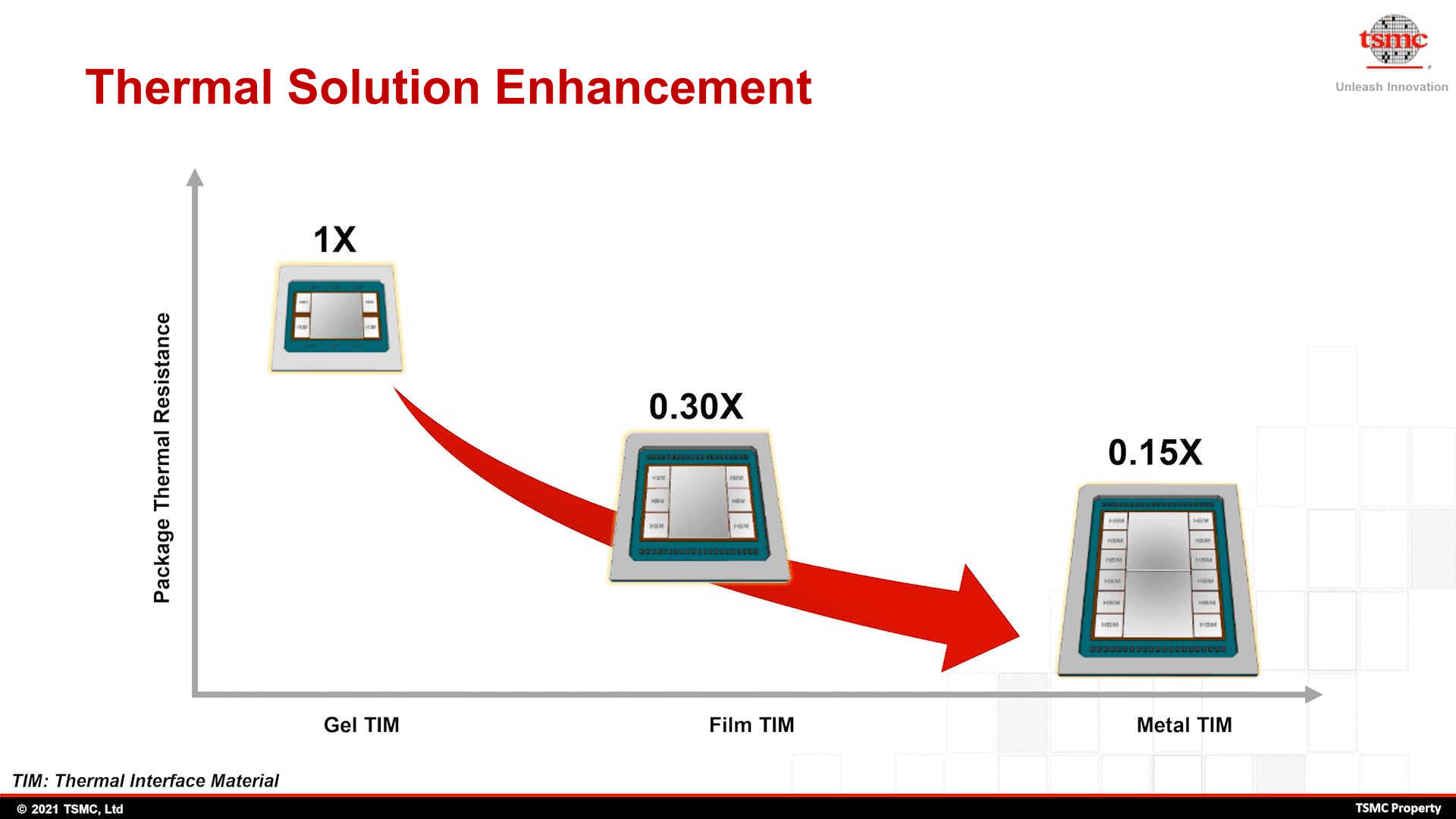

Das ganze Thema Stacking stellt jedoch Herausforderungen an die Kühlung, ein Thema das auch Intel zur Hot Chips 33 angeschnitten hatte. Gestapelte Chips lassen sich mitunter schlecht kühlen, Zwischenschichten aus flüssigem Metall zur Kühlung sollen helfen, die dabei möglichst nah an der Wärmequelle vorbeiführen. Gegenüber der direkten Wasserkühlung im HPC-Segment gibt es für einige der Entwicklungen große Gewinne bei der Wärmeabfuhr, die Mischung aus beiden ist am Ende das Beste.

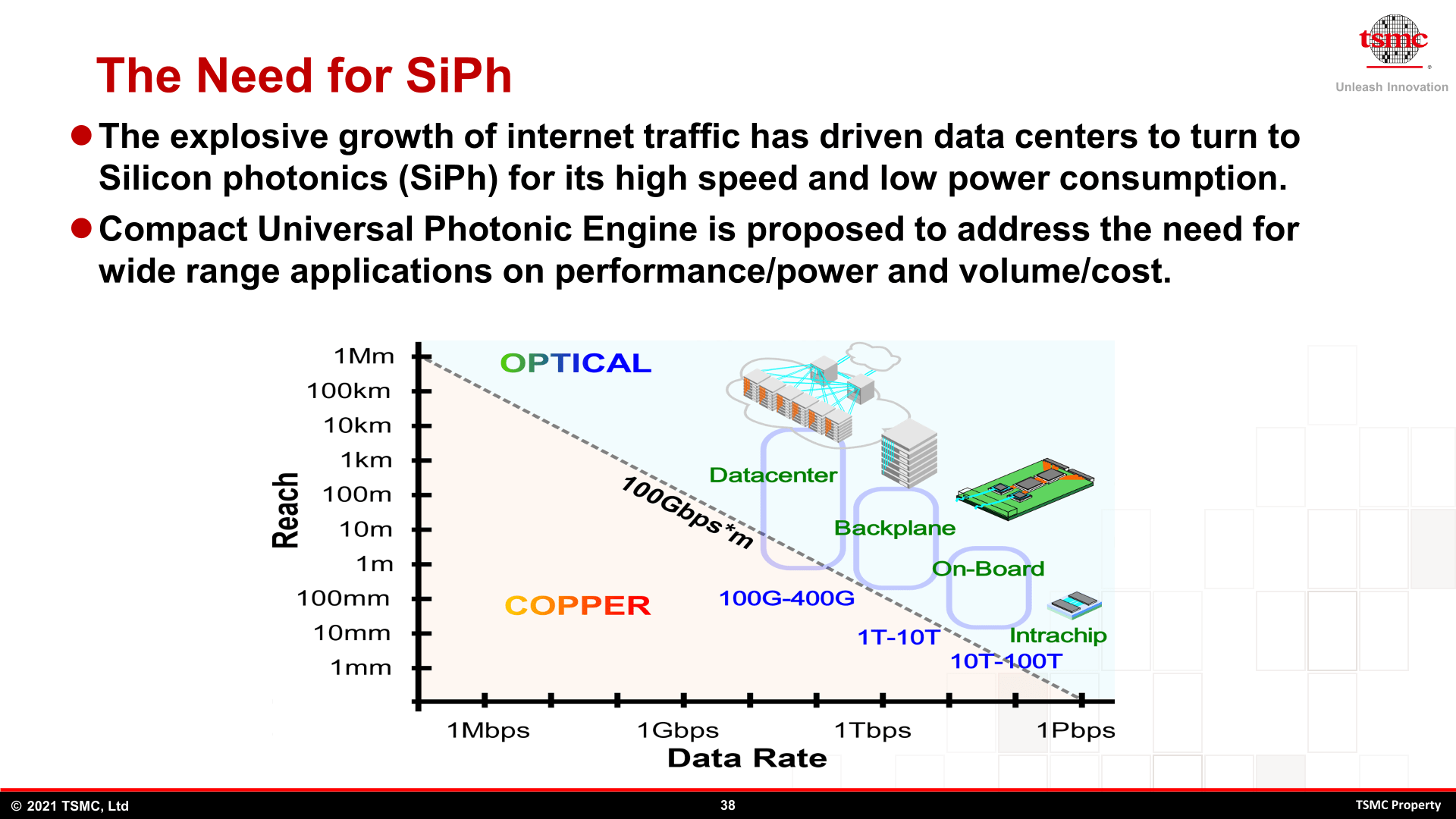

Silicon Photonics

Silicon Photonics ist ein Thema, das auch TSMC auf dem Schirm hat. Stets größere Datenmengen bei geringem Energieverbrauch zu transferieren, ist eine Herausforderung für die kommenden Jahre. Dabei hat sich das Design bereits so verändert, dass ehemals multiple Chips auf ein Package gewandert sind. Das monolithische Design wird angestrebt, ist aber aufgrund verschiedenen Technologiestufen in der Entwicklung oft noch nicht so weit. COUPE wird TSMCs Ansatz dafür. Wie üblich nennt TSMC dabei aber keine Kunden direkt beim Namen, es obliegt diesen selbst, eine Partnerschaft zu benennen.

- Hot Chips 33: Samsung zeigt HBM-PIM und riesige Speichermodule

- Hot Chips 33: IBMs Telum-Architektur setzt auf 32 MB L2-Cache – pro Kern

- Hot Chips 33: Intel Alder Lake steht und fällt mit dem Thread Director

- +7 weitere News