silent-efficiency

Banned

- Registriert

- Aug. 2004

- Beiträge

- 5.253

Hallo,

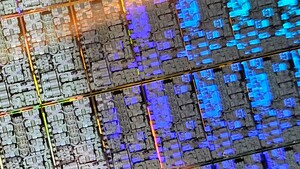

weiß jemand wie hoch der QPI-Takt bei den Clarkdale-Prozessoren ist?

Bei AnandTech wird zwar festgestellt, das die Anbindung des Speichercontrollers über QPI ähnlich wie bei FSB zur schlechteren Leistung führt, aber wie hoch der QPI taktet, wird nirgendwo erwähnt. Auch beim Clarkdale-Test auf CB habe ich nichts dazu gelesen. Weiß den keiner Bescheid, hat keiner bei Intel nachgefragt? oder hab ich irgendwo, irgend etwas übersehen?

weiß jemand wie hoch der QPI-Takt bei den Clarkdale-Prozessoren ist?

Bei AnandTech wird zwar festgestellt, das die Anbindung des Speichercontrollers über QPI ähnlich wie bei FSB zur schlechteren Leistung führt, aber wie hoch der QPI taktet, wird nirgendwo erwähnt. Auch beim Clarkdale-Test auf CB habe ich nichts dazu gelesen. Weiß den keiner Bescheid, hat keiner bei Intel nachgefragt? oder hab ich irgendwo, irgend etwas übersehen?