Power 9: PCI Express 4.0 zuerst für IBMs High-End-CPU

Neue Entwicklerplatinen für IBMs kommende Prozessorgeneration ebnen den Weg für PCI Express 4.0. Big Blue würde mit der Einführung Intel, AMD & Co zuvor kommen, denn die Power 9 sollen noch in diesem Jahr erscheinen. Partnerfirmen stellen bereits entsprechende Ausrüstung zur Verfügung.

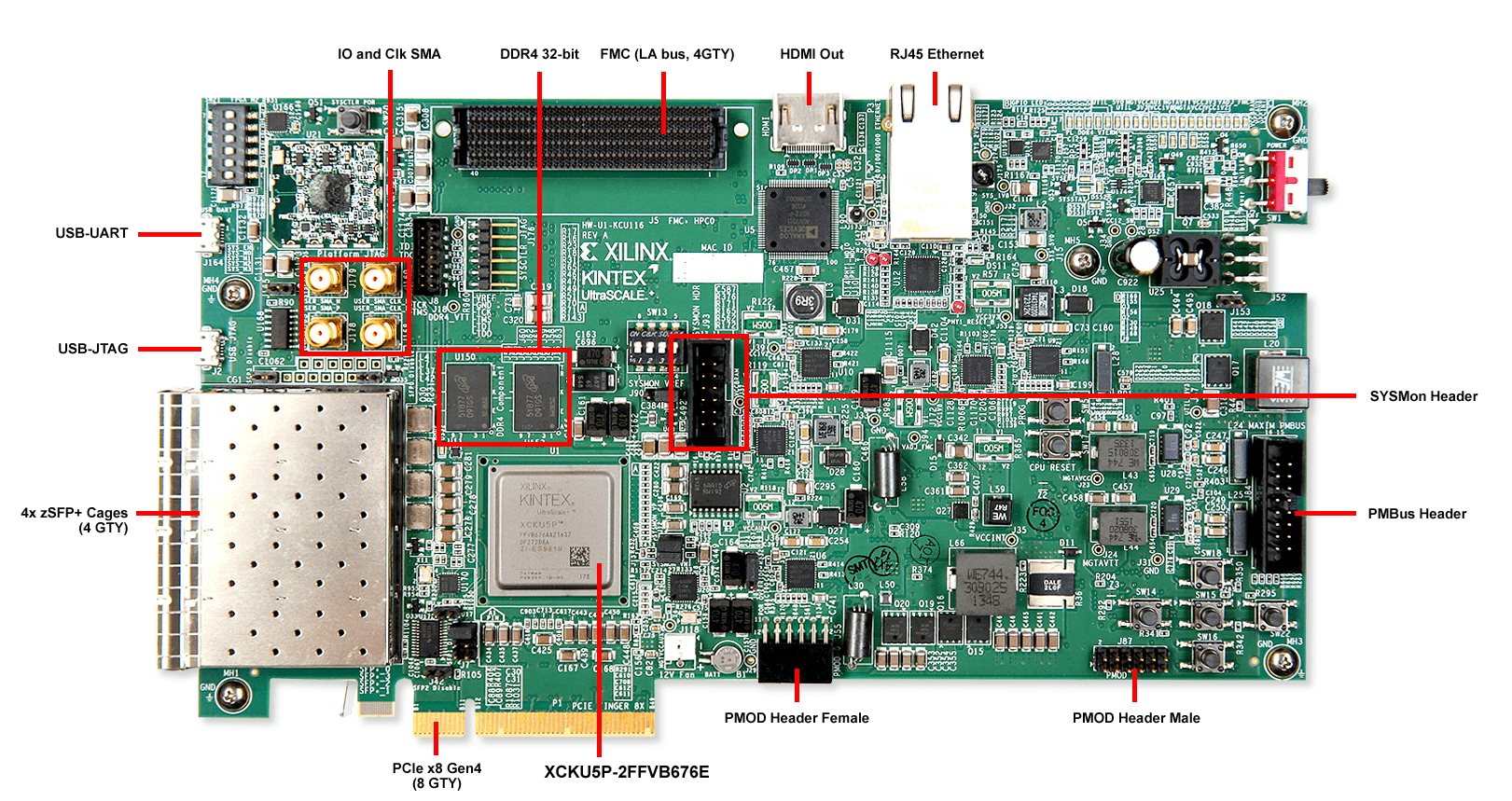

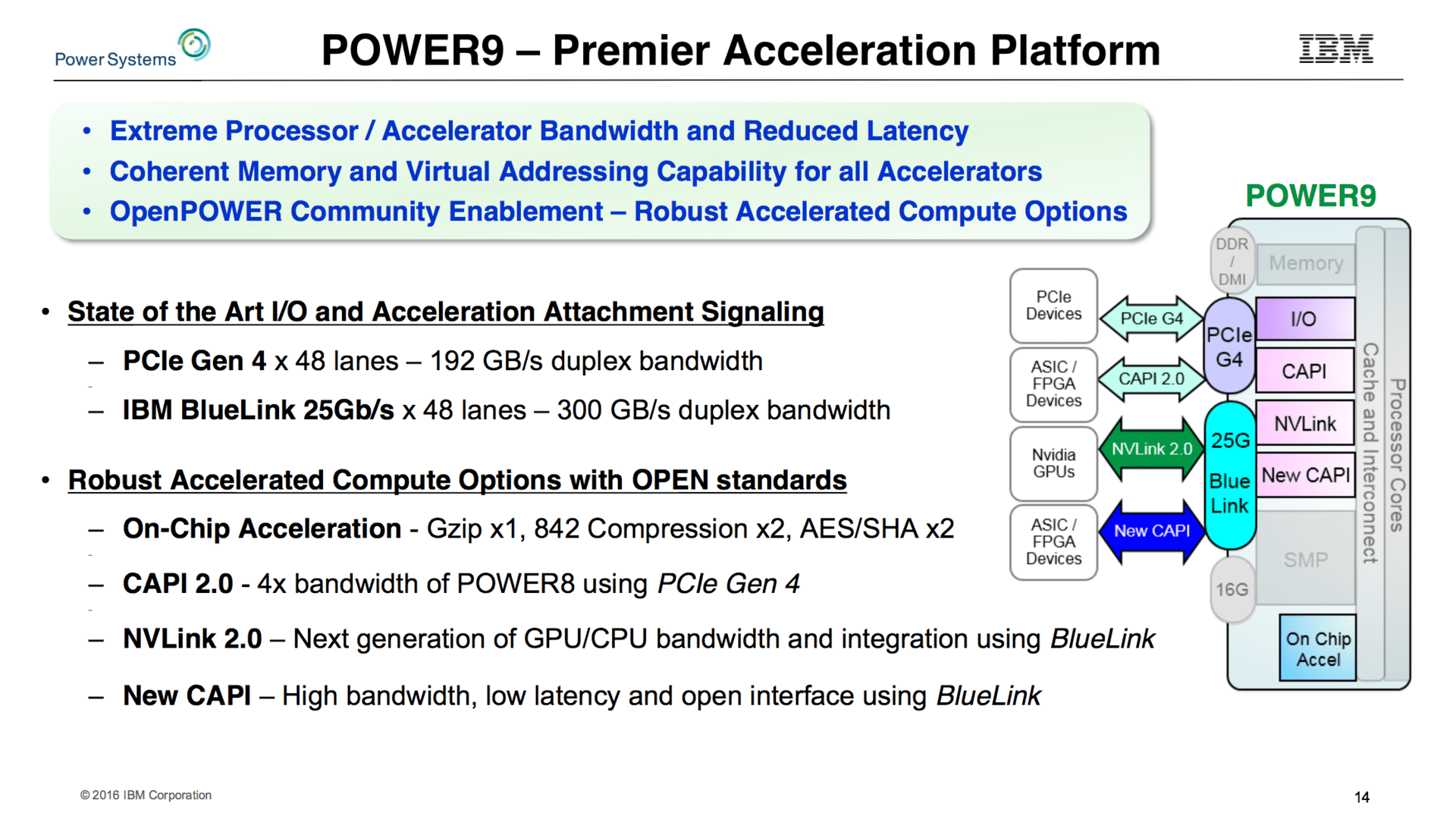

Zum Symposium Hot Chips 28 im August des letzten Jahres stand der neue Server-Prozessor Power 9 von IBM bereits das erste Mal im Blickpunkt. Dabei zeigt sich der Konzern kämpferisch, mit den Konkurrenten mithalten zu können, denn Power 9 bringt alles mit, was zu einem State-of-the-Art-Prozessor für das High-End-Segment gehört. 24 Kerne in neuer Architektur mit vier- oder achtfachem Simultaneous Multithreading (SMT) sowie sehr große Caches (eDRAM). Eine weitere Besonderheit sind die vielfältigen Anschlussmöglichkeiten unter anderem für Nvidias NVLink 2.0 und CAPI 2.0 (coherent accelerator processor interface); eine Schnittstelle, die auf kurzem und sehr schnellem Wege FPGAs, ASICs und selbst zukünftige technische Neuheiten wie Phase Change Memory (PCM) unterstützen kann.

PCI Express 4.0 vorerst nur bei IBM, Intel und AMD hängen zurück

Auch PCI Express 4.0 gehört zum Neuling, gleich in Form von 48 Lanes, die so eine Bandbreite von 192 GByte pro Sekunde im Duplex-Modus bieten können. Auf dem Papier ist PCI Express 4.0 eine Verdoppelung von PCI Express 3.0, pro einzelne Lane liegt die Bandbreite dementsprechend bei 2 statt 1 GT/s. Derzeit ist dies ein Ausstattungsmerkmal, das IBM den Mitbewerbern voraus hat. Und ohnehin läuft es dieses Mal anders als bei den vorangegangenen drei Generationen, in denen Intel und die Grafikhersteller eine treibende Kraft waren – diese hängen jetzt hinter Storage- und Netzwerk-Entwicklern zurück, die dringend jeden Funken an Bandbreite benötigen.

Bei Intel dürfte es vor 2019 kaum Lösungen mit dem neuen PCIe-Standard geben. Nach der Einstellung von Cannon Lake-SP im Server bereits im letzten Jahr zugunsten von Ice Lake-SP könnte dieser in der optimierten 10-nm-Fertigung auch den neuen PCI-Express-Standard bieten. Denn 2018 gibt es nur einen Skylake-SP-Refresh, Codename Cascade Lake, der vermutlich wie Skylake zu Kaby Lake im Desktop ausfällt. Die Ice-Lake-Xeons könnten zudem passen, da eine zeitgleiche Vorstellung von Knights Hill mit bis zu 90 Kernen in verbesserter 10-nm-Fertigung abgeliefert werden soll. Bisher gab es die Xeon Phi auch immer als PCI-Express-Karten.

Auch bei AMD ist der Schritt frühestens in der nächsten Generation denkbar, die ebenfalls erst 2019 erscheinen dürfte. Der aktuelle Ableger Naples alias Epyc soll dann durch einen Prozessor mit dem Codenamen Starship mit bis zu 48 Kernen ersetzt werden, die 7-nm-Fertigung und überarbeitete Zen-2-Kerne könnten die aktuellen 128 PCIe-3.0-Lanes der 32-Kern-CPUs auf den neuesten Stand bringen.

Ethernet-Adapter und FPGAs zuerst

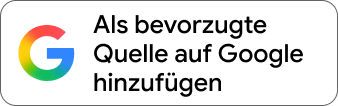

Melanox hat bereits im vergangenen Sommer erste Ethernet-Lösungen für PCIe 4.0 mit 100 Gbit/s gezeigt, Xilinx zieht nun mit der FPGA-Familie UltraScale+ nach. Tests, die von IBM und Xilinx zuvor durchgeführt wurden, offenbarten Datenraten von maximal möglichen 16 GT/s zwischen Power-9-Prototypen und den FPGAs. Die Lieferzeit liegt laut Homepage bei drei Wochen, der Startschuss für finale PCIe-Hardware nach 4.0-Standard ist demnach nicht mehr all zu fern.