BiCS Flash with TSV: Durchkontaktierter 3D‑NAND als Prototyp verfügbar

Was Toshiba bereits bei 2D-NAND nutzte, hält nun auch beim 3D-NAND Einzug: Mehrere übereinander liegende Dies werden mittels TSV-Technik vertikal durchkontaktiert. Gegenüber den klassischen Drahtbonden an den Chip-Rändern soll dies die Leistung steigern und die Leistungsaufnahme senken. Jetzt stehen Prototypen bereit.

Vertikale Verbindung durch die Chips hindurch

TSV steht für Through-Silicon Via und wird im Deutschen Silizium-Durchkontaktierung genannt. Die vertikale Verbindungstechnik wird auch bei DRAM-Chips genutzt und bietet auch hier Vorteile gegenüber dem sogenannten Wire Bonding mit feinen Drähten an den Rändern der übereinander gestapelten Chips (Dies).

16 Mal BiCS2 in einem Package

Bis zu 16 NAND-Flash-Dies hat Toshiba auf diese Weise bereits vor zwei Jahren in einem Chip-Gehäuse (Package) vereint. Was damals ein Novum für 2D-NAND war, wird nun erstmals beim 3D-NAND des Herstellers genutzt. Konkret wird Toshibas BiCS-Flash der zweiten Generation (BiCS2) mit 48 Zellschichten und drei Bit pro Speicherzelle (TLC) mit der TSV-Technik kombiniert. Ebenfalls sollen zunächst bis zu 16 Dies in einem Package übereinander gestapelt werden.

1-TB-Package mit doppelter Energieeffizienz

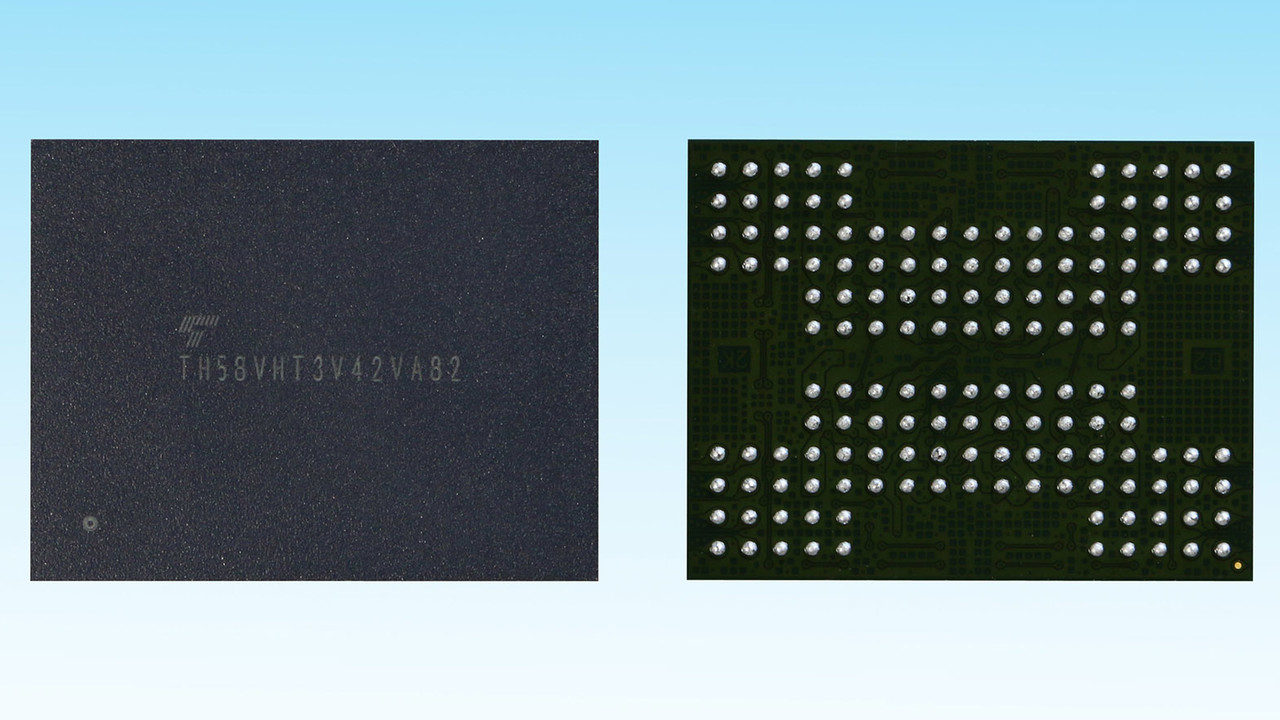

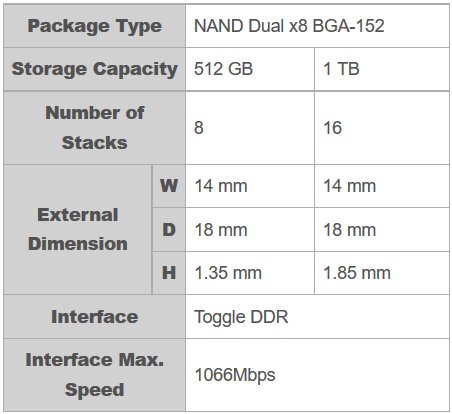

Toshiba prognostiziert einem solchen TSV-Package eine etwa zweimal so hohe Energieeffizienz gegenüber der herkömmlichen Wire-Bonding-Bauweise. Die Datenrate des Toggle-DDR-Interface soll bis zu 1.066 Mbit/s (133 MB/s) erreichen. Mit lediglich 18 × 14 mm (L × B) fallen die Chip-Gehäuse zudem sehr kompakt aus.

Der Hersteller nennt Varianten mit 512 GByte Speicherplatz bei 8 Dies und 1 TByte Speicherplatz mit 16 Dies. Dies würde bedeuten, dass ein Die eine Speicherkapazität von 512 Gbit (64 GByte) besitzt. Die aktuell ausgelieferten 512-Gbit-Dies gehören allerdings bereits der neuen Generation BiCS3 mit 64 Zellschichten an. Folglich produziert Toshiba zusätzlich 512-Gbit-Dies mit nur 48 Lagen und entsprechend größerer Chipfläche.

32 gestapelte Dies für die 100-TB-SSD

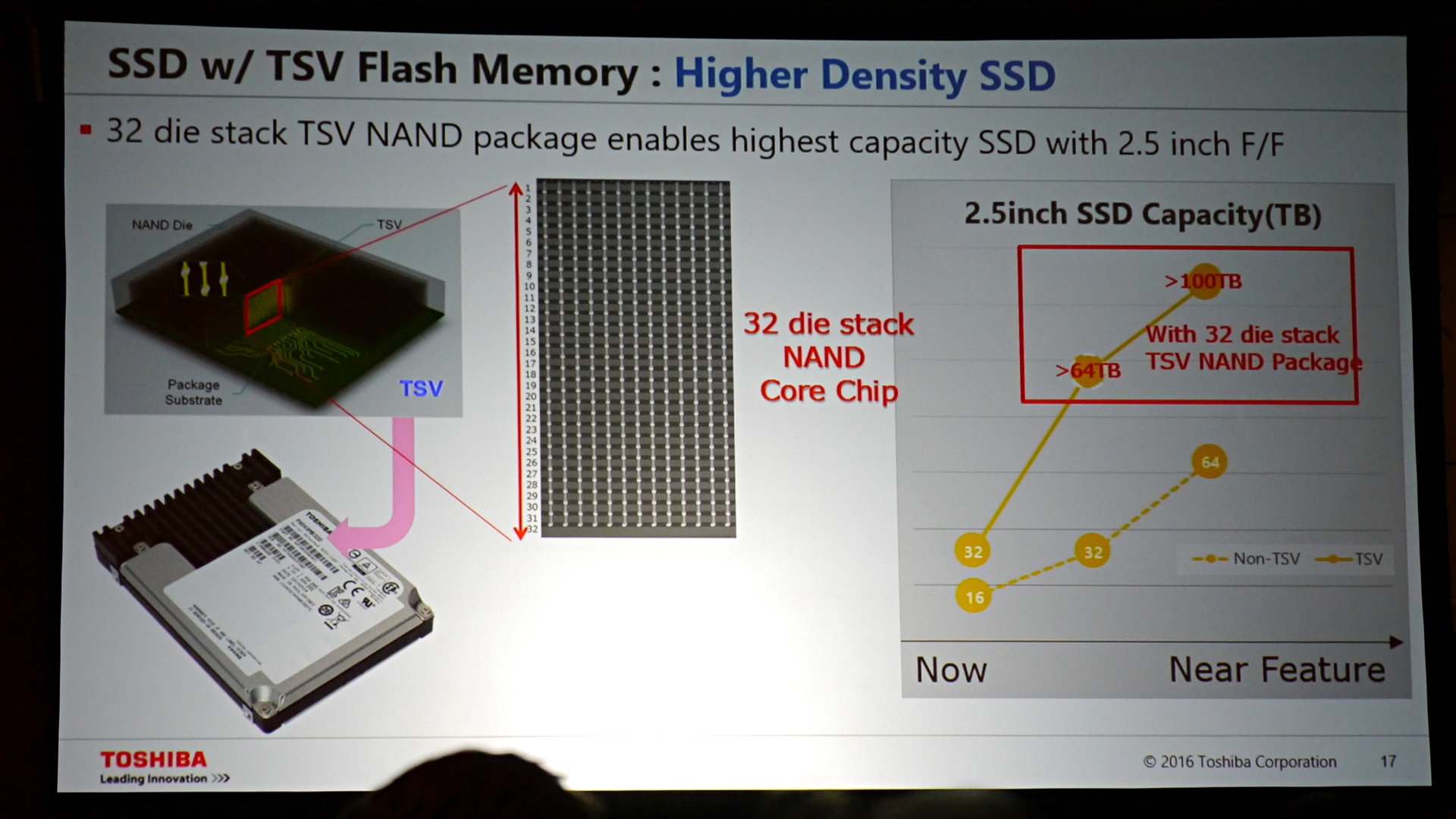

Auf dem letztjährigen Flash Memory Summit hatte Toshiba den 3D-NAND mit TSV bereits angekündigt und dabei nicht nur eine deutlich höhere Leistung, sondern auch noch mehr Speicherplatz pro Package in Aussicht gestellt: Nach 16 Dies sollen es künftig 32 Dies Pro Package werden.

-

100 TByte und mehr im 2,5-Zoll-Format (Bild: Marc Sauter/Golem.de)

100 TByte und mehr im 2,5-Zoll-Format (Bild: Marc Sauter/Golem.de)

Mit 2 TByte pro Package wären einseitig bestückte M.2-SSD mit 4 TByte denkbar, oder aber ein herkömmliches 2,5-Zoll-Modell mit bis zu 32 TByte bei 16 Packages. Spezielle 2,5-Zoll-SSDs mit mehreren Platinen könnten auf diesem Weg eine Speicherkapazität von 100 Terabyte oder mehr erreichen, hatte Toshiba in Aussicht gestellt.

BiCS Flash mit TSV noch Prototyp

Vorerst handelt es sich beim neuen BiCS Flash with TSV um Prototypen, die schon im Juni an Entwickler ausgeliefert wurden und auch auf dem Flash Memory Summit Anfang August präsentiert werden sollen. Die Auslieferung von Samples für die Produktion soll im zweiten Halbjahr folgen.