Hot Chips 33: AMD gibt weitere Einblicke in 3D-Packaging

Zur Hot Chips 33 hat AMD weitere Einblicke in ihre Stapeltechnologie gegeben, die mit kommenden Ryzen und zusätzlichem L3-Cache erstmals genutzt wird. Dabei macht AMD deutlich, dass die Vielfalt an Lösungen, die derzeit entwickelt wird, die Zukunft von Chips in der Industrie prägen wird. Dabei gilt es aber, richtig zu wählen.

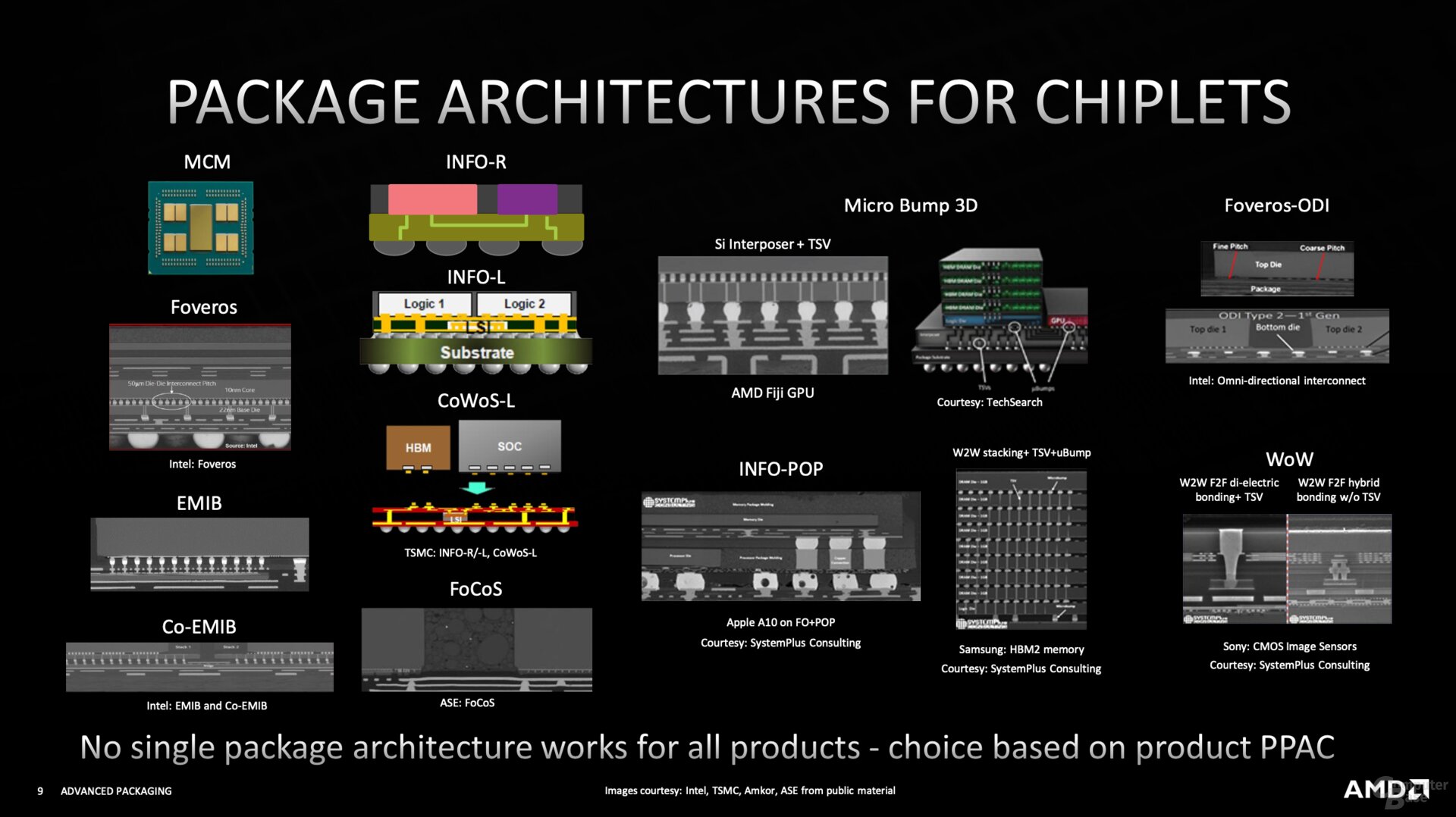

Nicht jede Lösung eignet sich für jedermann, erklärt Raja Swaminathan, Senior Fellow bei AMD für das Packaging gleich zum Auftakt. Doch zweifelsohne gehört dem modularen Design und dazu passendem und abgestimmtem Package die Zukunft, um Moore’s Law fortzuführen. Die Industrie hat das begriffen, vielfältige Lösungen der namhaften Hersteller legen das dar.

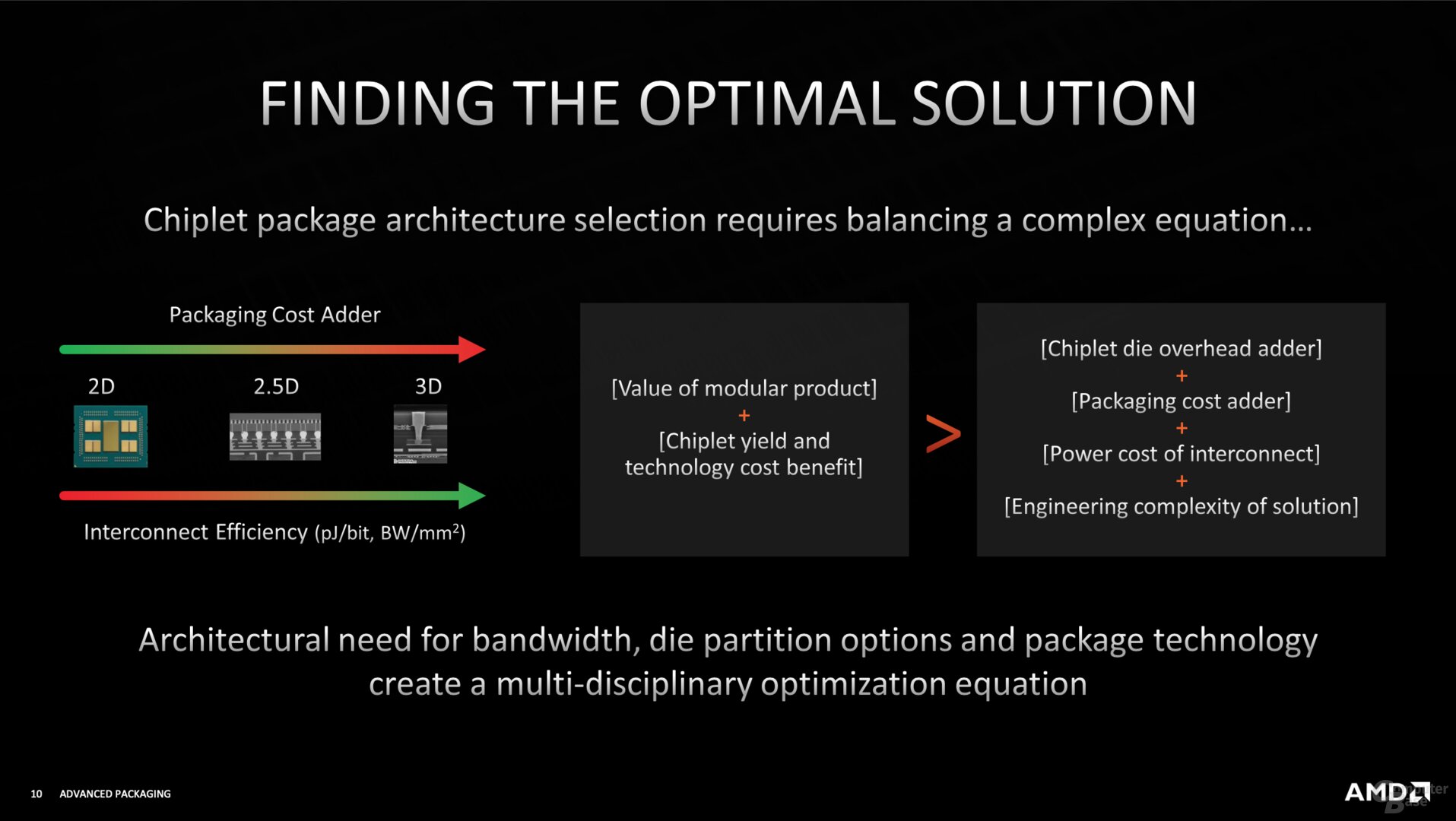

Alle Hersteller müssen die Wirtschaftlichkeit im Blick haben, AMD nennt sie PPAC (power, performance, area and cost). Über diese Punkte muss dann der erdachte Weg gewählt werden, denn nicht alles passt beispielsweise in den günstigen Mainstream-Markt, die Kosten wären einfach zu hoch. AMD wird so beispielsweise die erste Lösung mit 3D-Stacking im gehobenen Segment anbieten, der Hersteller deutet mindestens den Zwölf-Kern-Prozessor an, auch den 16-Kerner dürfte es mit zusätzlichem L3-Cache geben.

AMD hatte zur Enthüllung des 3D V-Cache im Juni bereits erklärt, dass die bisherigen Ryzen 5000 in Bezug auf den CPU-Die bereits auf das Stacking vorbereitet sind. Dafür sind kleine Elemente auf dem Die vorhanden, das Chipbonden erfolgt über einen direkten Kontakt der Kupferschichten, keine zusätzlichen BGA-Kontaktflächen oder ähnliches sind nötig.

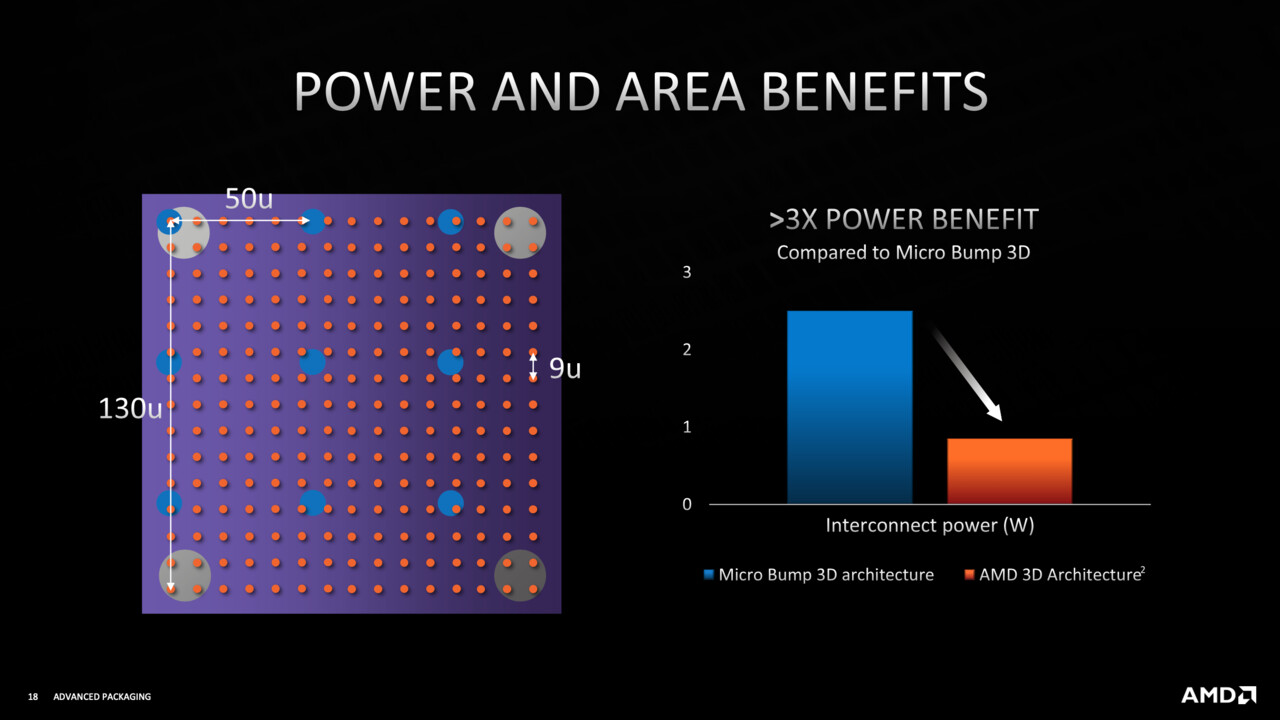

Heute zeigt man im Detail nun, wie diese aussehen: Extrem klein und mit geringstem Abstand von 9 µm der Kontakte sollen sie extrem hohe Signalqualität bei geringer Leistungsaufnahme aufweisen und vor allem gegenüber klassischen Microbumps einen deutlichen Vorteil bieten. Damit würde AMD zusammen mit TSMCs aktueller Technologie auf dem Papier deutlich Intel schlagen, das zukünftige Foveros Direct wird Abstände von „<10 µm“ aufweisen – es kommt aber erst 2023.

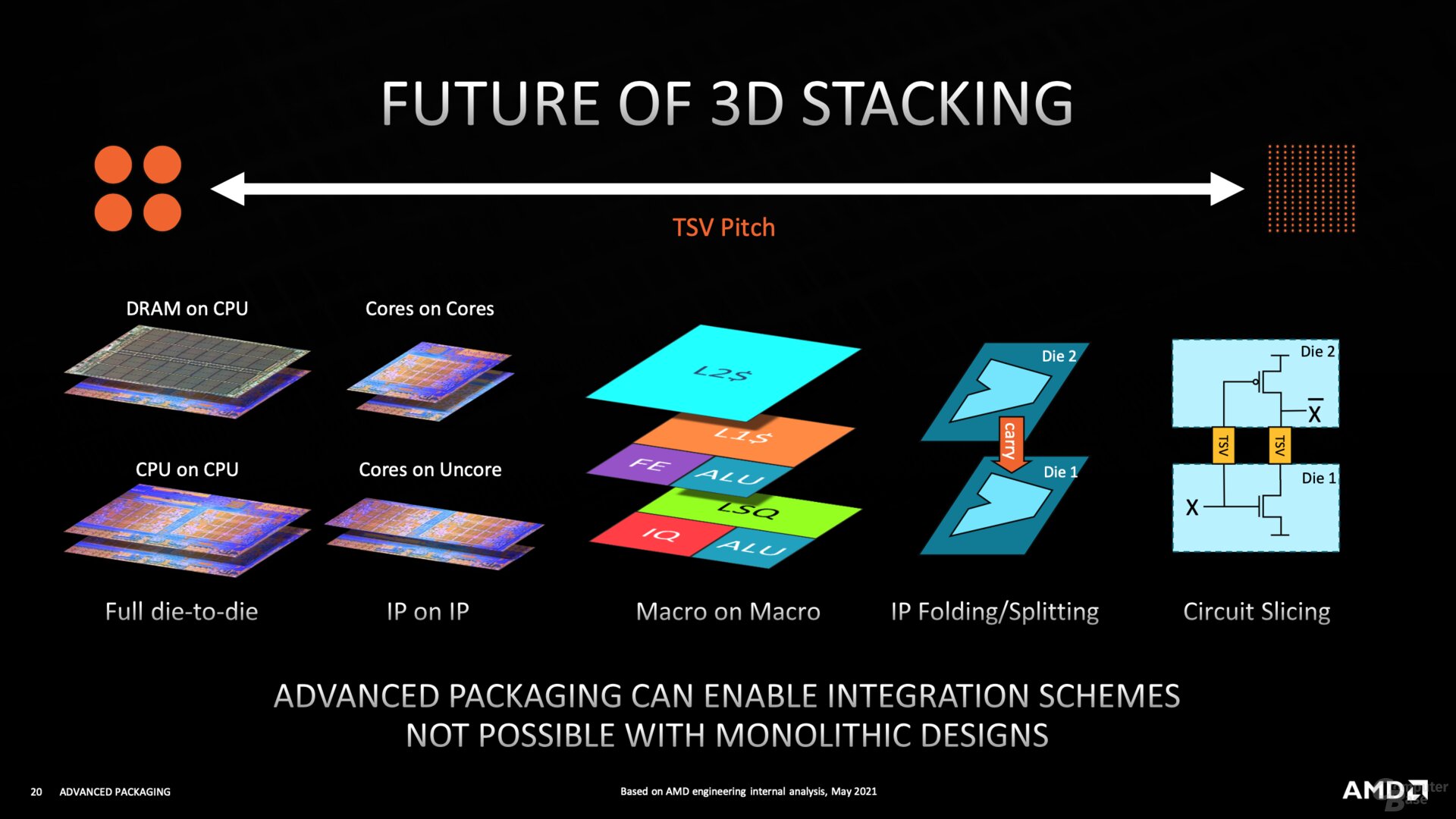

Die Zukunft wird sich weiter in diese Richtung entwickeln, die Möglichkeiten sind auch laut AMD fast endlos. Kosten und Nutzen sowie gewählter Markt dürften am Ende über eine Umsetzung entscheiden. In den kommenden Monaten wird AMD weitere Details zur ersten Lösung bereitstellen.