Das war bei Zen 3/4 so, bei Zen 5 sind die Dies gleich groß. Der eigentliche Cache nimmt zwar nur einen Teil der Fläche ein, aber da der Cache unter dem CCD liegt, braucht der eine ganze Menge TSV um Strom und Daten an den CCD zu übertragen.ThirdLife schrieb:die Tatsache dass das Chiplet per se knapp halb so groß wie die CPU ist und der Rest ja reines "structural silicon" ist und somit auf jedes gefertigte CCD zwei Cache Dies in der Produktion kommen.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

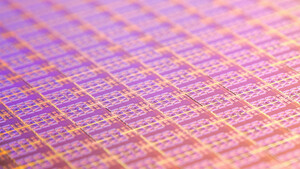

News AMD Zen 6 CCD: 50 Prozent mehr Kerne auf nahezu gleicher Fläche?

- Ersteller MichaG

- Erstellt am

- Zur News: AMD Zen 6 CCD: 50 Prozent mehr Kerne auf nahezu gleicher Fläche?

Panagiotis

Cadet 4th Year

- Registriert

- Juni 2017

- Beiträge

- 92

Auf die X3D Performance gespannt

Wie @stefan92x schon schreibt ist das Cache Die genau so groß wie das CCD. Dies ist notwendig da es gar kein Strukturelles Silizium mehr geben kann weil die Bumps mit denen das ganze mit dem Substrat verbunden wird sich am Cache Die befinden.ThirdLife schrieb:die Tatsache dass das Chiplet per se knapp halb so groß wie die CPU ist und der Rest ja reines "structural silicon" ist und somit auf jedes gefertigte CCD zwei Cache Dies in der Produktion kommen.

Oh, interessant. Bei dir werden nicht direkt die ersten Cores verwendet, sondern Core 3 und 8 des ersten CCDs. Da scheint Windows o. vlt. auch der Chipsatztreiber was bei der Threadverteilung anders zu machen. Kannst du mal 8 Threads testen und die per Taskmanager Affinity-Pinning auf die ersten 8 CPU-Threads pinnen?ThirdLife schrieb:4 Threads und Small FFTs sieht so aus bei mir:

Was man auch sieht, dass die maximale pro Kern Leistungsaufnahme gegenüber meinem 5950X ca. 2W geringer ist. Danke schonmal für den Screenshot.

Edit: Ach, kann es sein, dass der erste CCD der mit dem 3DV-Cache ist? Dann wäre es noch interessant, das ganze für den anderen CCD zu wiederholen, prime95 also auf die 8 Kerne/Threads des zweiten CCDs zu pinnen.

Zuletzt bearbeitet:

Ich halte dagegen. AMD hat es bislang immer vermieden, mehrere IOD aufzulegen. Für SP5 und SP6 sowie die Threadripper-Ableger gibt es nur einen IOD. Und es macht auch viel Sinn für AMD so vorzugehen, denn das spart sehr viel Validierungsaufwand für die jeweilige Plattform.ETI1120 schrieb:Ich bin mir ziemlich sicher dass die Annahme zutrifft, dass AMD unterschiedliche IODs für Classic und Dense CCDs auflegt. Das ergibt sich IMO automatisch aus der unterschiedlichen Shoreline zum IOD von Dense und Classic.

Dann gibt es die Tatsache, dass bereits Kühlkörper für beide Sockel angeboten werden. Und da hat der CS-SP7-1US11 z.B. 118mm x 101.5mm, der CS-SP8-1U S11 kommt auf 118mm x 82mm. Gleiche Breite, aber unterschiedliche Höhe. Was dazu passt, dass der IOD (der die Breite bestimmt) der gleiche ist, die Höhe (die von der Größe der CCDs bestimmt wird) aber bei SP8 nur Classic-CCDs erlauben könnte (was im Umkehrschluss aber nicht heißen muss, dass es auf SP7 nur Dense-CCDs geben muss).

Wenn man davon ausgeht, dass AMD das genau so geplant hat, dann kann man auch davon ausgehen, dass die CCDs eben auch so ausgelegt wurden, dass sie die gleiche Breite haben.

Und jetzt heißt es abwarten, wer von uns mit seiner Vermutung recht hat.

bytzmaster

Cadet 3rd Year

- Registriert

- Jan. 2010

- Beiträge

- 56

was ist daran schwer nen zen 3 zu kühlen? ich hab da den boxedlüfter drauf und die bude rennt seit jahren ohne probleme...und bei dir gehts unter ner wakü nicht? ist deine cpu kaputt?lmfaktor schrieb:Und wie soll man die dann kühlen können? Ist doch jetzt schon mit Ryzen 3 schwierig, selbst mit Wasserkühlung.

Alesis

Commander

- Registriert

- Juni 2022

- Beiträge

- 2.753

Natürlich.beckenrandschwi schrieb:Ja, aber man darf ja träumen...

Mal schauen, vielleicht gibt es auch 12 3D Cache + 24c Kerne, also 64 Threads im Desktop? Vielleicht sogar gleich mit Tiefkühltruhe und 24 Pizzen

Alesis

Commander

- Registriert

- Juni 2022

- Beiträge

- 2.753

@stefan92x

Vielleicht als AM5+?

Vielleicht als AM5+?

@Alesis Der Spaß bräuchte aber einen anderen Formfaktor - und wäre damit definitiv kein AM5(+) mehr, das müsste einen eigenen Namen bekommen. Physisch würde das Package FP11 (also Strix Halo) vielleicht passen, um zwei Dense-CCD mit dem kleinen IOD zu verbinden, aber das hätte auch keine sinnvollen Anschlüsse dafür. Also glaube ich nicht, dass wir das sehen werden.

Alesis

Commander

- Registriert

- Juni 2022

- Beiträge

- 2.753

@stefan92x

Wäre also ein angenommenes 16 Kerne CCD x2 schon zu viel für AM5?

Wäre also ein angenommenes 16 Kerne CCD x2 schon zu viel für AM5?

@Alesis Viel Kaffeesatzleserei während man auf seine Tiefkühlpizza wartet...

Also wenn wir von dieser Nachricht hier ausgehen, wird der 12-Core Zen 6 CCD ein bisschen größer als die alten 8-Core CCDs, gleichzeitig entfällt im Package die Lücke zwischen IOD und CCD, weil diese direkt gekoppelt werden. Das passt also, viel mehr Platz ist aber nicht mehr frei. Würde ein nochmal ein Drittel größeres CCD passen? Ich glaube nicht.

Würde ein 16C-CCD mit weniger Cache passen? Wahrscheinlich. Oder anders gesagt: Ich glaube nur dann an die Möglichkeit für 16C-CCDs auf AM5, wenn diese immer V-Cache mitbringen statt nur als optionale Erweiterung wie derzeit.

Also wenn wir von dieser Nachricht hier ausgehen, wird der 12-Core Zen 6 CCD ein bisschen größer als die alten 8-Core CCDs, gleichzeitig entfällt im Package die Lücke zwischen IOD und CCD, weil diese direkt gekoppelt werden. Das passt also, viel mehr Platz ist aber nicht mehr frei. Würde ein nochmal ein Drittel größeres CCD passen? Ich glaube nicht.

Würde ein 16C-CCD mit weniger Cache passen? Wahrscheinlich. Oder anders gesagt: Ich glaube nur dann an die Möglichkeit für 16C-CCDs auf AM5, wenn diese immer V-Cache mitbringen statt nur als optionale Erweiterung wie derzeit.

Alesis

Commander

- Registriert

- Juni 2022

- Beiträge

- 2.753

@stefan92x

Viel Kaffeesatzleserei während man auf seine Tiefkühlpizza wartet...

Ich kann sowas nicht einschätzen. Deswegen frage ich auch dich. Insofern interpretiere ich deine Ausführung so, dass mit Zen 6 und 12 x 12 Kerne auf einem DIE die Grenze erreicht ist für AM5. Man auch sagen könnte, dass alleine schon deswegen ein 16 Kerne CCD schon vor den ganzen Zen 6 Infos sehr unwahrscheinlich war.

Viel Kaffeesatzleserei während man auf seine Tiefkühlpizza wartet...

Ich kann sowas nicht einschätzen. Deswegen frage ich auch dich. Insofern interpretiere ich deine Ausführung so, dass mit Zen 6 und 12 x 12 Kerne auf einem DIE die Grenze erreicht ist für AM5. Man auch sagen könnte, dass alleine schon deswegen ein 16 Kerne CCD schon vor den ganzen Zen 6 Infos sehr unwahrscheinlich war.

RealMax123

Lieutenant

- Registriert

- Mai 2025

- Beiträge

- 830

Sind zwar intressante Leaks, aber trotzdem wenig wirklich handfeste technischen Fakten.

12 Kerne pro CCD hört man oft und wird wohl deshalb schon stimmen, aber es garantiert niemand das es wirklich 12 vollwertige sein werden. Schon bei den Zen5 Mobilvarianten ist es meist ein Mix aus Zen5 und Zen5c Kernen, und genau das könnte bei Zen6 dann auch bei den Desktop-Versionen der Fall sein.

Und selbst wenn es 12 vollwertige Kerne sind, ist bis jetzt noch nicht gesagt das die Zen6 Kerne vielleicht insgesamt weniger komplex sind als die Zen5 Kerne. Es könnnte sein das man zugunsten des grösseren L3-Cache die L1- und L2-Caches reduzuiert. Oder von den bei Zen5 erstmals eingeführten 6 ALUs pro Kern wieder auf 5 oder 4 ALUs zurückkehrt.

So könnte es dann gut sein das trozt 50% mehr Kerrne und 50% mehr L3-Cache am Ende trotzdem nur 10-20% mehr Leistung rauskommen.

12 Kerne pro CCD hört man oft und wird wohl deshalb schon stimmen, aber es garantiert niemand das es wirklich 12 vollwertige sein werden. Schon bei den Zen5 Mobilvarianten ist es meist ein Mix aus Zen5 und Zen5c Kernen, und genau das könnte bei Zen6 dann auch bei den Desktop-Versionen der Fall sein.

Und selbst wenn es 12 vollwertige Kerne sind, ist bis jetzt noch nicht gesagt das die Zen6 Kerne vielleicht insgesamt weniger komplex sind als die Zen5 Kerne. Es könnnte sein das man zugunsten des grösseren L3-Cache die L1- und L2-Caches reduzuiert. Oder von den bei Zen5 erstmals eingeführten 6 ALUs pro Kern wieder auf 5 oder 4 ALUs zurückkehrt.

So könnte es dann gut sein das trozt 50% mehr Kerrne und 50% mehr L3-Cache am Ende trotzdem nur 10-20% mehr Leistung rauskommen.

Nicht unmöglich, aber doch höchst unwahrscheinlich. Denn bislang gehen alle davon aus, dass das Zen 6 CCD auch für Server-CPUs verwendet wird, und bei denen machen Hybrid-Designs so überhaupt keinen Sinn.RealMax123 schrieb:Schon bei den Zen5 Mobilvarianten ist es meist ein Mix aus Zen5 und Zen5c Kernen, und genau das könnte bei Zen6 dann auch bei den Desktop-Versionen der Fall sein.

Doch.RealMax123 schrieb:Und selbst wenn es 12 vollwertige Kerne sind, ist bis jetzt noch nicht gesagt das die Zen6 Kerne vielleicht insgesamt weniger komplex sind als die Zen5 Kerne.

AMD hat gesagt, dass Venice 70% mehr Leistung als Turin bringen soll (und da wächst die Zahl der Kerne nur um 33%). Das widerspricht deiner Idee drastischRealMax123 schrieb:So könnte es dann gut sein das trozt 50% mehr Kerrne und 50% mehr L3-Cache am Ende trotzdem nur 10-20% mehr Leistung rauskommen.

Dig.Minimalist schrieb:Kann die CPU oder die neuen Chipsätze bitte 8-16 zusätzliche PCIe lanes bieten - selbst PCIe 4.0 wäre ok.

AM5 ist geil, aber der Mangel an PCIe lanes ist derb… bei jedem Mainboard muss man nachschauen wie wirke elektrische lanes wirklich vorhanden sind und wie diese geshared sind

Die CPU? Keine Chance; der Sockel hat nicht genügend Pins für mehr Lanes.

Denkbar wäre, daß ein neuer Chipsatz gleich mit PCIe 5.0 kommuniziert (das würde die Bandbreite immerhin verdoppeln); wenn jetzt noch eine USB 4.0-Fähigkeit in den Chipsatz integriert würde, entfiele auch das unselige Abknapsen von vier (PCIe 5.0-) CPU-Lanes für dein (PCIe 4.0-) USB-Chip.

Dann wären wieder acht PCIe 5.0-Lanes von der CPU frei, und 4n PCIe-Lanes von Chipsatz.

Letztere konkurrieren in der Bandbreite zwar allesamt miteinander und mit der gesammelten I/O-Leistung, aber zumindest wäre die Summe dieser Bandbreite dann nicht mehr PCIe 4.0 x4, sondern PCIe 5.0 x4.

RealMax123

Lieutenant

- Registriert

- Mai 2025

- Beiträge

- 830

24 Nutzbare PCIe Lanes sind eigentlich nicht wenig sondern schon ganz ordentlich, solange der Chipsatz flexibel genug ist.

Direktanbindung an CPU:

PCIe x16 Slot (konfigurierbar auf 16 oder 8 PCIe 5.0 Lanes)

PCIe x16 Slot (konfigurierbar auf 8 oder 4 PCIe 5.0 Lanes)

m.2 Slot (4 PCIe 5.0 Lanes)

m.2 Slot (4 PCIe 5.0 Lanes)

Anbindung an Chipsatz

PCIe x1 Slot (1 PCIe 4.0 Lane)

m.2 Slot (4 PCIe 4.0 Lane)

Direkt an der CPU betrieben könnte man dann wahlweise:

1 Grafikkarte mit 16 PCIe 5.0 Lanes

zweiter x16 Slot leer

2 m.2 SSDs mit je 4 PCIe 5.0 Lanes

1 Grafikkarte mit 16 PCIe 5.0 Lanes

1 sonstige Karte mit 4 PCIe 5.0 Lanes

1 m.2 SSDs mit 4 PCIe 5.0 Lanes

zweiter m.2 Slot leer

1 Grafikkarte mit 8 PCIe 5.0 Lanes

1 weitere Grafikkarte oder sonstige Karte mit 8 PCIe 5.0 Lanes

2 m.2 SSDs mit je 4 PCIe 5.0 Lanes

dazu dann jeweils noch über den Chipsatz

1 weitere PCIe x1 Karte (1 PCIe 4.0 Lane)

1 weitere m.2 SSD (4 PCIe 4.0 Lanes)

Das reicht doch locker!

Direktanbindung an CPU:

PCIe x16 Slot (konfigurierbar auf 16 oder 8 PCIe 5.0 Lanes)

PCIe x16 Slot (konfigurierbar auf 8 oder 4 PCIe 5.0 Lanes)

m.2 Slot (4 PCIe 5.0 Lanes)

m.2 Slot (4 PCIe 5.0 Lanes)

Anbindung an Chipsatz

PCIe x1 Slot (1 PCIe 4.0 Lane)

m.2 Slot (4 PCIe 4.0 Lane)

Direkt an der CPU betrieben könnte man dann wahlweise:

1 Grafikkarte mit 16 PCIe 5.0 Lanes

zweiter x16 Slot leer

2 m.2 SSDs mit je 4 PCIe 5.0 Lanes

1 Grafikkarte mit 16 PCIe 5.0 Lanes

1 sonstige Karte mit 4 PCIe 5.0 Lanes

1 m.2 SSDs mit 4 PCIe 5.0 Lanes

zweiter m.2 Slot leer

1 Grafikkarte mit 8 PCIe 5.0 Lanes

1 weitere Grafikkarte oder sonstige Karte mit 8 PCIe 5.0 Lanes

2 m.2 SSDs mit je 4 PCIe 5.0 Lanes

dazu dann jeweils noch über den Chipsatz

1 weitere PCIe x1 Karte (1 PCIe 4.0 Lane)

1 weitere m.2 SSD (4 PCIe 4.0 Lanes)

Das reicht doch locker!

Wenn es nicht Gerüchte/Leaks gäbe, die besagen dass es zwei verschiedene IODs gibt, und das eine Leak nicht durch den richtigen Wert für die DIMMs eine gewisse bestätigung erfähren hätte, wäre ich vollkommen bei Dir.stefan92x schrieb:Ich halte dagegen.

Das Argument mit dem Validierungsaufwand verwende ich auch sehr gerne wenn es darum geht warum AMD im Desktop das IOP für zwei Generationen verwendet.stefan92x schrieb:AMD hat es bislang immer vermieden, mehrere IOD aufzulegen. Für SP5 und SP6 sowie die Threadripper-Ableger gibt es nur einen IOD. Und es macht auch viel Sinn für AMD so vorzugehen, denn das spart sehr viel Validierungsaufwand für die jeweilige Plattform.

Also das ist so richtig.

Allerdings muss es nicht so bleiben wie es war. Siehe die Anordnung Cache Chiplet und CCD bei den X3D Versionen. Es war zwei Mal so und es gab viele gute Argumente warum es so bleibt. Es gab nur ein einziges Argument es zu ändern und diese eine Argument gab eben den Ausschlag. Die Wärme abzuführen ist nun Mal das ein und alles beim 3D Stacking.

Auch dem will ich nicht widersprechen.stefan92x schrieb:Dann gibt es die Tatsache, dass bereits Kühlkörper für beide Sockel angeboten werden. Und da hat der CS-SP7-1US11 z.B. 118mm x 101.5mm, der CS-SP8-1U S11 kommt auf 118mm x 82mm. Gleiche Breite, aber unterschiedliche Höhe. Was dazu passt, dass der IOD (der die Breite bestimmt) der gleiche ist, die Höhe (die von der Größe der CCDs bestimmt wird) aber bei SP8 nur Classic-CCDs erlauben könnte (was im Umkehrschluss aber nicht heißen muss, dass es auf SP7 nur Dense-CCDs geben muss).

Aber hast Du dir Mal angesehen welche Dimensionen die Kühlerkörper für SP5 und SP6 haben?

Ich habe gefunden:

SP5: 118 x 92,5 mm²

SP6: 118 x 78,9 mm²

Könnte es sein dass AMD auf den 75,4 mm Basis bleibt, aber nun, die bisher schmalere Seite (SP3=SP6=58,5 mm; SP5= 72 mm) bei SP7 nun die breitere Seite (d. h. >75,4 mm) ist?

Möglich, wenn es auch sicher ziemlich spaßig wird das hinzubekommen.stefan92x schrieb:Wenn man davon ausgeht, dass AMD das genau so geplant hat, dann kann man auch davon ausgehen, dass die CCDs eben auch so ausgelegt wurden, dass sie die gleiche Breite haben.

Ist es überhaupt sinnvoll, dass beide Dies dieselbe Shore Line zum IOD haben? Lass mich die Frage erläutern:

So wie ich die Die Shots von Strix Halo interpretiere wird fast komplette Shoreline zum IOD für das Sea of Wires des Infinity Fabric Advanced Packaging benötigt. Die Shore Line legt also fest welche Bandbreite die Anbindung zwischen IOD und CCD hat.

Also ist die eigentliche Frage, ist es sinnvoll die CCDs mit 12 und mit 32 Kerne mit derselben Bandbreite anzuschließen?

Ich sehe jetzt nicht, dass AMD die Dense CCD für die eher gemächlichen Aufgaben verwenden will. Wenn die Dense CCDs für Mainstream Server vorgesehen sind, kann AMD nicht mit der Bandbreite knausern. D. h. das Dense CCD muss mit mehr Bandbreite angeschlossen werden, benötigt also eine größere Shore Line.

Natürlich kann man das Classic CCD was die Anbindung anbelangt auch überdimensionieren. Aber das schleppt AMD auf dem Desktop mit, wo beide CCD sehr viel Shoreline belegen. Sinnvoll wäre es nur wenn das Infinity Fabric auf dem Desktop niedriger takten würde.

Bei Zen 2 war es ein Speicherkanal je CCD. Jeder Speicherkanal hatte eine Bandbreite 23,5 GB/s (DDR4-2933). Die IFoP-Links hatten eine Bandbreite von ca. 55 GB/s was genug war um asym das metrische Lastverteilungen auszugleichen.

Als ich gestern Mal das ganze mit MRDIMM DDR5-12800 durchgerechner habe ist mir ganz schummrig geworden.

Also für mich ergibt es Sinn konsequent zwei Plattformen zu machen

- SP8 mit 8 Speicher-Kanäle, maximal 8 CCDs a 12 x Zen 6 Classic und einem IOD dessen Shoreline für diese Anforderung abgestimmt ist. Die CCDs passen dann ohne Probleme für den Desktop

- SP7 mit 16 Speicher-Kanälen maximal 8 CCDs a 32 x Zen 6 Dense und einem IOD dessen Shoreline auf diese Anforderung abgestimmt ist.

Ob ich recht habe oder nicht interessiert mich nicht wirklich.stefan92x schrieb:Und jetzt heißt es abwarten, wer von uns mit seiner Vermutung recht hat.

Der Spaß ist beim vervollständigen des Puzzles. Wenn ich danebenliege, lerne ich etwas dazu.

So wie ich Deine Posts verstehe, siehst Du das genauso.

crustenscharbap

Rear Admiral

- Registriert

- Jan. 2008

- Beiträge

- 5.477

Genau. AMD begründet, dass RDNA 3.5 kein FSR 4 bekommt, weil diese APUs nicht über eine KI Funktion verfügen. Dabei haben sie eine NPU, haben 50TOPs und heißen sogar KI. Das ist für mich totaler Schwachsinn. Die sollen FSR4 frei geben, sonst wird meine nächste APU ein Intel.Alesis schrieb:Irgendwie verstehe ich deinen Kommentar nicht.

Gorgon Point wird als APU in den Desktop kommen und natürlich als zB 4 + 6c Kerner eine 50TOPS NPU haben, mit 768 RDNA 3.5 Shader insgesamt 73TOPs bieten.

beckenrandschwi

Commander

- Registriert

- Aug. 2004

- Beiträge

- 2.266

Naja, mein Dionsaurer hat 44c/88T:Alesis schrieb:Natürlich.Aber 2 x 12 Kerne, also 48 Threads und die 52 Kerne/Threads mit Nova sind mehr als genug im Desktop.

Kerne kann man NIE genug haben. Wobei ein wenig mehr Single Core Performance schon nicht schlecht wäre.

Ähnliche Themen

- Antworten

- 51

- Aufrufe

- 6.357