Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

News Hot Chips 2023: AMD verrät wenig mehr über „Siena“ und verwirrt

- Ersteller MichaG

- Erstellt am

- Zur News: Hot Chips 2023: AMD verrät wenig mehr über „Siena“ und verwirrt

@stefan92x big.BIGGER wurde einmal in den Raum geworfen, hat mir gefallen^^

Ich sehe dies grundlegend anders. Das c wie cloud von AMD ist ein Marketing Gag, Efficiency Cores und Performance Cores sind seit langem eingeführte Begriffe. In diesem Zusammenhang interessiert es nicht wie AMD und Intel jeweils die Kerne umsetzen, die die Effizient Rolle haben.stefan92x schrieb:Ich denke wir sollten die Begriffe P- und E-Kern nicht für AMD verwenden, da das für unterschiedliche Architekturen verwendet wird bei Intel.

In der internen Konfiguration verwendet AMD Performance und Efficiency Core.

Also sehe ich keinen Grund bei AMD nicht P und E zu verwenden, wo doch bei AMD die E Kerne effizienter als die P Kerne sind und die P Kerne mehr Performance bringen.

Im übrigen finde ich ist es irrelevant was Intel macht, weil das ganze zuerst von Arm umgesetzt wurde und AFAIK Arm auch die Terme Performance Core und Efficiency Core geprägt hat.

AFAIK hat Arm auch CPUs herausgebracht die denselben Kern für big.LITTLE verwendet haben. Arm hat ein Trademark auf big.Little und deshalb ist die korrekte Bezeichnung Hybrid CPU.

Es geht bei Zen 4c nicht nur um ein kompaktes Design, es geht ebenso um eine höhere Effizienz. Die Effizienz ist essentiell für die Cloudanbieter und für die Anwendungen bei Telekom und Edge.stefan92x schrieb:Bei AMD gibt es einfach nur ein Standarddesign und ein kompaktes Design (mit weniger Taktpotential und ohne Option zum Stapeln von Cache) des gleichen Kerns.

Und beim Design ist AMD IMO genau anders herum vorgegangen als Du es andeutest. AMD hat festgelegt mit welcher Frequenz diese Kerne betrieben werden, und hat dann auf Fläche und Power optimiert. Da der L3-cache bei der Rechen-Lasten für den Zen 4c entworfen wurde, nicht sonderlich relevant ist, spielt es keine Rolle, dass er je Kern halbiert wurde.

Wenn die Leaks zu Strix Point zutreffen, dann werden sich E und P Kerne bei Zen 5 deutlicher unterscheiden als bei Zen 4.

Hört sich witzig an, geht aber am Kern der Sache vorbei. Viele vergessen immer wieder wie groß Golden Cove im Vergleich zu Zen 3 ist.bad_sign schrieb:@stefan92x big.BIGGER wurde einmal in den Raum geworfen, hat mir gefallen^^

Die Kerne von AMD sind nicht sonderlich fett.

Ich find Bulh1t_Buster hat das sehr gut beschrieben:

https://twitter.com/Bullsh1t_buster/status/1664696479158550528

Ergänzung ()

Ja das kommt davon, wenn man beim Schreiben nicht mal einen Schritt zurück macht und in Ruhe überlegt was alles bekannt ist. Denn rennt man so wie ich einseitig in die Schiene Die-Fläche kleiner machen.bad_sign schrieb:Und dann kommt AMD und geht in die Vollen

Klar, ich bin nur verblüfft, dass AMD ausgerechnet Namen von ital. Städten anführt, "Siena" ist ja eher fast noch ein Dorf. Bergamo hat nicht einmal so viele Einwohner wie mein Bezirk hier in Rom. Wenn Amis auf ital. reden, auch die mit Migrationshintergrund, da muss ich immer schmunzeln als Muttersprachler.Nitschi66 schrieb:@juwa

Ja, im italienischen. Das interessiert aber das amerikanische Unternehmen AMD nicht, die den englischen Namen der Stadt nehmen ;-)

Auch wenn das berits jemand beantwortet haben sollte: Die SAP Zertifizierung gibt es schon lang. Nur bin ich mir nicht mehr sicher, wie es speziell bie SAP HANA aussieht.Unnu schrieb:Hat AMD eigentlich jetzt endliche ihre SAP-Zertifizierung durch?

- Registriert

- Feb. 2009

- Beiträge

- 11.083

ETI1120 schrieb:Die Threadripper-Varianten, die aus diesem Bauskasten abgeleitet werden, werden auch noch kommen.

Wäre das nicht gerade für Threadripper die Kombination schlechthin?ETI1120 schrieb:Unter linker Quadrant: Zen 4 - Ziel höhere Performance

Unter rechter Quadrant: Zen 4 c - Ziel niedrigere Power

1x CCD mit Zen 4 für Performance und 2-3 CCDs mit Zen4c die effizienter Takten.

Der 7950 überhitzt ja mit 2 CCDs schon komplett.

Sowas wie der 7950X3D nur halt nicht mit 3D Cache sondern 8 TurboCores.

Also eine 8 Kern Chiplet wo sehr hoch taktet weil Cache gegen Takt getauscht und einmal normale Menge Cache und Kerner weniger getaktet.Ist auch ne Option.Ob man da was merkt bei der Rohleistung wer weis.Aber ich bin mir da echt nicht sicher ob das AMD so machen würde.

Oder halt gleich 2 Verianten.Einmal normal und einmal komplett mit reduzieren L3 Cache dafür aber alle Kerne auf einem Die.Oder doch mal einen 32 Kerner mit reduzierten L3 Cache aber auf 2 Chiplet Verteilt.Ob das AMD sowas machen wird,wer weis.Wäre durchaus interessant sowas.Sparen würde zwar AMD auch was aber wie viele USer sich sowas kaufen würden,sicher bin ich mir da echt nicht.

Oder halt gleich 2 Verianten.Einmal normal und einmal komplett mit reduzieren L3 Cache dafür aber alle Kerne auf einem Die.Oder doch mal einen 32 Kerner mit reduzierten L3 Cache aber auf 2 Chiplet Verteilt.Ob das AMD sowas machen wird,wer weis.Wäre durchaus interessant sowas.Sparen würde zwar AMD auch was aber wie viele USer sich sowas kaufen würden,sicher bin ich mir da echt nicht.

Es gibt da eine Funktion die nennt sich "Nutzer ignorieren". Dann werden dir seine Beiträge ausgeblendet. Aber mit solch diffamierenden Beiträgen wie deinem, ist dann auch niemandem geholfen. Leben und leben lassen.B3rry schrieb:Was wird das eigentlich von dir ? Musst du dein Unwissen wirklich überall hinschreiben ?

ETI1120 schrieb:Das komische bei Phoenix 2 ist, dass er aus dem Preisvergleich wieder verschwunden ist.

Dass er drinnen war, war wohl ein Fehler, und Phoenix 2 gibt's noch nicht in Produkten.

Warten wir erst Mal ab wann Phoenix im Desktop kommt, bei Phoenix 2 bin ich skeptisch.

Naja, kann ich mir schon vorstellen, als Billigprozessor in der Nachfolge des Ryzen 5500 vielleicht. Wobei man die Taktbeschraenkung des Zen4c auf dem Desktop staerker spueren wird als in einem U-Laptop, das wuerde dagegen sprechen.

Nope. Also Danke.janer77 schrieb:Auch wenn das berits jemand beantwortet haben sollte: ... wie es speziell bie SAP HANA aussieht.

Hm, HANA wäre ja das interessante, dort wird das Geld verdient. Vor allem zukünftig.

Nur dass der Gedanke unausgegoren und weitgehend Blödsinn ist.latiose88 schrieb:Das war nur ne Vermutung wie AMD das Aufbauen könnte um Verbindungen zu reduzieren.Bzw um die Fläche zu reduzieren in dem ja die einen weniger L3 Cache haben und die anderen teile mit 3d Cache ganz viel.

Wenn du viele Kerne kaufst, brauchst du die meistens auch, d.h. der Cache wird von den jeweiligen Kernen benötigt.

Für "viel Cache mit wenig Kernen" gibt es passende Modelle.

Davon abgesehen vergessen die Leute gerne, dass Cache-Koherenz nicht kostenlos ist und die Caches auch einen Interconnect brauchen. Wenn ich am Ende kaum schneller bin, als wenn ich auf den RAM zugreife, kann ich mir den riesigen Aufwand (und die Kosten) sparen.

Das wurde im Update ~30 Minuten vor deinem Beitrag verneint.ETI1120 schrieb:Mit Siena kommt einen neues IOD hinzu und AMD kann daraus mit Zen 4c und Zen 4 wieder zig Produkte ableiten.

Ich vermute den üblichen Grund: Kosten/Nutzen-Relation.

Mit den APUs hat AMD eine Roadtour durch Carlifornien gemacht. In den 2000er waren es Mal Rennstrecken. Bei den GPUs waren es Mal Inseln und aktuell Sterne. Beim Client waren es Maler. 2017 hat sich die Serverabteilung von AMD hat sich 2017 auf eine Tour durch Italien begeben.juwa schrieb:Klar, ich bin nur verblüfft, dass AMD ausgerechnet Namen von ital. Städten anführt, "Siena" ist ja eher fast noch ein Dorf.

Ergänzung ()

Die Zen 4c sind nur bei niedrigen Taktraten effizienter als Zen 4.Haldi schrieb:Wäre das nicht gerade für Threadripper die Kombination schlechthin?

1x CCD mit Zen 4 für Performance und 2-3 CCDs mit Zen4c die effizienter Takten.

Wenn man die Taktfrequenz erhöht kommt sehr schnell der Punkt an dem Zen 4 bei gleicher Taktrate effizienter ist. Und ziemlich bald danach wird der Punkt kommen an dem nichts mehr geht.

Ob es bei Workstation Zen 4c zu verwenden Sinn ergibt kann ich nicht beurteilen. Ich denke aber eher nicht.

Zuletzt bearbeitet:

Aber den Fehler gab es gleich 4 Mal und irgendwie hat das auch zu gut zur damaligen Diskussion über Hybrid CPUs gepasst. Die Frage ist was war der Fehler?Hatten die Geräte gar kein Phoenix 2 oder haben die Händler Geräte gelistet, die sie noch gar nicht hätten listen dürfen.mae schrieb:Dass er drinnen war, war wohl ein Fehler, und Phoenix 2 gibt's noch nicht in Produkten.

Grundsätzlich war es merkwürdig, dass diese Notebooks im Preisvergleich aufgetaucht sind, obwohl Phoenix 2 nicht Mal angekündigt geschweige denn offiziell vorgestellt war.

Das denke ich auch.mae schrieb:Naja, kann ich mir schon vorstellen, als Billigprozessor in der Nachfolge des Ryzen 5500 vielleicht. Wobei man die Taktbeschraenkung des Zen4c auf dem Desktop staerker spueren wird als in einem U-Laptop, das wuerde dagegen sprechen.

Zu beachten ist außerdem, dass Phoenix 2 angeblich nur ca 23 % weniger Fläche als Phoenix hat.

foofoobar

Rear Admiral

- Registriert

- Dez. 2011

- Beiträge

- 5.599

Works as designed.ETI1120 schrieb:Die Zen 4c sind nur bei niedrigen Taktraten effizienter als Zen 4.

Wenn man die Taktfrequenz erhöht kommt sehr schnell der Punkt an dem Zen 4 bei gleicher Taktrate effizienter ist. Und ziemlich bald danach wird der Punkt kommen an dem nichts mehr geht.

Ich bin eben kein Schnellschreiber,Nagilum99 schrieb:Das wurde im Update ~30 Minuten vor deinem Beitrag verneint.

Bei einem zweiten Die wäre der einzige Nutzen eine Kosteneinsparung gewesen.Nagilum99 schrieb:Ich vermute den üblichen Grund: Kosten/Nutzen-Relation.

Und eine relevante Kostenersparnis ist wohl nicht gegeben.

ETI1120 schrieb:Aber den Fehler gab es gleich 4 Mal und irgendwie hat das auch zu gut zur damaligen Diskussion über Hybrid CPUs gepasst. Die Frage ist was war der Fehler?Hatten die Geräte gar kein Phoenix 2 oder haben die Händler Geräte gelistet, die sie noch gar nicht hätten listen dürfen.

Meine verschwommene Erinnerung meint, dass ich damals auf der Homepage des Herstellers eines Laptops geschaut habe, und der Laptop dort mit Phoenix (ohne 2) beschrieben war. Also zumindest zu dem Zeitpunkt gab's den Fehler offenbar nur in Geizhals. Inwieweit der urspruenglich auf einer zeitweilig fehlerhaften Angabe beim Laptop-Hersteller beruht, oder woher der auch immer kam, darueber kann man nur spekulieren.

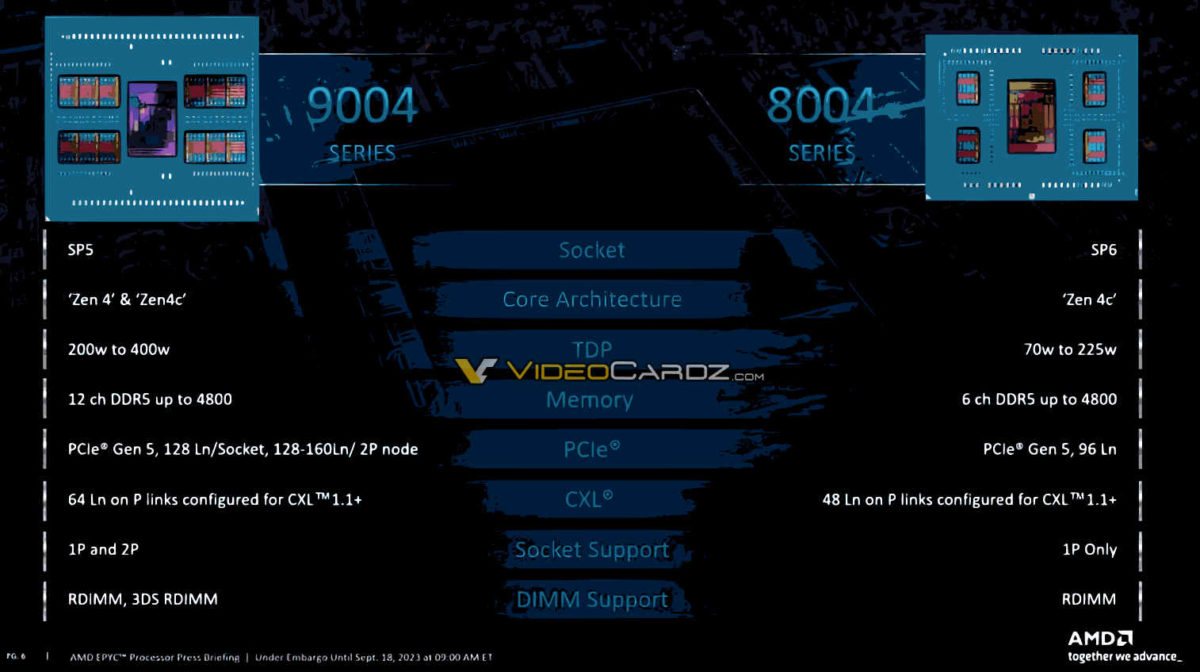

https://videocardz.com/newz/amd-lau...pu-series-up-to-64-zen4c-cores-and-sp6-socket

Videocardz hat es jetzt geleakt:

Siena gibt es NUR mit ZEN4c. Damit auch nur 4 CCDs.

Videocardz hat es jetzt geleakt:

Siena gibt es NUR mit ZEN4c. Damit auch nur 4 CCDs.

Ähnliche Themen

- Antworten

- 28

- Aufrufe

- 3.173