Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

News Intel und die EUV-Fertigung: Technische Details zu „Intel 4“ und Meteor Lake

- Ersteller Volker

- Erstellt am

- Zur News: Intel und die EUV-Fertigung: Technische Details zu „Intel 4“ und Meteor Lake

Warst du auf der von mir verlinkten TSMC Seite? Da steht folgendesxexex schrieb:Der "Verlauf" der "7nm" Prozesse ist N7-N7P-N6. Der N7+ Prozess läuft/lief parallell zum N7 Prozess, ist aber zu dem nicht kompatibel und hätte eine größere Änderung des Designs erfordert.

Sowohl N7, als auch N7P sind reine DUV Prozesse, weshalb auch die Aussage AMD hätte schon länger von EUV profitiert schlichtweg falsch ist. Erst die kommenden CPUs und GPUs die in N6 und N5 Prozessen kommen, werden dann auf einigen Layern EUV nutzen.

"In addition, 7nm FnFET plus (N7+) technology entered full-scale production in 2019 and delivered customer 7nm products to market in high volume. N7+ technology is the first commercially available extreme ultraviolet EUV-enabled foundry manufacturing process technology in the world."

Deshalb meinte ich Milan dürfte wohl N7+ sein.

Meiner Erinnerung nach wurde Zen3 in allen Formen als N7P angegeben, während Zen 2 auf N7 gefertigt wurde. Das wurde bei der Einführung von Ryzen 5000 angegeben, aber die Chiplet-Strategie funktioniert ja nur, wenn die Chiplets alle aus der gleichen Produktion kommen.

Die GPUs sind seit den 5000ern schon auf N7P. Mit Navi24 und Rembrandt auf N6, wo als einziges EUV eingesetzt wird. Ist trotzdem gegenüber Intels zukünftiger CPU (Ende 2023?) schon "lange genutzt".

Die GPUs sind seit den 5000ern schon auf N7P. Mit Navi24 und Rembrandt auf N6, wo als einziges EUV eingesetzt wird. Ist trotzdem gegenüber Intels zukünftiger CPU (Ende 2023?) schon "lange genutzt".

O

Onkel Föhn

Gast

pioneer3001 schrieb:Mir als Börsianer sagen diese Luftschloß-Angaben, dass ich weiter AMD-Aktien halten soll und nicht auf Intel umsatteln soll.

MfG Föhn.

Anhänge

Wie du schon selbst sagst, entspricht die tatsächliche Transistordichte eines Chips selten der Dichte die als maximal für den Prozess angegeben wird. Die Angaben beziehen sich meist nur auf bestimmte Schaltungen ohne Sachen wie Thermik zu berücksichtigen.Tzk schrieb:Ist amd nicht eh auf einem Custom Prozess unterwegs? Die Dichte war ja eher in Regionen um 50-60MTr/mm2 angesiedelt und nicht um 90-100 wie von TSMC für N7 angesagt. Ist natürlich nur ein Mittelwert, klar. Insbesondere Cache schrumpft ja anscheinend weniger gut...

Grundsätzlich hat AMD bisher N7 und ich glaube bei GPUs auch N7P genutzt und bewegt sich nun zu N6, was letztlich nur ein weiterer, dank EUV kostenoptimierter "7nm" Prozess ist. Der wichtige Punkt dabei ist folgender:

TSMC states that their N6 fabrication technology offers 18% higher logic density when compared to the company’s N7 process (1st Gen 7 nm, DUV-only), yet offers the same performance and power consumption. Furthermore, according to TSMC N6 'leverages new capabilities in extreme ultraviolet lithography (EUVL)' gained from N7+, but does not disclose how exactly it uses EUV for the particular technology. Meanwhile, N6 uses the same design rules as N7 and enables developers of chips to re-use the same design ecosystem (e.g., tools, etc.), which will enable them to lower development costs. Essentially, N6 allows to shrink die sizes of designs developed using N7 design rules by around 15% while using the familiar IP for additional cost savings.

https://www.anandtech.com/show/1422...echnology-7-nm-with-higher-transistor-density

Der springende Punkt dabei ist, der N7+ Prozess verfolgt andere Designrichtlinien, die Chips müssten dafür neu entwickelt werden und das ist nie erfolgt. Die erste Neuentwicklung von AMD wird nun auf den N5 Prozess setzen.Salutos schrieb:"In addition, 7nm FnFET plus (N7+) technology entered full-scale production in 2019 and delivered customer 7nm products to market in high volume. N7+ technology is the first commercially available extreme ultraviolet EUV-enabled foundry manufacturing process technology in the world."

This year, TSMC ramped the N7+ node. This is its first EUV process which introduces EUV at a few critical layers for cost reduction and learning. Learning from N7+, next year TSMC will be introducing the N6 node. The reason for this new node is simple. N7+ is not IP-compatible with N7 making the transition more difficult. N6, on the other hand, allows for the same design rules as N7 thereby maintaining IP compatibility.

https://fuse.wikichip.org/news/2879/tsmc-5-nanometer-update/

Der einzige mir bekannte Chip der in dem Prozess überhaupt hergestellt wurde ist Kirin, zumindest bis von seitens der USA ein Embargo verhängt wurde.

Im Grunde genommen war N7+ immer ein "Aussenseiterprozess", was kaum Verwendung in irgendwelchen Produkten fand und war mehr ein "Testlauf" für den N5 Prozess.At present, TSMC uses N7+ to produce chips for multiple customers. The most prominent customer of N7+ is Huawei's Hisilicon with the Kirin 990 5G.

https://www.anandtech.com/show/14954/tsmc-n7-euv-process-technology-in-hvm-n6-on-track

Es kann sein, dass AMD mal vor hatte N7+ zu verwenden, es gab ja eine Zeitlang Gerüchte als AMD noch von 7nm+ gesprochen hat. Dieses "+" verschwand aber irgendwann aus den Marketingfolien, was die Gerüchteküche befeuert hat und zu diversen Spekulationen geführt hat.

Denkbar ist, dass die Leistungssteigerung von N7 zu N7+ zu gering war, sie war kaum größer als die zu N7P und man die EUV Maschinen schlichtweg lieber für den N5 Prozess für Apple genommen hat. Die dürften auch den größeren Geldbeutel gehabt haben als AMD. Langfristig gesehen war es eh die bessere Entscheidung,, weil man nun ohne ein Neudesign auf N6 setzen kann.

Ergänzung ()

Angedacht laut Wikichip sind folgende Fabs:Salutos schrieb:Hat jemand eine Übersicht darüber wo Intel Intel 4 produzieren will und ob sie das benötigte Equipment für eine großvolumige Fertigung schon haben?

Grundsätzlich kämen aber natürlich auch andere Fabs in Frage, laut Wikipedia wäre es diese:Intel's 7-nanometer process (renamed as Intel 4), P1276, will enter risk production at the end of 2022 and ramp in 2023. On February 8 2017, Intel announced a $7B investment in Arizona's Fab 42 which will eventually produce chips on a 7 nm process. On March 23 2021, Intel announced a $20B investment for two fabs in Arizona, which will produce chips on a 7nm process.

Zuletzt bearbeitet:

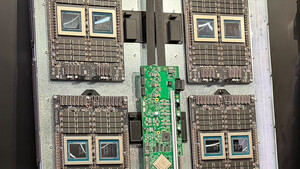

Bisherige mobile CPUs haben den PCH mit auf dem Package. Der muss bei Meteor Lake also auch mit drauf. Der SoC wird also ein PCH mit eventuell erweiterten Funktionen sein. @Philste hat ja ein interessante Slide gezeigt.Tzk schrieb:Wurde hier eigentlich schon besprochen wo genau Intel die Unterscheidung zwischen SoC-Tile und IO-Tile macht? Oder anders gefragt: Warum ist der SoC Tile so riesig und was genau ist da drin? GPU/Cpu Kerne sind es nicht, I/O (PCIe USB?) auch nicht. Bleibt noch das Dram Interface?

Media engine und Display Controller wird man auch vom GPU Die raushalten wollen, um dort nur Logik und SRAM zu haben, wie beim CPU Die auch. Das macht schon Sinn.

Wie aber IO-Die und SoC aufgeteilt sind ist die Frage.

Aber der IO-Tile ist so klein, da wird kaum mehr als der Speichercontroller und -Interface und vielleicht ein paar PCIe Lanes drin sein.

Würde aber auch bedeuten, dass für den Desktop die CPU anders aussieht. Da gibt es nicht genug Pins am Sockel um den PCH zu integrieren. Wäre bei großen Mainboards auch eher nachteilig.

Zuletzt bearbeitet:

Alternativlos kann man ja nur werden, wenn man den ganzen Markt bedienen kann. Und das wird nicht passieren.Humbertus schrieb:Klingt alles erstmal sehr gut und ambitioniert aber dann muss Intel es auch hinbekommen rechtzeitig nächstes Jahr zu liefern.

Als Verbrauche habe ich wenig davon wenn AMD alternativlos wird und die Preise dadurch anziehen.

Techpowerup sagt dazu was anderes:bensen schrieb:Bisherige mobile CPUs haben den PCH mit auf dem Package. Der muss bei Meteor Lake also auch mit drauf. Der SoC wird also ein PCH mit eventuell erweiterten Funktionen sein

The SoC Tile packs uncore and high-bandwidth I/O components, including the memory controllers, PCI-Express 5.0 root complex, Management Engine, etc.

https://www.techpowerup.com/295790/intel-meteor-lake-p-soc-with-6p-8e-compute-tile-picturedThe I/O Tile is essentially an integrated PCH that handles platform I/O that isn't as bandwidth heavy has the main PEG interface, or the main Gen 5 NVMe interface.

Hört sich für mich ehrlich gesagt plausibler an, der SoC wäre an sich die zentrale Komponente in diesem "Verbund" und der I/O Tile ist ein PCH der je nach Variante unterschiedlich ausgelegt wird oder ganz wegfällt. Das würde dann auch besser zu den Renderbildern passen, auf denen es kein I/O Die gab.

Zuletzt bearbeitet:

- Registriert

- Juni 2001

- Beiträge

- 20.013

Artikel-Update: David Kanter hat für Realworldtech einen exzellenten Artikel zu dem Thema mit weiteren Informationen verfasst. Interessant ist dabei unter anderem ein Punkt: Auf dem Papier würden ohne EUV die Anzahl der Belichtungsschritte um rund 30 Prozent steigen, dank EUV sinken sie um 20 Prozent. Aber das ist bekanntlich nicht alles. EUV ist nach wie vor sehr teuer, weshalb Intel nur einige Lagen damit belichtet (Anzahl unbekannt) und später selbst das altbekannte SAQP-Verfahren (self-aligned quad-patterning) wirtschaftlicher ist, also vier Schritte im alten Verfahren statt nur einem mit EUV. Unterm Strich spart Intel mit EUV am Ende, wenn alles berücksichtigt wird (deposition, etch, clean, polish), nämlich nur rund fünf Prozent der gesamten Arbeitsschritte ein. Dennoch dürfte insbesondere der Rückgang an Belichtungsschritten positiv für die Ausbeute (Yield) sein.

[Bilder: Zum Betrachten bitte den Artikel aufrufen.]

Kein wunder, dass Intel hier spät einsteigt.

Selbst jetzt ist EUV immer noch sehr teuer, langsam im Durchsatz. Aber trotzdem hat es hier inzwischen große Sprünge gegeben. Früher waren 100 Wafer die Stunde gut.

Ein nass DUV schafft an die 300 Wafer/h, der aktuellste EUV 160.

Dazu kommt deutlich schwierigere Wartung und entsprechend längere Downtimes.

Andere haben halt eher angefangen, Intel versucht jetzt das dort aufgebaute Know How nachzunutzen. Ob das richtig war halte ich allerdings auch für fraglich. Hier hat Intel den Anschluß verloren und das aufzuholen wird dauern.

Und in wie weit Intels aktuelle Architektur davon profitiert, man darf gespannt sein. So einfach ist das nicht.

Selbst jetzt ist EUV immer noch sehr teuer, langsam im Durchsatz. Aber trotzdem hat es hier inzwischen große Sprünge gegeben. Früher waren 100 Wafer die Stunde gut.

Ein nass DUV schafft an die 300 Wafer/h, der aktuellste EUV 160.

Dazu kommt deutlich schwierigere Wartung und entsprechend längere Downtimes.

Andere haben halt eher angefangen, Intel versucht jetzt das dort aufgebaute Know How nachzunutzen. Ob das richtig war halte ich allerdings auch für fraglich. Hier hat Intel den Anschluß verloren und das aufzuholen wird dauern.

Und in wie weit Intels aktuelle Architektur davon profitiert, man darf gespannt sein. So einfach ist das nicht.

CDLABSRadonP...

Admiral

- Registriert

- Feb. 2021

- Beiträge

- 7.369

Ja, die Theorie, die du wiedergibst, klingt reichlich absurd; in etwa so hirnamputiert wie die berüchtigte Intel-Schulblade.RogueSix schrieb:Intel hat TSMC also mit voller Absicht auf und davon ziehen lassen, um 14nm bis zum bitteren Ende zu melken. Das gilt hier auf Computerbase inzwischen als die offizielle Version. Die angeblichen 10nm Probleme haben nie existiert und sämtliche offizielle Aussagen dazu sind glatte Lügen.

Sagt jedenfalls Computerbase und der ganz überwiegende Teil der Community hier. Wir müssen uns halt darauf verlassen, dass das so stimmt und die das aus sicherer Quelle (im Zweifel sicherlich Igor... der geht immer) wissen.

Doch befürchte ich, dass allein deine Interpretation dafür verantwortlich ist, dass du überhaupt eine solche Theorie erkennst...

Denn tatsächlich sagt Volker etwas völlig anderes:RogueSix schrieb:@andi_sco Ja logisch und der Kommentar bestätigt ja genau das, was ich geschrieben habe. Denn auch hinsichtlich EUV vermutet Volker, dass Intel wieder etwas VORGAUKELN werden und wollen, also prinzipiell exakt das, was ich geschrieben habe, nämlich das angebliche (übrigens mehrjährige) Vorgaukeln von 10nm Problemen, was hier von der Redaktion -und von einem Großteil der AMD-affinen Community eh schon lange- inzwischen offenbar als unumstößlicher Fakt angesehen wird, wobei sich mir persönlich immer noch die Frage stellt, welchen Vorteil Intel davon gehabt haben soll, dass sie TSMC sehenden Auges auf Nimmerwiedersehen haben links an sich vorbeiziehen lassen.

Bei ihm geht es darum, dass Intel der Presse und den Aktionären vorgaukeln möchte, dass sie mit Intel 4 schon weiter wären, als sie es eigentlich sind. Sprich: Das genaue Gegenteil, was du da reininterpretierst!Volker schrieb:Erste Lösung mit EUV halt, kurze Halbwertzeit, aber muss eben sein. Und kleinste CPU-Tiles sind perfekt dafür. So kann man auch ne schön hohe Yield vorgaukeln und sagen wie geil die ersten Gen mit EUV doch schon ist.

Naja, sie erhalten einen neuen, komplexeren Prozess und haben trotzdem 5% weniger Arbeitsschritte. Das klingt für mich sehr logisch und spricht für die Nutzung von EUV.Volker schrieb:Unterm Strich spart Intel mit EUV am Ende, wenn alles berücksichtigt wird (deposition, etch, clean, polish), nämlich nur rund fünf Prozent der gesamten Arbeitsschritte ein.

- Registriert

- Juni 2001

- Beiträge

- 20.013

Ganjaware schrieb:Wenn überhaupt kommt Intel erst ab 2027/28 back on track:

Also bei dem maschinell übersetzten ist sooo viel falsch, das ist schon unglaublich^^

1. Es sind immer nur 17 Mrd in Magedeburg, für Phase 1 und 2 zusammen.

2. 12 Mrd gehen an weitere Standorte in Europa, wie Polen, Spanien und Frankreich

3. Italien wird wohl noch 4,5 Mrd bekommen für ein Back-End-Werk .. summa summarum 33 Mrd

4. Intel 4 wird zuerst in Hillsboro gebaut, ab nächstem Jahr auch in Irland, auch andere Fabs wie in Israel werden massiv aufgerüstet

Intel 3 folgt dann binnen eines halben Jahres und steht dann in Konkurrenz zu N3 von TSMC, was auch erst nächstes Jahr da ist. Da ist die Gap schon deutlich kleiner. Ab 2025 soll dann GAA kommen, hier gibt es bei TSMC auch nur die Ansage 2025+. Da wäre es auf dem Papier ein Gleichstand, was davon stimmt, wird sich zeigen. TSMCs ganzen neuen Prozesse machen auch nur noch Mini-Schritte, aber das können sie sich leisten, weil sie in Front liegen. Bei GAA wird alles neu gemischt.

Zuletzt bearbeitet:

Bin ich hier der einzige, dem diese tollen Werte total mau vorkommen? Viel Marketingblabla aber so toll scheint Intel4 gar nicht zu sein. Auf jeden Fall nicht besser als N5.

Das ist durchaus ein Schritt in die richtige Richtung, nicht falsch verstehen. Aber der große Wurf ist das nicht.

Das ist durchaus ein Schritt in die richtige Richtung, nicht falsch verstehen. Aber der große Wurf ist das nicht.

- Registriert

- Juni 2001

- Beiträge

- 20.013

Es ist ja auch quasi Intels N5, nur sie nennen es 4 weil kleiner gleich geiler

Deshalb hat TSMC ja auch 3 N4-Prozesse nun .. oder ka wieviele mehr auf der Off-Roadmap sind.

Die Pitches sind schon OK, sie gehen wirklich auf Nummer sicher wie es scheint. Noch ein Desaster überleben sie wohl auch nicht. Bei TSMC N5 ist Gate und Metal Pitch auch rund 50/30 nm

Deshalb hat TSMC ja auch 3 N4-Prozesse nun .. oder ka wieviele mehr auf der Off-Roadmap sind.

Die Pitches sind schon OK, sie gehen wirklich auf Nummer sicher wie es scheint. Noch ein Desaster überleben sie wohl auch nicht. Bei TSMC N5 ist Gate und Metal Pitch auch rund 50/30 nm

Zuletzt bearbeitet:

Ich finde es ja höchst interessant, dass Intel und TSMC überhaupt mit derartigem Material „an die Öffentlichkeit“ gehen, denn offensichtlich ist das ja nur sehr bedingt dazu geeignet, eben dieser überhaupt irgendetwas „nützliches“ zu vermitteln.Tzk schrieb:Interessant zu sehen das Leute offensichtlich die gezeigten Diagramme fehlinterpretieren oder schlicht nicht verstehen, dann aber anderen erklären wollen was Intel (und TSMC) an Infos an die Öffentlichkeit kommunizieren

Wenn sich hier im Forum schon die Geeks und (vermeintlich) besser Bescheid wissenden uneinig in der Interpretation der Infos sind, dann sind diese Mitteilungen ja wohl höchsten für eine eng definierte Fachschaft und kaum für die „breite Öffentlichkeit“.

… aber für Unterhaltung bei Popcorn und Bier ist immerhin gesorgt! 🤣👍

Und gab es da nicht auch noch einen dritten Mitspieler über dessen Blatt eifrig diskutiert wird? Die durchgehende und konsequente Nicht-Erwähnung Samsungs fällt irgendwie auf...Volker schrieb:Bei GAA wird alles neu gemischt.

Ähnliche Themen

- Antworten

- 29

- Aufrufe

- 4.998

- Antworten

- 19

- Aufrufe

- 2.200