Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

News AMD Zen 6 CCD: 50 Prozent mehr Kerne auf nahezu gleicher Fläche?

- Ersteller MichaG

- Erstellt am

- Zur News: AMD Zen 6 CCD: 50 Prozent mehr Kerne auf nahezu gleicher Fläche?

Slayterix

Lt. Junior Grade

- Registriert

- Nov. 2007

- Beiträge

- 323

Und Intel hat damals auch gechillt zu FX und Bulldozer Zeiten und 6-7 Jahre auch nur kleine Upgrades von 3-10 % raus gehauen pro Generation. Bei ZEN 1 mussten Sie aber wieder reagieren um mithalten zu können.Dessi schrieb:Na klar kommt der neue Ryzen mit 24 Kernen / 48 Threads - das wissen wir nun doch schon sehr lange.

Die Frage ist: wann kommt er ?

Da Intel mit den neuen Core Ultra Refresh wieder mal total enttäuscht, hat sich AMD gesagt: da lassen wir es mal langsam angehen und bringen die neuen Ryzen erst Ende 2026 raus...oh je !

Aber die Frage ist doch wie hoch der Idle-Verbrauch der CPU im Bezug auf den ganzen PC tatsächlich relevant ist.Casillas schrieb:Der Idle Verbrauch bei den Ryzen CPUs ist nicht wirklich gut. Da sind sich ja alle einig.

Man muss sich nur die Kennlinien der Netzteile und der Spannungswandler auf den Mainboards anschauen. Im Niedriglast-Bereich fällt der Wirkungsgrad ins bodenlose.

Der hohe Idle-Verbrauch ist für AMD ein reales Problem, weil Dragon Range und Fire Range deswegen nicht als Notebookprozessoren taugen.Casillas schrieb:Trotzdem wird jetzt von einigen als wichtigster Punkt die Verbesserung des idle Verbrauchs genannt.

Es gibt fast immer die Lösung einen PC auszuschalten.

Der wichtige Punkt ist, wenn der Idle-Verbrauch wirklich wichtig ist, weil man den PC durchlaufen lassen muss, muss man den gesamten PC dementsprechend konfigurieren, kleines Netzteil, Mainboard ohn viel Schnick Schnack und ohne überdimensionierte Spannungsversorgung, ...

Es müssen nicht immer dieselben Personen sein die mit einem 1000 Watt Netzteil im Idle unterwegs sind und die die weniger Power bei Idle verbrauchen wollen.Casillas schrieb:Passt für mich nicht zusammen.

Alle Gerüchte besagen, dass der L3 Cache auf dem CCD größer wird, so dass es bei 4 MByte je Kern bleibt.Piktogramm schrieb:Wobei die Hitrate vom L3-Cache bei den meisten Anwendungen jetzt nicht brachial schlechter würde, wenn der L3 gleich groß bliebe, aber die Anzahl an Kernen von 8 auf 12 stiege.

Auch der L3 Cache beim Dense CCD ist nun auf 4 MByte je Kern. Deshalb ist das Dense CCD nun so um die 160 mm² groß.

L3 Cache je Kern ist AFAIU ist für Server von Belang da mehr Threads in der Regel auch mehr Daten schaufeln.

Man muss CCD gegen CCD vergleichen und CCD + CacheChiplet gegen CCD + ChacheChiplet.Piktogramm schrieb:Mit 3D-Cache wäre die Änderung bei der Hitrate sogar noch kleiner.

Wenn das Cache Chiplet bei 64 MByte bleibt wären es beim Zen 6 X3D mit 112 MByte immer noch mehr als aktuell. Beim Desktop mit Games hast Du recht. Niemand spielt nun 2 Games auf der 12 kern CPU. und mit einem Game ändern mehr Kerne nichts an der Verteilung der Soeicherzugriffe und somit dürfte die Hitrate leicht steigen. Mit einem 96 MByte Cachehiplet und insgesamt 144 MByte L3 wäre sie noch Mal besser. als bei aktuellen X3D.

Bei Turin gab es keine Variante mit X3D. Bei Venice könnte es zumindest für HPC wieder eine geben.

Der Durchsatz wird durch das Infinity Fabric festgelegt. Ich gehe davon aus, dass AMD das IFoP so designed hat, dass IFOP Links die CCDs nicht ausbremsen.Piktogramm schrieb:Verkraftbar wäre das, wenn die Die2Die Interconnects schneller werden (Durchsatz und Latenz).

Bei den Latenzen ist es nun mal so, dass sich die Switches und repeater der Infinity Fabrics in der CCD und im IOD auch auf die Latenz auswirken. Hier ist also nicht nur die Latenz der IFoP-SERDES relevant.

Diese Folie von der ISSCC 2020 zeigt das Infinity Fabric im sIOD von Zen 2.

Es zeigt die Latenzen vom CCD1 zu den einzelnen Speicherkontrollern.

Die zusätzlichen Latenzen im IOD sind deutlich kleiner als die Latenz von CCD1 zu IOD (ich gehe Mal von 90 ns aus). Hier haben IMO die SERDES eine deutliche Auswirkung.

Allerdings kenne ich keine Messung zu Strix Halo, die zwischen den Dies eine deutlich niedrigere Latenz als Granite Ridge zeigt.Piktogramm schrieb:Was erwartbar ist, wenn sie da den Interconnect vom StrixHalo übernehmen (was die Gerüchteküche so verlautbart).

Wobei ich dazu sagen muss, dass ich diesen Messungen nicht sonderlich traue.

- Die Schwankungen zwischen den einzelnen Kernen eines CCDs sind viel zu klein.

- Die Latenz zwischen den beiden Threads eines Kerns ist nicht deutlich kleiner als die Latenz zu den anderen Kernen.

- Am Anfang hat Zen 5 sehr schlechte Werte bei den Latenzen zwischen den CCX gehabt. Das galt für Strix Point und Granite Ridge. Dann hat AMD die Firmware angepasst. Plötzlich waren es bei Granite Ridge dieselben Werte wie bei den Vorgängern. Aber die Performance hat sich kaum geändert.

Was man unbedingt beachten sollte, bei den Servern steigt die Speicherbandbreite drastisch an. Diese höhere Speicherbandbreite muss auch intern durchgeschoben werden können.

Slayterix

Lt. Junior Grade

- Registriert

- Nov. 2007

- Beiträge

- 323

Wohnst du sehr nah ein einem größeren Energieerzeuger ?BloodGod schrieb:Zahle nun schon seit Jahren 21-23 Cent im Durchschnitt dank mydealz und Co. Bin bei knapp 55€ im Monat bei 2300kwh als Single, macht mich nun nicht wirklich arm…

also in RLP gibt es keinen Tarif laut check24, Verifox ect. der unverschämte Grundgebühren verlangt unter 29 Cent die KWH bei normalem Verbrauch wie bei dir mit 2300KWH

alkaAdeluxx

Lt. Commander

- Registriert

- Mai 2007

- Beiträge

- 1.544

Das glaub ich bei Intel erst, wenn ich es sehe 😅Matthiazy schrieb:Dort soll ja Razer Lake angeblich auf dem gleichen Sockel wie Nova Lake funktionieren.

- Registriert

- Okt. 2012

- Beiträge

- 8.118

Die meisten Enthusiasten die AM5 haben, werden es sich geholt haben als 32GB noch 400€ gekostet haben, also ganz am Anfang. Klar, ein paar haben zu den schnäppchen Preisen letzen Sommer zugegriffen. Also im Endeffekt macht es echt keinen so großen Unterschied.Werderwunder schrieb:Für Aufrüster die die passende Infrastruktur haben vermutlich ein tolles Upgrade, aber ein PC Neubau ist für die nächsten 2-3 Jahre vermutlich aufgrund der beschissenen Marktlage bei Ram, SSD und GPU etwas was ohnehin sich nur noch eine Minderheit leisten kann und will.

Wer ein neues System will, also wirklich will und nicht nur mit nimmt, weil es nice to have ist, der wird sich auch nicht von den gesalzenen Preisen abschrecken lassen. Besonders weil nicht zu erwarten ist das die CPU diesesmal gleich mit 900€ zu Buche schlägt, weil alle sich drauf stürzen wie die Geier. ;-)

Ich ärger mich trotzdem ein wenig nicht letztes Jahr zugeschlagen zu haben und halt dieses Jahr die ganzen neuen Musikinstrumente zu kaufen, hätte ich gut was gespart ... anderseits, viel Spaß macht gehabt und wenig vorm PC gesessen, passt schon.

Diese Rechnung ergibt keinen Sinn.CDLABSRadonP... schrieb:Die Zahlen von ChipsAndCheese zu den Zen6C-CCDs passen auf jeden Fall auch gut:

https://chipsandcheese.com/p/ces-2026-taking-the-lids-off-amds

Milchmädchen: 76:12 sind 6 1/3mm², 164/32 wären 5 1/8mm² pro Kern. 76mm² ist der Wert von hier, ChipsAndCheese hat fürs Zen6C-CCD 165mm² angenommen, mit 164mm² lässt es sich halt glatt rechnen.

- Der L3 Cache verwässert die Unterschiede in den Kernen

- Die Repeater und Switches des Infinity Fabric benötigen ebenfalls Fläche und wir wissen nicht wie AMD die Kerne auf den CCDs verschaltet. es kann gut sein, dass das Dense CCD überpropotional mehr Fläche für den Infinity Fabrik benötigt.

- Auch bei der Anbindung ans IOD kann es Änderungen geben.

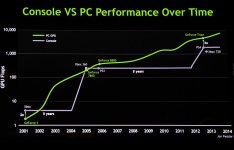

Und es kamen auch neue Konsolen. Meistens ist der Sprung nachdem eine neue Konsolengeneration rausgekommen ist größer.Slayterix schrieb:Und Intel hat damals auch gechillt zu FX und Bulldozer Zeiten und 6-7 Jahre auch nur kleine Upgrades von 3-10 % raus gehauen pro Generation. Bei ZEN 1 mussten Sie aber wieder reagieren um mithalten zu können.

Anhänge

BloodGod

Commander

- Registriert

- März 2023

- Beiträge

- 2.954

Slayterix schrieb:Wohnst du sehr nah ein einem größeren Energieerzeuger ?

Ne, aber ich muss mal fragen:

Ihr rechnet alle Boni etc mathematisch korrekt ein und wertet das Endergebnis dann aus, oder?

Ich mache das zb jedes Jahr mit einer extra vorbereiteten Excel Tabelle, oder inzwischen auch gerne mal mit Ki.

Die erste Zahl bei Check24 und Verivox etc. hat ja erst mal nichts zu sagen.

Tut es doch. Es geht nur noch mit Tippelschrittchen weiter.DragonScience schrieb:Sollte nicht hier langsam mal das Ende des Schrumpfens kommen ?

Das meiste kommt nicht mehr vom Shrink sondern von DTCO.

Wir haben hier 50 % bei 2 Nodes. In den guten alten Zeiten hat ein Node 100 % gebracht.DragonScience schrieb:Dachte mir fast das des jetzt schwierig wird mit kleineren Strukturen aber 50% mehr auf gleicher Fläche hört sich schon nach einen saftigen Sprung an.

Northstar2710

Fleet Admiral

- Registriert

- Aug. 2019

- Beiträge

- 10.305

Das stimmt schon. Allerdings wird dies ja nur relevant bei starke multicoreanwendung. Wenn alle Kerne gleich viel mehr Cache benötigen würden. In wie weit das relevant ist kann ich nicht wirklich beurteilen, da es auch Anwendungsprogramme nutzen müssen. Ich kenne da leider keine. Und bei Spielen wird das auch kaum ins Gewicht fallen.ETI1120 schrieb:Wenn das 3D Cache Chiplet nicht mitwächst stehen je Kern weniger MByte L3 Cache als bei Zen 5 zur Verfügung. Also wird AMD wenn es irgend möglich ist auch mehr SRAM aufs Cache Chiplet packen.

Wenn ich wetten müsste, würde ich sagen dass der Nachfolger des 9800X3D also eher AI 580x3d ansatt 10800X3D etwa 10-15% mehr Performance haben wird.theGucky schrieb:Ich werde von einem 9800X3D auf einen 10800X3D upgraden.

Damit werde ich dann AM6 komplett überspringen, außer es kommt eine große Technologische Änderung in Sachen Spiele die mehr CPU Leistung braucht... aber daran glaube ich nicht, eher wird es eine Add-In Karte für z.b. KI in Spielen geben.

Dass AM6 sogar laut Gerüchten erst 2029 erscheinen könnte weißt du oder?

Somit möchtest du erst vermutlich frühestens 2036 upgraden?

Schon bei den teuren X670E Boards war die Anbindung des "Chipsatzes" mit 4 Lanes PCIe 5 eine Frechheit.bensen schrieb:Ein neuer Chipsatz mit PCIe 5.0 Anbindung und mehr Lanes wäre sinnvoll. Ebenso USB 4.0 direkt auf der CPU. Oder zumindest eines von beiden.

Den gleichen Quatsch noch ne Generation mitzuschleppen können die sich eigentlich nicht leisten. Klar, für den Großteil der Anwender taugts.

Wie AMD mit USB4 umgegangen ist kann ich auch nicht nachvollziehen. Dass sich die USB4 Ports von Hawk Point auf den meisten Boards nicht nutzen lassen ist einfach nur bescheuert.

Wir sind einer Meinung, AMD muss da was tun. Aber es einige Anzeichen dafür, dass AMD nichts tut.

Das Problem ist immer, wie viel Geld wollen die Käufer ausgeben. Wie viel mehr Geld wollen die Käufer für die 8 Kerne mehr ausgeben?bensen schrieb:Aber 12-24 Kerne wird man zu Anfang nicht verramschen. Die Preise für Zen 6 werden hoch sein. Siehe auch Zen 4 und 5 zum Start. Da sind die Erwartungen schon andere.

Wie viel schneller wird Zen 6 wie Zen 5? Und was bringt Intel mit Nova Lake. Das sind die Dinge die dafür entscheidend sind, was AMD verlangen kann. AMD wird mit dem Leben müssen was der Markt hergibt. Bei Zen 4 hat sich AMD binnen 2 Monaten von den Einstandspreisen verabschiedet

D0m1n4t0r

Rear Admiral

- Registriert

- Jan. 2014

- Beiträge

- 5.738

Könnte mir vorstellen, dass es X3D Modelle dann nur bis maximal 12 Kerne gibt und die auf ein Chiplet setzen wohingegen die nicht-X3D-Modelle auf zwei Chiplets mit bis zu 24 Kernen setzen.

X3D Chips wären dann für Gaming wo 12 Kerne / 24 Threads ja komplett reichen, wohingegen die CPUs mit zwei Chiplets dann für die Leute wären die viel Rechenleistung brauchen.

Und die die noch mehr Leistung brauchen die müssen dann eben zu Threadripper greifen.

X3D Chips wären dann für Gaming wo 12 Kerne / 24 Threads ja komplett reichen, wohingegen die CPUs mit zwei Chiplets dann für die Leute wären die viel Rechenleistung brauchen.

Und die die noch mehr Leistung brauchen die müssen dann eben zu Threadripper greifen.

Moritz Velten

Commander

- Registriert

- März 2020

- Beiträge

- 2.986

hel666 schrieb:Wird die nächste Generation tatsächlich Ryzen 10000 heißen? Na ich weiß nicht.

AMD Ryzen X klingt doch direkt viel besser, wenn ihr mich fragt.

Bert

Lt. Junior Grade

- Registriert

- März 2001

- Beiträge

- 479

Wenn die Verlustleistung nicht singt, bin ich bei dir. Das wird schwirig mit einem Luftkühler.lmfaktor schrieb:Und wie soll man die dann kühlen können? Ist doch jetzt schon mit Ryzen 3 schwierig, selbst mit Wasserkühlung.

CDLABSRadonP...

Admiral

- Registriert

- Feb. 2021

- Beiträge

- 7.387

Ich gehe auch davon aus, dass insgesamt für Consumer keine CCDs mit bloß sechs aktiven Kernen kommen werden. Das wäre schließlich in etwa so, wie wenn es bei GraniteRidge noch Quadcore-SKUs gäbe.Alesis schrieb:Ich gehe davon aus, dass zum Anfang keine 6 Kerne kommen werden.

Neunkerner werden die neuen Sechskerner sein, (ein Viertel der Kerne deaktiviert) falls AMD großzügig, die Intel-Konkurrenz zu stark sein wird oder sie sich nicht vermarkten lassen, werden sogar Zehnkerner das untere Ende der Desktop-Chiplet-„CPUs“ darstellen.

Falls die Intel-Konkurrenz sehr schwach sein sollte, dann wird AMD auch weiterhin Achtkerner bringen.

Das ist der Plan. Habe damals nur den 7600x gekauft, um mir den 11800x3d zu gönnen.Werderwunder schrieb:Für Aufrüster die die passende Infrastruktur haben vermutlich ein tolles Upgrade, aber ein PC Neubau ist für die nächsten 2-3 Jahre vermutlich aufgrund der beschissenen Marktlage bei Ram, SSD und GPU etwas was ohnehin sich nur noch eine Minderheit leisten kann und will.

Im Kern selbst ist, was die Fläche angeht sehr viel SRAM. Die 48 kBit des L1 D Caches benötigen so ziemlich dieselbe Fläche wie 512 kB L2 Cache. Die Vektor Register benögtien so ziemlich 1/3 der Fläche der FPU, ...bensen schrieb:Warum eigentlich?

Also funktioniert die Rechnung die Fläche des Kerns mit Logik gleichzusetzen nicht. Der Kern skaliert schlechter.

Natürlich gibt es auch die Möglichkeit die SRAM-Zellen oder SRAM-Blöcke zu optimieren. Damit hat AMD bei L3 Cache von Zen 5 Fläche eingespart. Aber davon auszugehen, dass es nochmal gelingt ist IMO zu verwegen.

Und grundsätzlich, ich lasse mich lieber positiv als negativ überraschen.

Zen 5 ist eine Baustelle. Der Umbau auf 6 ALU ist definitiv nicht abgeschlossen. Mit realen Code ist eine IPC von 5 erreichbar. Mit synthetischem Code ist eine IPC von 5,5 erreichbar. Auch bei der FPU gibt es noch ein. Außerdem gab es einiges Regressionen unerwünschte Latenzen, ....bensen schrieb:Zumal Zen5 bei den Kernen sehr in die Breite gegangen ist. Das man diese Iteration dann eher moderat rangeht und nur im Detail verbreitert ist nicht unlogisch.

Also war klar AMD wird bei Zen 6 nicht nur ein bisschen feilen.

Inzwischen ist klar, dass AMD auf 6 Integer Scheduler geht.

Und außerhalb des Kern kann sich auch etwas ändern. AFAIU skaliert ein doppelter Ringbus bis zu 10 Kernen ganz gut. Das Zen 6 Classic CCD hat 12 Kerne, alle 12 an einem doppelten Ringbus würde mich überraschen. Also gehe ich davon aus dass das Infinity Fabric auf dem CCD ein bisschen aufwändiger wird.

Faust2011 schrieb:Wenn ich mir noch was wünschen dürfte von AMD, dann wäre es den Idle-Verbrauch zu senken.

Casillas schrieb:Trotzdem wird jetzt von einigen als wichtigster Punkt die Verbesserung des idle Verbrauchs genannt. Kann ich nicht nachvollziehen.

man zockt mit einer Gaming CPU

ansonsten ist der PC doch aus 🤷♂️

aus meiner Sicht ist Idle bei X3D uninteressant

zum Arbeiten ein Mac mini, der schaltet nicht mal die Lüfter an und hat kaum Stromverbrauch.

Gibt auch MiniPCs mit Windows

Piak schrieb:Was man braucht, hängt daran ob man die Rechenlast überhaupt auf mehrere Threads aufteilen kann.

das ist ein wichtiges Argument

Einige Spiele boosten oft auf wenigen Kernen, während andere sich ausschalten oder wenige Prozent Auslastung haben

mit 12/24 Kernen hat man keinerlei Vorteile, wenn die Engine schon 8/16 nicht gleichmäßig auslastet

Ähnliche Themen

- Antworten

- 51

- Aufrufe

- 6.415