High-End-Speicher: SK Hynix liefert HBM3 für Hopper an Nvidia aus

Nvidia hat die Nutzung von HBM3 für die Profi-Grafiklösung „Hopper“ bereits vor Monaten angekündigt, jetzt zieht dessen Hersteller nach: Es ist SK Hynix. Dabei werden die ersten Chargen laut Pressemitteilung wohl fast ausschließlich an Nvidia gehen, wenn die Fertigung ab dem dritten Quartal hochgefahren wird.

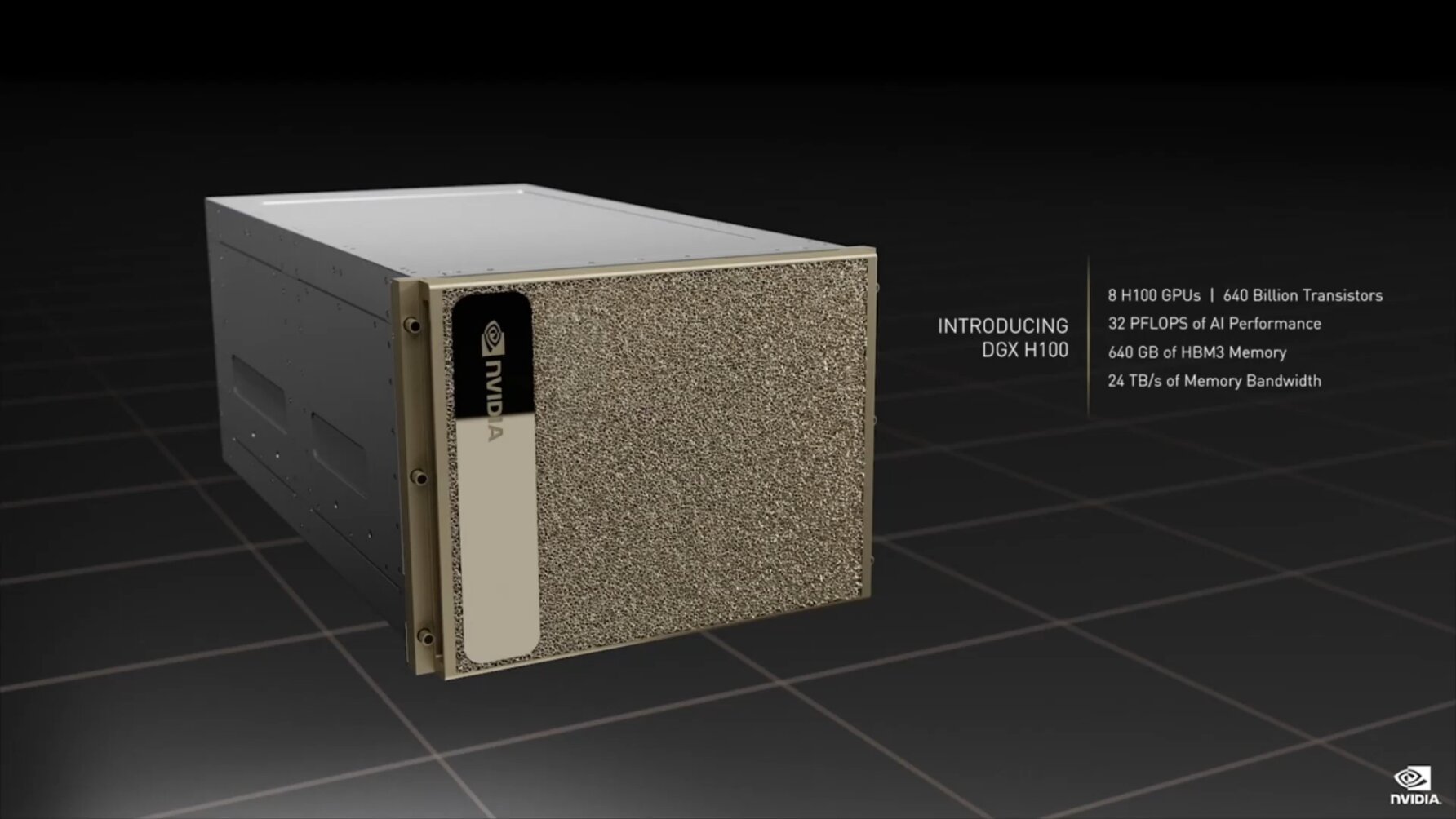

Der Zeitplan stimmt mit dem bisher bekannten von Nvidia überein. Vor dem Ende des Jahres dürfte es die Produkte mit der neuen Hopper-GPU GH100 nicht in größeren Mengen geben. Pro einzelner Hopper-GPU sind 80 GByte HBM3 verbaut, fünf Chips mit jeweils 16 GByte. In der neuen DGX H100 sind es in Summe 640 GByte, denn sie kombiniert eine Sapphire-Rapids-CPU von Intel mit acht GH100-Grafikkarten.

NVIDIA has recently completed its performance evaluation of SK hynix’s HBM3 samples. SK hynix will provide HBM3 for NVIDIA systems expected to ship starting in the third quarter of this year. SK hynix will expand HBM3 volume in the first half in accordance with NVIDIA’s schedule.

SK Hynix

Das Hochfahren der Serienproduktion mit höheren Volumen wird von SK Hynix erst für das Jahr 2023 angepeilt, was nach den letzten Aussagen seitens Nvidia bereits vermutet, nun durch SK Hynix als einzigem Speicherlieferanten aber de facto bestätigt wurde.

Die erste Welle nach JEDEC-Vorgaben

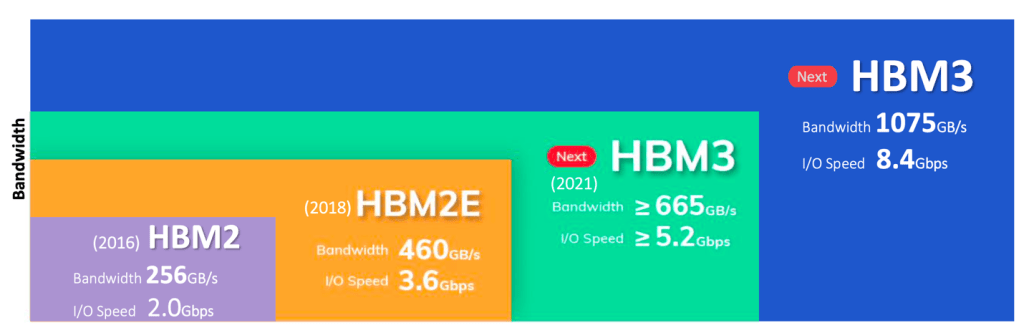

SK Hynix spezifiziert die ersten HBM3-Chips für eine Bandbreite von 819,2 GB/s. Damit folgt der Hersteller genau den Vorgaben des Speicherkonsortiums JEDEC, die zu Beginn dieses Jahres diese Basisspezifikationen festgesetzt hatten – nachdem SK Hynix Monate zuvor bereits mit eigenen Ankündigungen vorgeprescht war. Demnach bringt HBM3 eine auf 6,4 GT/s erhöhte Transferrate pro Pin mit, ein HBM3-Package kommt so auf bis zu 819 GB/s.

| Nvidia GH100 | Nvidia GA100 | Nvidia GV100 | |

|---|---|---|---|

| Architektur | Hopper | Ampere | Volta |

| Fertigung | TSMC N4 | TSMC N7 | TSMC 12FFN |

| Transistoren | 80,0 Milliarden | 54,2 Milliarden | 21,1 Milliarden |

| Die Size | 814 mm² | 826 mm² | 815 mm² |

| SMs | 144 | 128 | 84 |

| FP64 CUDA Cores | 9.216 | 4.096 | 2.688 |

| FP32 CUDA Cores | 18.432 | 8.192 | 5.376 |

| Tensor Cores | 576 | 512 | 672 |

| GPU-Takt | nicht final | 1.410 MHz | 1.450 MHz |

| Speicher | 80 GB HBM3 | 48 GB HBM2/80 GB HBM2e | 32 GB HBM2 |

| Speichertakt | nicht final | 1.250 MHz | 880 MHz |

| Speicherinterface | 6.144 Bit | 6.144 Bit | 4.096 Bit |

| Bandbreite | 3,0+ TB/s | 1,9 TB/s/2,4 TB/s | 900 GB/s |

| TDP | 700 Watt | 400 Watt | 300 Watt |

| Interconnect | NVLink 900 GB/s PCIe 5.0 128 GB/s |

NVLink 600 GB/s PCIe 4.0 64 GB/s |

NVLink 300 GB/s PCIe 3.0 32 GB/s |

Ein Stapel (Stack) kann gemäß diesen Spezifikationen 4, 8 oder 12 DRAM-Schichten umfassen; für die Zukunft sind bei HBM3 bereits 16 Layer angedacht. Die Speicherkapazität rangiert somit zwischen 4 GB beim Einsatz von vier 8-Gbit-Dies (1 GB/Die) bis hin zu 64 GB bei kommenden 16-Layer-Türmen mit 32-Gbit-Dies. Im Laufe der kommenden Jahre dürfte auch die Datenrate weiter steigen. SK Hynix selbst hatte zusammen mit Rambus noch höhere Transferraten von 8,4 GT/s in Aussicht gestellt, die umgerechnet ein Package mit 1.075 GB/s ermöglichen.

Im Podcast erinnern sich Frank, Steffen und Jan daran, wie im Jahr 1999 alles begann.