Also eine Operation besteht vereinfacht aus folgenden Phasen: nächste Instruktion laden, Instruktion decodieren und Daten laden, Ausführen, Ergebnisse zurückschreiben

Die sehr frühen CPU-Architekturen haben gesagt, dass diese ganzen Phasen zusammen ein Block sind. Sie finden in einem einzelnen Takt statt. Das Problem dabei ist aber doch, dass das Ausführen unterschiedlich lange benötigt. Eine Bitweise Negierung ist ziemlich einfach, da kann jedes Bit parallel negiert werden. Ist also extrem schnell. Eine Addition hingegen (man denke an Halb- und Volladdierer) besteht aus vielen Operationen, die nacheinander ausgeführt werden müssen. Warum sollte also nun die Negierung genauso langsam wie die Addition sein? Nur damit alles in einem Takt passiert?

Und aus dem Grund ging man weg von Architekturen bei denen ein Befehl in einem Takt ausgeführt wird und baute Architekturen bei denen die Negierung eben 3 Takte benötigte, und die Addition 7 Takte. Nur dass alles nun 7 mal so schnell ausgeführt wird. Die Addition ist nicht schneller geworden, denn alles wird zwar 7mal so schnell ausgeführt aber die Operation benötigt nun auch 7 Takte. Aber die Negierung arbeitet nun schneller, da nur noch 3 der neuen 7mal schnelleren Takte benötigt werden.

Genauso gibt es den Vorteil, dass schon der nächste Befehl geladen und dekodiert werden kann, während der vorherige noch bearbeitet wird. Also wieder schneller.

Was vorher einfach eine lange Aktion war wurde in mehrere kleine Schritte aufgeteilt, die jede für sich schneller abläuft. Dafür sind nun aber mehrere Schritte nötig. Und es können Teile parallel abgearbeitet werden. So kann z.B. schon die nächste Instruktion geladen werden, während die Instruktion davor noch berechnet wird. Aber auch nur Teile, die wie in #23 beschrieben sich nicht überschneiden und zu einem falschen Ergebnis führen würden. Für das Problem in #23 müsste eben für die Ausführung von Operation 2 auf das Ergebnis von Operation 1 gewartet werden, der Prozessor würde also einige Takte nichts machen. Und genau an dieser Stelle kommt von Intel das Hyperthreading ins Spiel: Statt nichts zu tun, kann eine Operation eines anderen Threads ausgeführt werden. Das ist der Grund warum HT z.B. nur 20% schneller ist, weil es nur da eingesetzt werden kann, wo der Prozessor warten müsste. Die mehreren Integer-Operationen der AMD-Architektur sind ein ziemlich ähnliches Modell, aber eine ganze Ecke komplexer: Im Prinzip bestimmt jeder Core in der K10-Architektur welche folgenden Integer-Operationen er alle parallel berechnen kann, ohne dass diese voneinander wie in #23 abhängig sind. Und diese werden dann berechnet.

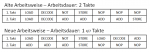

Wikipedia hat ein schönes Beispiel welchen Unterschied die Parallelität der mehreren einzelnen Phasen mit einzelnen Takten gegenüber dem 1 Takt pro Befehl Modell macht:

http://de.wikipedia.org/wiki/Pipeline_(Prozessor)

Ist es jetzt verständlicher?