Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

News AMD Ryzen Mobile mit Zen 5: Roadmap mit Fire Range, Strix Halo, Kraken Point und Escher

Northstar2710

Fleet Admiral

- Registriert

- Aug. 2019

- Beiträge

- 10.244

Ja es muss mindestens im Treiber integriert Sein. Je nach Software gibt es bestimmt auch noch Anpassungen.latiose88 schrieb:Ja muss das die software beherrschen das es von der Software benutzt wird das mit ki

DutchTraveller

Cadet 3rd Year

- Registriert

- Okt. 2022

- Beiträge

- 40

APUs eignen sich auch hervorragend für Heimserver, da ihre Leerlaufleistung viel geringer ist. Ich würde gerne eine Zen4/5-Version auf AM4 sehen.Overkee schrieb:Toll diese ganzen Mobile APUs während man für den Desktop weiter vergeblich auf neue APUs wartet

Northstar2710

Fleet Admiral

- Registriert

- Aug. 2019

- Beiträge

- 10.244

Keine Sorge kommt, allerdings wohl erst die kleinen Modelle 7300g/7500g mit 4cu igpu, später angeblich die größeren 7600g/7700gDutchTraveller schrieb:Ich würde gerne eine Zen4/5-Version auf AM4 sehen

Ergänzung ()

Ich bin allerdings gespannt wie der 7500g vs 7600 performt. Denn die 2cu igpu des

7600 fand ich nicht so prickelnd.

Die können noch so viel versprechen. Am Ende sind dennoch höchstens 2 Modelle verfügbar in minderer Stückzahl ein Jahr nach der Ankündigung, wenn überhaupt. Und dass AMD neue Chips aufsetzt mit Kernen der letzten Generation muss man nicht verstehen oder?

crustenscharbap

Rear Admiral

- Registriert

- Jan. 2008

- Beiträge

- 5.496

ZEN5 RDNA 3,5 40CUs.

Shut up an take my money!!

Das wäre wirklich cool für ein ITX Build.

Ich denke das wird die Zukunft. Dass die günstigen Modelle einfach ältere sind statt niedrig getaktete Versionen. Die Ausfallrate wird halt immer geringer.

Früher gabs nen dual core. Der eine hats bis 3,5Ghz geschafft und der andere nur bis 3,1Ghz. Letztere war billiger.

Shut up an take my money!!

Das wäre wirklich cool für ein ITX Build.

Ergänzung ()

Resteverwertung. Außerdem haben die Fertiger (GF, TSMC…) noch Lithografie-Maschinen. In der Regel hoch bis 45nm. Die werden nicht weg geschmissen.Smeany schrieb:. Und dass AMD neue Chips aufsetzt mit Kernen der letzten Generation muss man nicht verstehen oder?

Ich denke das wird die Zukunft. Dass die günstigen Modelle einfach ältere sind statt niedrig getaktete Versionen. Die Ausfallrate wird halt immer geringer.

Früher gabs nen dual core. Der eine hats bis 3,5Ghz geschafft und der andere nur bis 3,1Ghz. Letztere war billiger.

Zuletzt bearbeitet:

Northstar2710

Fleet Admiral

- Registriert

- Aug. 2019

- Beiträge

- 10.244

Zu mal man sagen muss das für einfache Notebooks ein Zen2/3/ ohne weiteres reicht. Chrombooks laufen auch auf Zen2 .

Es gibt soviele Bereiche wo auch ältere Technologien reichen. Ist alles eine Preisfrage.

Zusätzlich ist es ja so das AMD diese Chips nicht aufzwingen kann. Die entsprechenden Partner haben ihre Vorstellungen von Hardware + Preis und diese versucht AMD und Intel zu erfüllen.

Es gibt soviele Bereiche wo auch ältere Technologien reichen. Ist alles eine Preisfrage.

Zusätzlich ist es ja so das AMD diese Chips nicht aufzwingen kann. Die entsprechenden Partner haben ihre Vorstellungen von Hardware + Preis und diese versucht AMD und Intel zu erfüllen.

DutchTraveller

Cadet 3rd Year

- Registriert

- Okt. 2022

- Beiträge

- 40

TSMC verfügt derzeit über viel freie Kapazität im 7-nm-Verfahren, sodass AMD genügend APUs produzieren kanncrustenscharbap schrieb:ZEN5 RDNA 3,5 40CUs.

Shut up an take my money!!

Das wäre wirklich cool für ein ITX Build.

Ergänzung ()

Resteverwertung. Außerdem haben die Fertiger (GF, TSMC…) noch Lithografie-Maschinen. In der Regel hoch bis 45nm. Die werden nicht weg geschmissen.

Ich denke das wird die Zukunft. Dass die günstigen Modelle einfach ältere sind statt niedrig getaktete Versionen. Die Ausfallrate wird halt immer geringer.

Früher gabs nen dual core. Der eine hats bis 3,5Ghz geschafft und der andere nur bis 3,1Ghz. Letztere war billiger.

crustenscharbap

Rear Admiral

- Registriert

- Jan. 2008

- Beiträge

- 5.496

Deswegen hat ja AMD jetzt das coole neue Namensschema. So können die ZEN 3 besser verkaufen. An sich nichts Schlimmes. Finde nur doof, dass die es verschleiern. Zumindest im Notebook.

Für den Desktop: Ein 5700G mit etwas stärkerer iGPU. 16CUs RDNA2. Warum nicht? Dürfte dann wie ein 7840HS performen und 20W mehr brauchen. Für 250€ würde der sicherlich genug Abnehmer finden.

Für den Desktop: Ein 5700G mit etwas stärkerer iGPU. 16CUs RDNA2. Warum nicht? Dürfte dann wie ein 7840HS performen und 20W mehr brauchen. Für 250€ würde der sicherlich genug Abnehmer finden.

Also erstens gibt's da ja eh keine 'Sockel' mehr, das ist ja nur noch BGA und aufgelötet.ETI1120 schrieb:Dass LPCAMM mit 128 Bit kommt, weiß ich. Aber was soll das grundsätzliche Problem sein 2 LPCAMM Steckplätze bereitzustellen? Um was es mir ging war, dass AMD keine Notebook Sockel hat die 256 Bit Speicherinterface unterstützen, und deswegen dann spielt es keine Rolle was man mit LPCAMM umsetzen kann.

Zweitens: Wer definiert, dass mit Zen 5 kein Pinout kommen kann, welches 256 Bit unterstützt? Speziell im Notebooksegment ist der Wechsel eher egal, da hier eh keiner ein Upgrade vornimmt und die höheren Frequenzen und LPCAMMs eh Layoutänderungen erfordern werden.

Gleichzeitig kann man hier bekannterweise auch mit Caches gegensteuern.

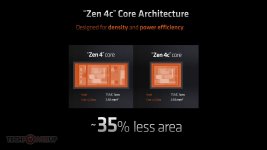

Cezanne=Barcelo=Barcelo-R wird in 7nm auf 180mm² großem Die gefertigt und hat die alte Vega-GPU mit der alten Media-Engine

Der Phoenix II wird in einem nicht teureren 6nm Prozess auf 137mm² kleinen Die gefertigt und hat die modernere RDNA-GPU mit der neuen Media-Engine

Warum sollte man im Jahr 2024 also noch Barcelo-R bringen wollen, wenn man einen günstigeren 137mm² kleinen Chip hat, der besser ist? Nur damit man noch ein paar Notebooks mit DDR4 im Jahr 2024 verkaufen kann? So teuer ist DDR5 inzwischen doch auch nicht mehr. Sogar der eine Etage tiefer eingeordnete Mendocino läuft mit LPDDR5.

Und warum taucht Phoenix 2 in der Roadmap überhaupt nicht auf?

https://www.computerbase.de/news/pr...-nun-auch-auf-die-kleinen-zen-4c-kerne.86028/

Der Phoenix II wird in einem nicht teureren 6nm Prozess auf 137mm² kleinen Die gefertigt und hat die modernere RDNA-GPU mit der neuen Media-Engine

Warum sollte man im Jahr 2024 also noch Barcelo-R bringen wollen, wenn man einen günstigeren 137mm² kleinen Chip hat, der besser ist? Nur damit man noch ein paar Notebooks mit DDR4 im Jahr 2024 verkaufen kann? So teuer ist DDR5 inzwischen doch auch nicht mehr. Sogar der eine Etage tiefer eingeordnete Mendocino läuft mit LPDDR5.

Und warum taucht Phoenix 2 in der Roadmap überhaupt nicht auf?

https://www.computerbase.de/news/pr...-nun-auch-auf-die-kleinen-zen-4c-kerne.86028/

Zuletzt bearbeitet:

Es heißt nun mal Socket FP7 bzw Socket FP8. Dass es BGA sind ist klar.Nagilum99 schrieb:Also erstens gibt's da ja eh keine 'Sockel' mehr, das ist ja nur noch BGA und aufgelötet.

Verschiedene Generationen Pin-kompatibel zu machen ist für die OEMs von Vorteil, da es den Entwicklungsaufwand reduziert.

Natürlich kann AMD mit einem neues Pinout mit 256 Bit Speicherinterface kommen. Nur hört man nichts von einem neuen FP9, der sich zu FP7/FP8 gesellen soll.Nagilum99 schrieb:Zweitens: Wer definiert, dass mit Zen 5 kein Pinout kommen kann, welches 256 Bit unterstützt?

Ich gehe davon aus, dass bei LPDDR6 ein anderes Pinout kommt. So wie es auch bei DIMM und SoDIMM war. Ich sehe jetzt keinen Grund bei LPCAMM das Interface zu ändern, weil andere Frequenzen verwendet werden. Dies wäre IMO fatal.Nagilum99 schrieb:Speziell im Notebooksegment ist der Wechsel eher egal, da hier eh keiner ein Upgrade vornimmt und die höheren Frequenzen und LPCAMMs eh Layoutänderungen erfordern werden.

LPCAMM ist ziemlich auf die Dimensionen der LPDDR-Chips zugeschnitten, ich erwarte eigentlich, dass für LPDDR5 die Abmessungen der Module definiert werden. Dies dürfte ein Unterschied zu CAMM sein.

Ja, das kann man. Nur hört man nichts dazu.Nagilum99 schrieb:Gleichzeitig kann man hier bekannterweise auch mit Caches gegensteuern.

Alle Probleme über das wir hier diskutieren, lösen sich in Lust auf, wenn man annimmt, dass das was MLID als Strix Halo beteichnet, ein Projekt der Custom-Abteilung für eine spezielle Hardware ist und dass ein GDDR-Speicherinterface verbaut ist. Die Liste der Dinge die MLID falsch einsortiert hat ist lang.

Ergänzung ()

Ich habe keinen Hinweis dafür gesehen dass Phoenix 2 in 6 nm produziert wird.Convert schrieb:Der Phoenix II wird in einem nicht teureren 6nm Prozess auf 137mm² kleinen Die gefertigt und hat die modernere RDNA-GPU mit der neuen Media-Engine

Es wäre gar nicht möglich eine Phoenix APU durch eine performance-gleiche Phoenix 2 APU zu ersetzen, wenn Phoenix 2 in 6 nm produziert werden würde.

Anhänge

Zuletzt bearbeitet:

Vincy

Commander

- Registriert

- Sep. 2007

- Beiträge

- 2.589

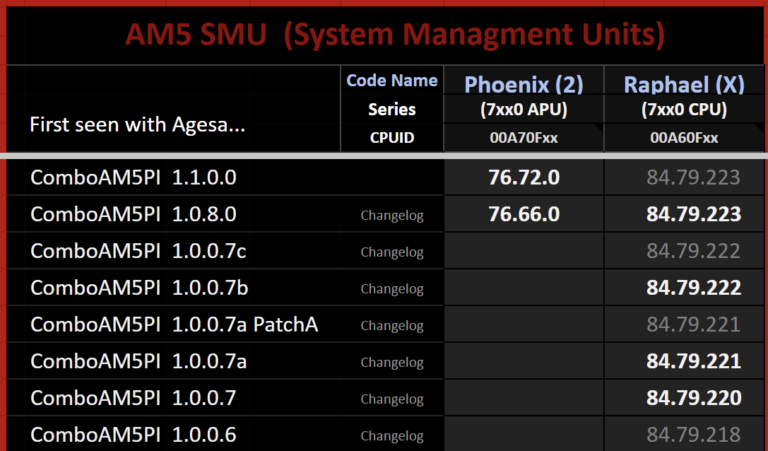

ASRock hat inzwischen erste BIOSe für die zukünftigen AM5-APUs 7000G Series "Phoenix" veröffentlicht.

https://videocardz.com/newz/asrock-...rds-with-improved-ryzen-7000g-phoenix-support

https://wccftech.com/asrock-amd-agesa-1-1-0-0-bios-firmware-x670e-taichi-motherboards/

https://www.pcgameshardware.de/CPU-...G-Zen-4-Desktop-APUs-Firmware-Update-1433173/

https://videocardz.com/newz/asrock-...rds-with-improved-ryzen-7000g-phoenix-support

https://wccftech.com/asrock-amd-agesa-1-1-0-0-bios-firmware-x670e-taichi-motherboards/

https://www.pcgameshardware.de/CPU-...G-Zen-4-Desktop-APUs-Firmware-Update-1433173/

Zuletzt bearbeitet:

Northstar2710

Fleet Admiral

- Registriert

- Aug. 2019

- Beiträge

- 10.244

Auch wenn mich das grösste Model eher reizt, werde ich wohl den 7500g als erstes testen.

Phoronix hat Lenovo-Notebooks mit Zen APUs aus 4 Generationen durch einen Benchmarkparcour geschickt:

https://www.phoronix.com/review/ryzen-thinkpad-zen2-zen4

Es sind aber nicht jeweils Notebooks derselben Serie.

Detailierte Ergebnisse

https://openbenchmarking.org/result/2310267-NE-RYZENLAPT71&sgm=1&scalar=1

Mein Fazit: Von der Performance her ist der 7840U ein riesen Sprung gegenüber dem 6850U.

Allerdings geht das auf Kosten der Power und auch der Effizienz. Was die Frage auswirft ob die kleineren APUs nicht für viele Anwender die bessere Wahl sind.

https://www.phoronix.com/review/ryzen-thinkpad-zen2-zen4

Es sind aber nicht jeweils Notebooks derselben Serie.

Detailierte Ergebnisse

https://openbenchmarking.org/result/2310267-NE-RYZENLAPT71&sgm=1&scalar=1

Mein Fazit: Von der Performance her ist der 7840U ein riesen Sprung gegenüber dem 6850U.

Allerdings geht das auf Kosten der Power und auch der Effizienz. Was die Frage auswirft ob die kleineren APUs nicht für viele Anwender die bessere Wahl sind.

Bei 'Kraken Point' wäre eigentlich ein Nachfolger Phoenix 2 zu erwarten, also 4 CU RDNA 3.5, ohne AI und dann 2* Zen5 plus 6* Zen5c, da erscheint die Folie unlogisch.Convert schrieb:@ETI1120

Damit muss ich mich korrigieren. Phoenix 2 Die ist zwar kleiner, wird aber im teureren Prozess hergestellt, ist also entgegen meiner Behauptung wohl nicht günstiger als Barcelo...

Im Mainstream würde 2* Zen5 plus 4 oder 6 Zen5c Cores im Mobilbereich und Desktop meist reichen und dann etwa bei grob $200 je APU landen.

Ich würde sagen warten wir erst einmal Strix Point ab. Dann kann man einiges viel besseres beurteilen.RKCPU schrieb:Bei 'Kraken Point' wäre eigentlich ein Nachfolger Phoenix 2 zu erwarten, also 4 CU RDNA 3.5, ohne AI und dann 2* Zen5 plus 6* Zen5c,

In welchem Preisbereich tobt sich Strix Point aus? Wie sind die 12 Kerne organisiert? Funktioniert Strix Point im HS oder gar HX Segment?*) Wann bremsen die c-Kerne StrixPoint aus? Hat XDNA 2 eine neue Architektur der Tiles oder einfach nur mehr Tiles? Was ändert sich bei RDNA 3.5? ...

*) Ich bin mir ziemlich sicher das Strix Point im HS Segment funktioniert.

Alleine aus der CPU betrachtet ergibt KrakenPoint mit 8 Zen 5 Kernen neben StrixPoint mit 4P+8E auf demselben Node keinen Sinn. Wenn die Metriken von Zen 4 auch für Zen 5 gelten sollten, dann hätten beide SoC praktisch dieselbe Fläche und Strix Point wäre im U und HS Segment deutlich schneller.

Deshalb stelle ich mir schon seit einiger Zeit die Frage, was soll Kraken Point? Oder welche Info fehlt, die den Sinn von Kraken Point erklären würde?

Bei Phoenix 2 war die AIE wegzulassen, rückblickend betrachtet, eine sehr dumme Entscheidung und AMD weiß das. Wenn AMD bei Strix Point die TOPS verdreifacht, dann halte ich es für ausgeschlossen dass Mitte 2024 oder später ein APU Die ohne AIE kommt.

Es ist eine Folie von MLID, was erwartest Du da?RKCPU schrieb:da erscheint die Folie unlogisch.

Dass der TOPS-Wert von Hawk-Point stimmt, bedeutet eben nicht, dass auch der Rest stimmt.

Für mich sind diese angeblichen AMD-Road-Maps nichts als ein Code-Word-Bingo. Und selbst wenn diese Code Words alle für APU-Projekte stehen, bedeutet es nicht, dass die Code Words auf dieselbe Road Map gehören.

Die Klassiker sind Warhol und Van Gogh, die jahrelang auf angeblich authentischen Roadmaps waren. Warhol war eine Ente. Van Gogh war ein Projekt von SemiCustom für Valve.

Das könnte so funktionieren. Aber gibt es so etwas?RKCPU schrieb:Im Mainstream würde 2* Zen5 plus 4 oder 6 Zen5c Cores im Mobilbereich und Desktop meist reichen und dann etwa bei grob $200 je APU landen.

Klar ist, in der sogenannten Roadmap fehlt Phoenix 2 bzw. Hawk Point 2, wieso? Wenn ich mich recht entsinne hat MLID versucht Phoenix 2 als Van Gogh Nachfolger zu erklären. Obwohl Valve erklärt hatte, vorerst nichts am SoC zu ändern.

Die Gerüchte zu Strix Point mit 4 P und 8 E kommen (scheinbar) aus vielen Richtungen, so dass ich das für weitgehend gesichert halte. Bei allem anderen bin ich vorsichtig.

https://www.computerbase.de/news/pr...oll-die-ai-leistung-2024-verdreifachen.86319/ETI1120 schrieb:Ich würde sagen warten wir erst einmal Strix Point... ab.

Dann kann man einiges viel besseres beurteilen.In welchem Preisbereich tobt sich Strix Point aus?Die Gerüchte zu Strix Point mit 4 P und 8 E kommen (scheinbar) aus vielen Richtungen, so dass ich das für weitgehend gesichert halte. Bei allem anderen bin ich vorsichtig.

Letztlich die 3. Stufe nach Phönix und Hawk Point = AI mit mehr Takt

Irgendwie passt eine APU OHNE AI nicht mehr zur aktuellen Vermarktung von AI.ETI1120 schrieb:Alleine aus der CPU betrachtet ergibt KrakenPoint mit 8 Zen 5 Kernen neben StrixPoint mit 4P+8E auf demselben Node keinen Sinn. Wenn die Metriken von Zen 4 auch für Zen 5 gelten sollten, dann hätten beide SoC praktisch dieselbe Fläche und Strix Point wäre im U und HS Segment deutlich schneller.

Deshalb stelle ich mir schon seit einiger Zeit die Frage, was soll Kraken Point? Oder welche Info fehlt, die den Sinn von Kraken Point erklären würde?

Bei Phoenix 2 war die AIE wegzulassen, rückblickend betrachtet, eine sehr dumme Entscheidung und AMD weiß das. Wenn AMD bei Strix Point die TOPS verdreifacht, dann halte ich es für ausgeschlossen dass Mitte 2024 oder später ein APU Die ohne AIE kommt.

Das könnte so funktionieren. Aber gibt es so etwas?

Klar ist, in der sogenannten Roadmap fehlt Phoenix 2 bzw. Hawk Point 2, wieso?

Nur noch AI würde aber auch den IO - Chip zum Zen5 Chiplet dann umfassen ?!

https://www.amd.com/de/technologies/xdna.html

Im Link unten zu Youtube wird von wird von Lisa Su persönlich betont dass Strix Point gerade ausgiebig mit der AI vom kommenden Windows getestet wird.

Aber wie könnte ein Budget AI dann für Kraken Point aussehen?

Wahrscheinlich ist das Design schon gestorben und bald taucht ein neuer Codename auf.

AMD kann nicht den 3-fachen Takt wie bei Hawk Point anlegen. Die Takterhöhung war die Notlösung für Hawk Point.RKCPU schrieb:https://www.computerbase.de/news/pr...oll-die-ai-leistung-2024-verdreifachen.86319/

Letztlich die 3. Stufe nach Phönix und Hawk Point = AI mit mehr Takt

Bei Strix Point muss mehr passieren. Und hier ist eben die Frage, bekommen die einzelnen Tiles eine neue leistungsfähigere Architektur oder gibt es nur mehr Tiles.

Es geht hier nicht um die Vermarktung von AMD. Wenn der PC in der schönen neuen AI-Welt keine speziellen Funktionen bekommt ist Ende der Plattform besiegelt. Wenn sich eh alles mit AI auf den Servern abspielt, was will man dann noch mit einem PC? Dann genügt ein schmales kleines Terminal.RKCPU schrieb:Irgendwie passt eine APU OHNE AI nicht mehr zur aktuellen Vermarktung von AI.

Auf dem FAD 2022 war das Bild, dass XDNA in das gesamte Produktporfolio außer RDNA und XDNA wandert.RKCPU schrieb:Nur noch AI würde aber auch den IO - Chip zum Zen5 Chiplet dann umfassen ?!

In verschiedenen Interviews hört sich das neuerdings ein bisschen anders an. Hier wird XDNA von David McAfee als sehr effiziente Lösung speziell für Notebooks gepriesen.

Aber das natürlich auch damit zusammenhängen, dass David McAfee momentan noch die Ryzen 7000 ohne XDNA verkaufen muss.

Neben der Energieeffizienz betont AMD (Ex Xilinx) dass die AIE eine sehr hohe Auslastung von 90 bis 95 % erreicht. Bei GPUs soll dies erheblich niedriger liegen.

Ich habe das ganze Video gesehen und auch die Ankündigung mit der 3 fachen Performance mitbekommen.RKCPU schrieb:https://www.amd.com/de/technologies/xdna.html

Im Link unten zu Youtube wird von wird von Lisa Su persönlich betont dass Strix Point gerade ausgiebig mit der AI vom kommenden Windows getestet wird.

Es bleibt aber die Frage Frage wie AMD das erreicht.

Und bei einem neuen VLIW-Engine stellt sich die Frage, welche Datentypen AMD da reinpackt. Aus einer Präsentation:

XDNA ist AIE-ML, die zweite Generation von der AIE darstellt. Wenn man sich die unterstützten Datentypen anschaut, dann hat da Xilinx intern einiges geändert.

Du hast doch die Website zu XDNA angeschaut. XDNA besteht aus einzelnen Tiles. Bei Phoenix sind es 20. Und es läuft bei XDNA mit den Tiles im Prinzip ebenso wie bei den GPUs mit den CUs.RKCPU schrieb:Aber wie könnte ein Budget AI dann für Kraken Point aussehen?

Aber laut den genannten Spezifikationen taugt Kraken Point nicht als Budget Lösung im Vergleich zu Strix Point. Wenn ich Zen 5c mit 65 % der Fläche von Zen 5 veranschlage komme ich auf eine um ca. 14 % kleinre CPU-Fläche von Kraken Point im Vergleich zu Strix Point. da die CPU-Kerne aber nur einen sehr kleinen Teil der Gesamtfäche ausmachen lohnt sich das nicht.

Wieso sollte das Design wg. AI sterben? Die genannte CPU Konfiguration selbst ergibt keinen Sinn, wenn beides APUs für Notebooks sein sollen.RKCPU schrieb:Wahrscheinlich ist das Design schon gestorben und bald taucht ein neuer Codename auf.

Wenn AMD die AI-Leistung bei Strix Point verdreifacht hat, dann wurde diese Entscheidung schon vor Jahren getroffen. Und dann ergibt es keinen Sinn bei einer zweiten APU auf XDNA zu verzichten.

Diese das Design ist gestoppt worden eingestellt worden ist die Standard Ausrede von Leakern, wenn sie Blödsinn erzählt haben.

Aber Kraken Point geistert nicht nur bei MLID herum. Es fällt auf, dass die Schreibweise zuerst Krackan Point war.

Ähnliche Themen

- Antworten

- 20

- Aufrufe

- 3.091

- Antworten

- 223

- Aufrufe

- 31.163