Mega-GPUs für Nvidia, AMD & Co: TSMC zeigt CoWoS-Package mit >11.600 mm² & 24 × HBM5E

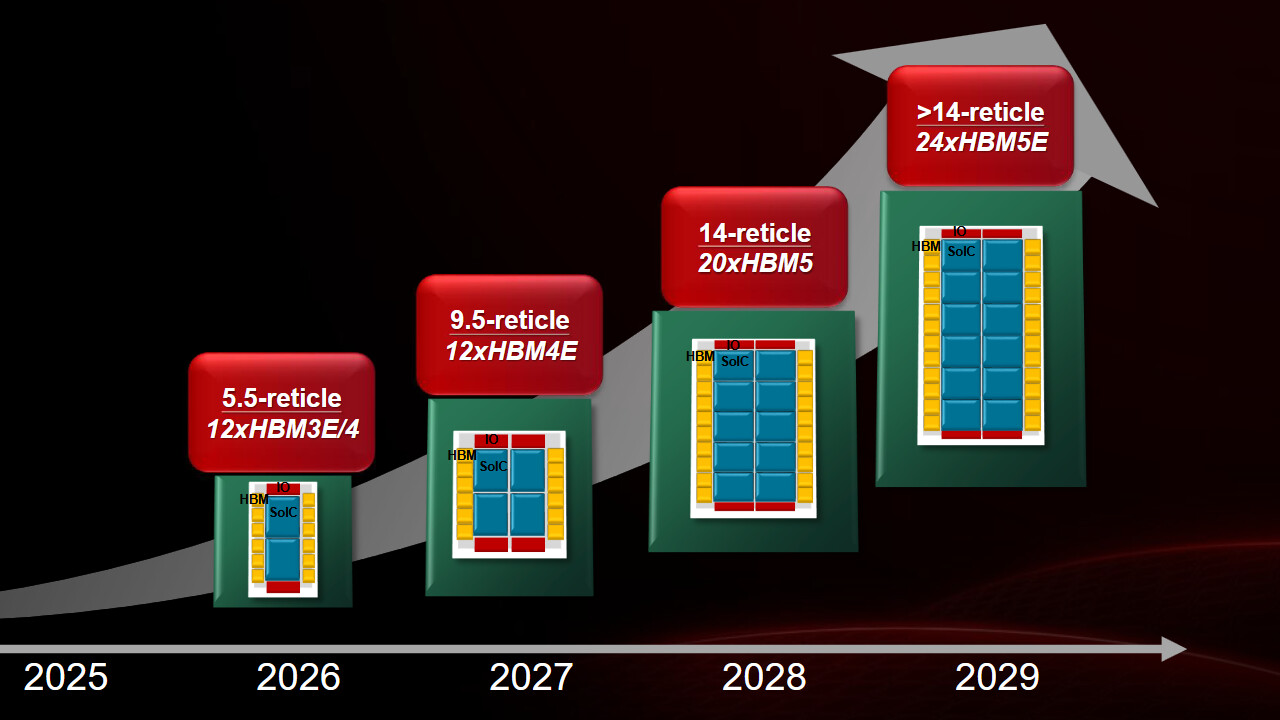

TSMC hat CoWoS als den Standard für das Packaging der kommenden Jahre zum „Technology Symposium“ erneut massiv erweitert. Riesige Chips werden daraus resultieren, vom aktuellen Stand mit einer Größe von ungefähr 5,5 Reticles mit 12 × HBM4 können dann Produkte wachsen, die die Größe von über 14 Reticles mit 24 × HBM5E einnehmen.

CoWoS wächst und gedeiht

Seit 2021 bereits in Produktion, hat sich CoWoS (Chips on Wafer on Substrate) zum Kassenschlager entwickelt. Kein moderner größerer Chip ist ohne diese Technologie verfügbar. In diesem Jahr werden so primär gepackte Chips in der Größe von 5,5 Reticles gefertigt, laut TSMC mit einer Yield-Rate (Ausbeute) von über 98 Prozent. Als Reticle-Size-Limit in der Branche gilt die Maximalgröße eines einzelnen Chips, der mit gängigen (EUV-)Belichtungsmaschinen Kantenlängen von bis zu 26 × 33 mm beziehungsweise 858 mm² haben kann. TSMC nutzt als Berechnungsgrundlage vereinfacht in der Regel 830 mm² als Maximum.

Hatte TSMC im letzten Jahr an gleicher Stelle beim Technology Symposium die Grenze auf 9,5 Reticles verschoben, wird sie in diesem Jahr noch einmal deutlich weiter nach oben gesetzt. Nicht nur werden Größen von 14 Reticles bereits ab 2028 anvisiert, im Jahr darauf soll das ganze Konstrukt noch einmal größer werden können. Ohne exakte Angaben steht hier deshalb ein wenig als Platzhalter nur „>14 Reticles“, Platz für 20 Prozent mehr Speicher gegenüber dem vorangegangenen Maximalausbau ist aber ebenso gegeben.

Umgerechnet sind das über 11.600 mm² Fläche nur für die Chips, das 9,5x große CoWoS-Verfahren brachte es auf 7.900 mm². Der darunter liegende Interposer ist noch größer, TSMC bestätigte ihn letztes Jahr mit bis zu 18.000 mm² für das 9,5x große Reticle, bei >14x dürfte wohl eine nochmals deutlich größere Fläche in Beschlag genommen werden.

SoW-X für 40 Reticles und 64 × HBM

Über all dem wird weiterhin „System on Wafer“ (SoW-X) stehen. Bekanntestes Beispiel dafür sind die aktuellen Wafer-Scale-Produkte von Cerebras. Die Weiterentwicklung dieser Variante wird ab 2029 HBM und Logic direkt auf dem Wafer vereinen können. Und dass die Lösungen dann die Größe von über 40 Reticles erreichen, ist für 2029 ebenso geplant.

Intel Foundry vs. TSMC: Meins ist größer als deins!

TSMC begegnet mit der überraschend aggressiven Roadmap auch zuletzt aufkommenden Gerüchten, Intel könnte die Kundschaft streitig machen. Intel Foundry hatte im letzten Jahr nämlich ein Package gezeigt, welches mit bis zu 12 Reticles bereits größer war, als das, was TSMC bis dato geplant hatte. Intel legte daraufhin im März dieses Jahres nach und bestätigte die Produktionsbereitschaft ab dem Jahr 2028. Der Gegenschlag von TSMC ist deshalb heute umfassend ausgefallen.

Weitere Meldungen und Neuheiten von der Auftaktveranstaltung für dieses Jahr gibt es auf der Themenseite:

ComputerBase hat Informationen zu diesem Artikel von TSMC vorab unter NDA erhalten. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.