TSMC A13/A12-Fertigungsprozess: „1,2 nm“ mit Super Power Rail (ohne High-NA-EUV) ab 2029

Mit den Fertigungsprozessen A13 und A12 geht TSMC in die nächste Dekade. Kombiniert mit Super Power Rail wird A12 die Flaggschiffserie. Realisiert werden soll das alles weiterhin ohne High-NA-EUV, wie TSMC auf Rückfrage verdeutlicht. Die modernsten Low-NA-EUV-Belichter geben das alles problemlos her, erklärt der Hersteller.

Dr. Kevin Zhang, Senior Vice President und Deputy Co-COO bei TSMC (und zuvor auch mal 12 Jahre bei Intel), erläuterte am Vorabend des Symposiums in den USA gegenüber der Presse die kommenden Entwicklungsschritte – mit extrem hohem technischen Verständnis. Auf dem Papier sieht es dabei so aus, als würden die Schritte kleiner werden. Dies ist aber der Zweigleisigkeit geschuldet, die TSMC derzeit fährt: Es gibt einen Standardprozess, und dann eine Linie, die auf BSPD, also die rückseitige Stromversorgung der Chips setzt.

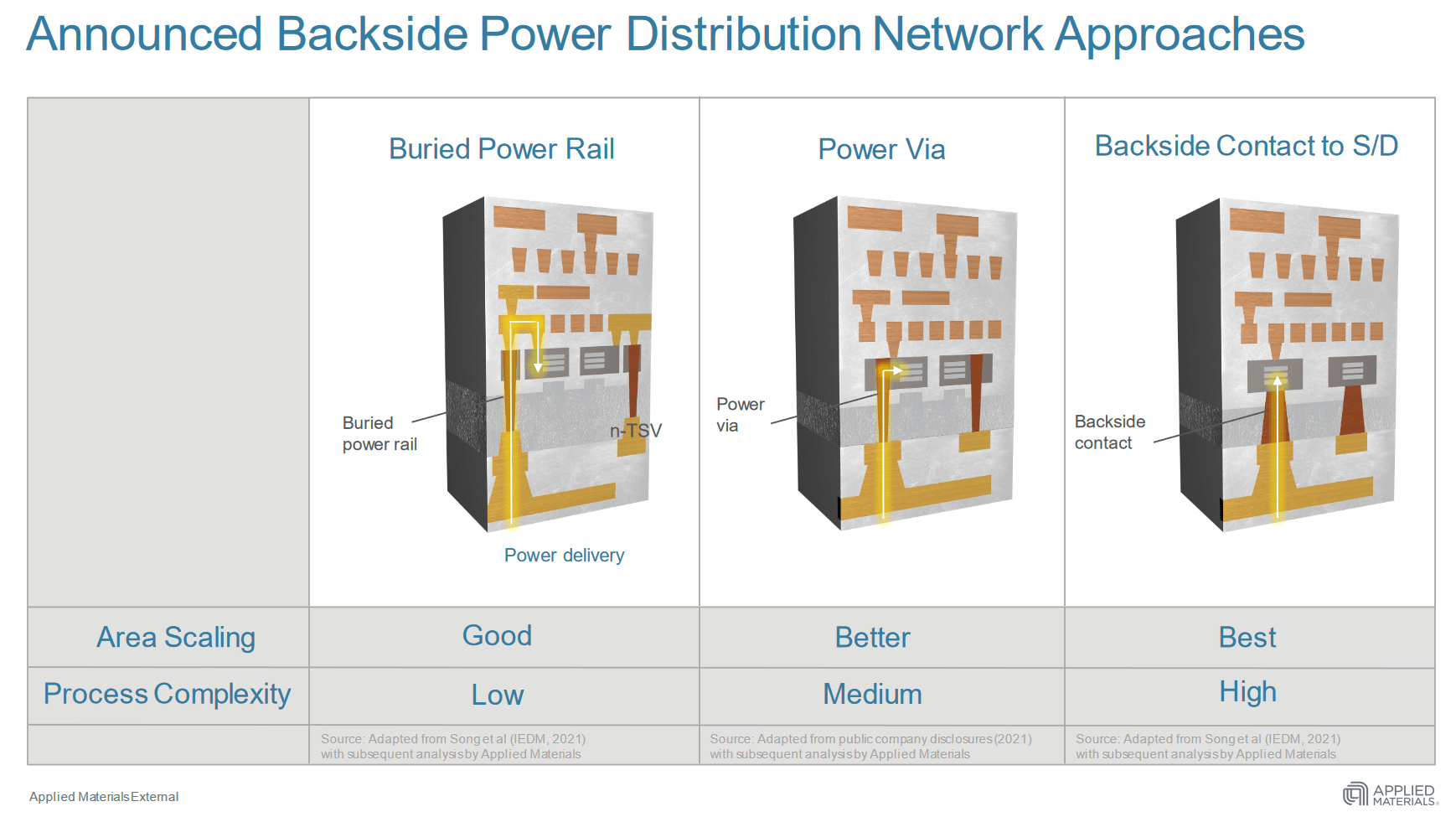

Diese Zweigleisigkeit wird aktuell beim N2-Prozess eingeführt. Denn der kommende Fertigungsschritt A16 ist eigentlich N2 im Herzen, jedoch mit Backside Power Delivery (BSPN) ausgestattet. Der Nachfolger von N2 ohne BSPD wird der A14-Prozess, der Nachfolger von A16 mit BSPD letztlich deshalb A12. Die Basis dafür ist entsprechend der A14-Prozess mit Optimierungen. Auch hier setzt TSMC auf das sogenannte Super Power Rail (SPR), der besten Adaption von BSPD mit direktem rückseitigem Kontakt (die ganz rechte Lösung im Bild). Intel nutzt seit Panther Lake in Intel 18A die mittlere Variante mit Power VIAs.

A14-Prozess bekommt Shrink auf A13

Auf den A14-Prozess folgt im Standardverfahren binnen eines Jahres der A13-Prozess. Dies wiederum ist heutzutage vergleichbar mit dem Schritt von N3E auf N3P oder zukünftig N2 auf N2P. Mit einem optischen Shrink kann etwas Fläche von rund sechs Prozent eingespart werden, hier und da gibt es zudem minimale Vorteile durch den zeitlichen Versatz des Prozesses, sodass zusätzliche design-technology co-optimizations (DTCO) greifen und eine verbesserte Leistung und Effizienz versprechen. Da die Design-Tools und –Regeln identisch bleiben, können A14-Kunden schnell und direkt auf den angepassten Prozess schwenken.

High-NA-EUV bei TSMC weiterhin kein Thema

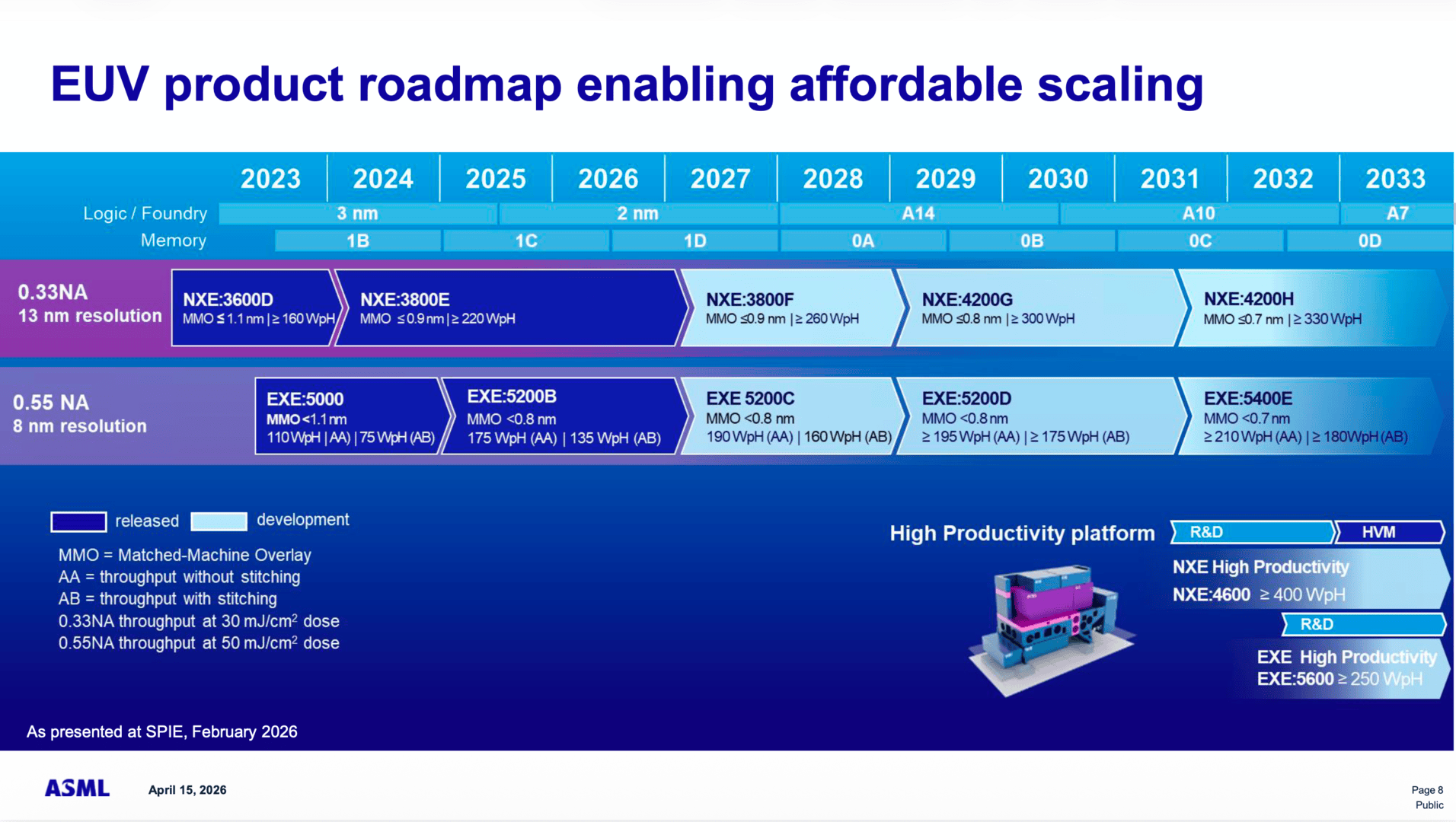

Stolz erklärte Zhang, dass TSMC auch bei den Prozessen für das Jahr 2029 auf High-NA werde verzichten können. Bisher hat das Unternehmen stets eine Möglichkeit gefunden, es wirtschaftlich mit den bestehenden Belichtern zu realisieren – auch heute monierte TSMC den sehr hohen Preis des rund 400 Millionen Euro teuren Systems. Die Entscheidung, wann High-NA bei TSMC zum Einsatz kommt, ist damit erneut vertagt worden, nachdem es im letzten Jahr bereits hieß, dass es vor 2029 nicht gebraucht wird.

Bei Intel könnten die ersten High-NA-Systeme eventuell ab 2027/2028 in der Produktion genutzt werden, aber auch hier klang es zuletzt danach, dass es eher später als früher wird. Ab dem Jahr 2030 dürften die High-NA-EUV-Systeme zudem einen deutlich höheren Reifegrad erreicht haben und so bestehende Low-NA-EUV-Systeme besser ergänzen können. Vermutlich tendiert TSMC erst dann zu einer Integration.

Weitere Meldungen und Neuheiten von der Auftaktveranstaltung für dieses Jahr gibt es auf der Themenseite:

ComputerBase hat Informationen zu diesem Artikel von TSMC vorab unter NDA erhalten. Die einzige Vorgabe war der frühestmögliche Veröffentlichungszeitpunkt.