- Registriert

- Juni 2001

- Beiträge

- 19.968

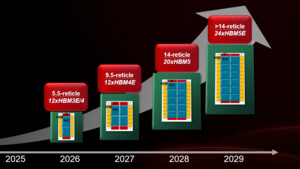

Mit den Fertigungsprozessen A13 und A12 geht TSMC in die nächste Dekade. Kombiniert mit Super Power Rail wird A12 die Flaggschiffserie. Realisiert werden soll das alles weiterhin ohne High-NA-EUV, wie TSMC auf Rückfrage verdeutlicht. Die modernsten Low-NA-EUV-Belichter geben das alles problemlos her, erklärt der Hersteller.

Zur News: TSMC A13/A12-Fertigungsprozess: „1,2 nm“ mit Super Power Rail (ohne High-NA-EUV) ab 2029

Zur News: TSMC A13/A12-Fertigungsprozess: „1,2 nm“ mit Super Power Rail (ohne High-NA-EUV) ab 2029