Philste schrieb:

Das liegt aber zu einem guten Teil auch an dem 8-Kern-CCX.

Da sind wir einer Meinung.

Philste schrieb:

Ich denke bei einer Erweiterung des CCX auf mehr Kerne muss sich AMD entweder vom Ringbus oder von der Niedrig-Latenz-Sache verabschieden.

Das sehe ich ein wenig anders.

AMD kann das CCX nur dann erweitern, wenn sie einen Weg finden dies mit einer niedrigen Latenz hinzubekommen. Der Witz am 3D V-Cache ist, dass der L3-Cache verdreifacht wird, aber die Latenz nur wenig leidet.

Die Sache mit dem Ringbus ist doch ganz einfach, man muss eine Topologie finden die die Anforderungen erfüllt und die dafür erforderliche Anzahl der Links je Kern bereitstellen.

Mike Clark antworte in dem Anandtech Interview auf die Frage nach größeren CXX:

Wir sehen, dass die Anzahl der Kerne steigt, und wir werden die Anzahl der Kerne in unserem Kernkomplex, die unter einem L3 gemeinsam genutzt werden, weiter erhöhen. Wie Sie anmerken, gibt es bei der Kommunikation darüber sowohl Latenz- als auch Kohärenzprobleme, aber so ist die Architektur nun einmal, und dafür haben wir uns entschieden. Dafür leben wir - um diese Probleme zu lösen. Ich möchte also nur sagen, dass das Team bereits überlegt, was nötig ist, um zu einem Komplex zu wachsen, der weit über das hinausgeht, was wir heute haben, und wie wir das in Zukunft erreichen können

Philste schrieb:

Ich denke eher es gibt ein neues Cache-System.

Möglich aber nicht in dem Sinn auf den Du raus willst.

Philste schrieb:

Da gab es ja auch schon Gerüchte zu, Stichwort Ladder Cache.

Ich hatte das krude Zeugs ganz vergessen.

Philste schrieb:

Das hab ich schon damals stark bezweifelt.

Und nun sind wir an des Pudels Kern.

Entweder vertraut man einer Quelle oder man vertraut ihr nicht. Wenn man einer Quelle nicht vertraut kann man sich auch nicht auf sie berufen.

MLID ist keine vertrauenswürdige Quelle. Natürlich sagt er auch Dinge die stimmen, aber niemand weiß heute was stimmt und was nicht.

Michael Günsch macht es übrigens ziemlich deutlich, dass alles aus dem Leak mit Vorsicht zu genießen ist.

Zur Roadmap:

Dass Turin Dense früher fertig wird, halte ich für möglich. Dass Sorano und Turin AI so spät kommen sollen finde ich seltsam. Warten wir ab on AMD tatsächlich in den nächsten Wochen offiziell Server auf Basis von Ryzen 7000 und AM5 freigibt.

Philste schrieb:

Erstens eben wie von dir gesagt aufgrund von N3. Zweitens baut die c Architektur auf der normalen auf und nicht andersrum.

Beide basieren auf derseleben Logikbeschreibung. Es sind lediglich zwei verschiedene Chipdesign. Diese unterscheiden sich darin, dass sie für andere Frequenzbereiche ausgelegt wurden.

Philste schrieb:

Ein guter Teil des Shrinks resultiert ja daraus, dass man die einzelnen Komponenten des Kerns nicht mehr so strikt trennt.

Es Zen 4c ist kein Shrink sonder ein es ist ein weiteres Chip-Design, das keine hohen Frequenzen erreichen muss. Und da die Timing Anforderungen relaxed sind, kann man im Chipdesign mit größeren Partitionen arbeiten.

Philste schrieb:

Das kann aber nur Funktionen, wenn das alles schon in einer funktionierenden Form (im normalen Kern) existiert.

Beim Chip Designs wird die Logikbeschreibung (RTL-Code) auf die tatsächlichen Transistorstrukturen umgesetzt. Chip Design können bereits fertige Designs von IP Blöcke verwenden, aber Chip Designs die für andere Betriebspunkte (a/F) erstellt werden, können per se nicht aufeinander basieren.

Philste schrieb:

Drittens dann alleine noch der Fakt, dass Bergamo deutlich nach Geboa kam, warum sollte der Bergamo Nachfolger jetzt so früh kommen?

Dafür habe ich als Laie folgende Erklärung: Zen 4 brachte SP6. Also musste SP6 validiert werden. Das macht man am besten mit der Mainstreamvariante, sprich Genoa. Nachdem SP6 und IOD grundsätzlich validiert sind kommen die Ableitungen. Hier ist das Validieren wegen der Wiederverwendung von Sockel und IOD erheblich einfacher.

Philste schrieb:

Ich glaube auch einfach nicht, dass AMD vor Anfang 2025 an N3E kommt. Bei N3B hat es vom angeblichen HVM Start ein 3/4 Jahr gedauert, bis Apple was gebracht hat.

TSMC konnte N3 nicht rechtzeitig für den A16 fertig stellen. Den nächsten neuen SoC den Apple bringt, war der A17. Apple veröffentlicht neue Telefone nun Mal im Herbst, und damit hat sich die Auslieferung der ersten SoC mit 3 nm um praktisch 1 Jahr verschoben.

Zu welchem Zeitpunkt und in welchem Umfang TSMC die HVM hochgefahren hat werden wir normal sterblichen nie erfahren. Aber es war C. C. Wei wichtig den Start der HVM für 2022 zu verkünden. Ich halte es auch für sehr unwahrscheinlich, dass TSMC seit Dezember 2022 die Wafer mit A17-SoCs mit voller Pulle produziert.

Philste schrieb:

Wäre seltsam, wenn Apple bei N3E jemand anderem den Vortritt lassen würde.

So wie ich es verstehe ist N3 der Prozess von Apple und N3E der Prozess für die anderen Kunden.

Apple wird nicht auf N3E wechseln. Es wird eine neue Version des PDK von N3 geben, bei der Verbesserungen einfließen.

MediaTek hat Anfang September

verkündet, dass sie das Tape out des ersten Dimensity-SoC in 3 nm abgeschossen haben. Auslieferung im 2. Halbjahr 2024.

Philste schrieb:

Das realistischste scheint mir zu sein, dass der A18 im Iphone 16 Pro im Herbst 2024 das erste Produkt mit N3E ist, alle anderen dürfen dann ein halbes Jahr später liefern.

Also Du glaubst ernsthaft, dass TSMC Apple eine Exklusivität von beinahe 2 Jahren zugesteht?

Philste schrieb:

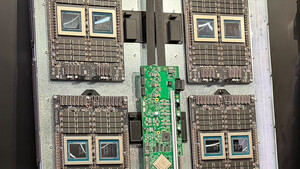

Hier die Dieshots von ZEN4 und ZEN4c:

Anhang anzeigen 1403949

Was fällt auf? ZEN4 hat unzählige deutlich voneinander abgegrenzte Bereiche (Load/Store, Dispatch, Decode etc.). ZEN4c hat das nicht. Woran liegt das? Ganz einfach, es arbeitet nicht ein Team am gesamten Kern. Es gibt ein Team für jeden dieser Bereiche, das sich nur darum kümmert. Das hat den Vorteil, dass bei einem Fehler in einem Bereich die anderen Teams/Teile nicht betroffen sind.

Das steht so weit im Artikel aus dem Du die Bilder hast.

Philste schrieb:

Bei ZEN4 wurden diese Grenzen dann aufgelöst. Die Architektur ist dieselbe wie ZEN4, die einzelnen Teile funktionieren alle. Also kann man sie jetzt mit dem Gesamtbild im Blick so Neuordnen, das alles perfekt platzsparend zusammenpassen kann.

Zen 4c hat größere Partitionen, dass das Design von Zen 4c aus Zen 4 durch das Verschieben von Blöcken abgeleitet wurde ist alleine deine Interpretation.

Du lässt aber den entscheiden Gag des

Artikels aus:

Das bedeutet, dass AMD den Zen-4-Kern direkt hätte schrumpfen können, indem es die Kurve Geschwindigkeit gegen Fläche nach unten verschoben hätte, und der Kern hätte weitgehend ähnlich ausgesehen, allerdings mit einer höheren Zelldichte. Der Zen 4c sieht jedoch aufgrund des folgenden Physical Design-Ansatzes*) ganz anders aus.

Zen 4c sieht aufgrund einer flacheren Designhierarchie*) mit weniger Partitionen ganz anders aus. Bei solch komplexen Core-Designs mit mehreren hundert Millionen Transistoren ist es sinnvoll, den Core in einem Floorplan in verschiedene Regionen aufzuteilen, so dass Designer und Simulationswerkzeuge parallel arbeiten können, um die Markteinführung zu beschleunigen (TTM). Alle technischen Änderungen an einer Schaltung können auch auf eine Unterregion beschränkt werden, ohne dass der Platzierungs- und Routingprozess für den gesamten Kern erneut durchgeführt werden muss.

Die absichtliche Trennung von zeitkritischen Regionen kann auch bei Routing-Engpässen helfen und durch weniger Interferenzen höhere Taktraten erzielen. Wir sehen ARMs Neoverse V1- und Cortex-X2-Cores ohne harte Trennwände zwischen logischen Regionen, wobei die Platzierung so dicht wie möglich gepackt ist. Die Regionen erscheinen homogen, wenn man sich den physischen Chip ansieht. Auf der anderen Seite sehen wir Intels Crestmont E-Core mit vielen sichtbaren Partitionen, wobei die Grenzen lila hervorgehoben sind.

Wie in unseren Zen 4-Kernkommentaren zu sehen ist, gibt es zahlreiche Partitionen für jeden logischen Block innerhalb des Kerns, was in Zen 4c mit nur 4 Partitionen (L2, Front End, Execution, FPU) drastisch reduziert wurde. Durch die Zusammenlegung dieser Partitionen aus Zen 4 können die Regionen enger zusammen gepackt werden, was eine weitere Möglichkeit zur Flächeneinsparung bietet, indem die Standardzelldichte weiter erhöht wird. Man kann sagen, dass AMDs Zen 4c "wie ein ARM-Core aussieht.

*) Der Physical Design Ansatz auf den verwiesen wird ist die flachere Designhierarchie mit weniger Partitionen.

Kurz zusammengefasst:

- Die Ähnlichkeit von Arm-Kerne und Zen 4c Kerne resultiert darauf, dass sie für niedrigere Frequenzen ausgelegt sind. Beide können deshalb mit einer flachen Designhierachie mit wenigen großen Partitionen erstellt werden.

- Die hohen Frequenzen von Zen 4 erfordern das Designen mit einer tiefen Designhierarchie mit vielen kleinen Partitionen.

- Die flache Designhierarchie ermöglicht eine höhere Packungsdichte