sheng

Lt. Commander

- Registriert

- Apr. 2010

- Beiträge

- 1.235

Hallo Leute,

ich stelle mir gerade ein paar Fragen nach den verfügbaren und genutzten PCIe Lanes meines Systems. Ich habe mich bisher nicht sonderlich mit dem Thema auseinandergesetzt, außer ein wenig gegoogelt. Vielleicht könnt ihr mir weiterhelfen?

Folgende Hardware kommt zum Einsatz:

CPU: Intel Core i7-6700K

PCIe-Lanes: 16x PCIe 3.0

PCI Express Configurations: 1x16, 2x8, 1x8+2x4

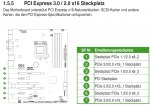

Mainboard: ASUS Z170-A

PCIe-Lanes: 20

Und nun zur Belegung

Es ist ja diverse Hardware vorhanden, die die entsprechenden Lanes belegt:

PCIe Storage

1x M.2/M-Key (PCIe 3.0 x4)

Status: belegt

Verbrauch Chipsatz-Lanes: x4

PCIe Grafikkarte

PCIe 3.0 x16

Status: belegt

Verbrauch Chipsatz-Lanes: ???

Jetzt kommen die Fragen:

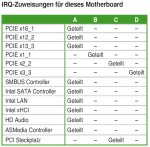

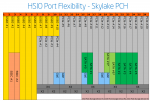

Belegt die Grafikkarte auch Chipsatz-Lanes? Oder nur die der CPU?

Was belegt noch Lanes?

Wenn ich noch eine x1 Soundkarte einbaue, was passiert dann? Grafik x16 + M.2 PCIe SSD x4 + Soundkarte x1 = 21. Wird dann wo was abgezogen.

Und rein hypothetisch, wenn ich eine M.2 PCIe SSD nicht über M.2 sondern über einen PCIe Adapter (x4) direkt an einem PCIe Slot betreibe, ändert sich an der Belegung etwas?

Danke für die Erleuchtung =)

Grüße

sheng

ich stelle mir gerade ein paar Fragen nach den verfügbaren und genutzten PCIe Lanes meines Systems. Ich habe mich bisher nicht sonderlich mit dem Thema auseinandergesetzt, außer ein wenig gegoogelt. Vielleicht könnt ihr mir weiterhelfen?

Folgende Hardware kommt zum Einsatz:

CPU: Intel Core i7-6700K

PCIe-Lanes: 16x PCIe 3.0

PCI Express Configurations: 1x16, 2x8, 1x8+2x4

Mainboard: ASUS Z170-A

PCIe-Lanes: 20

Und nun zur Belegung

Es ist ja diverse Hardware vorhanden, die die entsprechenden Lanes belegt:

PCIe Storage

1x M.2/M-Key (PCIe 3.0 x4)

Status: belegt

Verbrauch Chipsatz-Lanes: x4

PCIe Grafikkarte

PCIe 3.0 x16

Status: belegt

Verbrauch Chipsatz-Lanes: ???

Jetzt kommen die Fragen:

Belegt die Grafikkarte auch Chipsatz-Lanes? Oder nur die der CPU?

Was belegt noch Lanes?

Wenn ich noch eine x1 Soundkarte einbaue, was passiert dann? Grafik x16 + M.2 PCIe SSD x4 + Soundkarte x1 = 21. Wird dann wo was abgezogen.

Und rein hypothetisch, wenn ich eine M.2 PCIe SSD nicht über M.2 sondern über einen PCIe Adapter (x4) direkt an einem PCIe Slot betreibe, ändert sich an der Belegung etwas?

Danke für die Erleuchtung =)

Grüße

sheng

Anhänge

Zuletzt bearbeitet: