Piak schrieb:

Das Tempo das TSMC an den Tag legt ist Wahnsinn. Sie ruhen nicht, obwohl sie schon führen. Insofern gönne ich Ihnen auch den Erfolg.

Intel, Nokia und andere wurden für mangelden Fortschritt "belohnt"

Nokia hat sich nicht ausgeruht. Das iPhone machte von heute auf morgen ein Touch-Interface zur Pflicht. Das hatte Nokia nicht. Nokia konnte/wollte es nicht selbst entwickeln und hat mit Windows Phone aufs falsche Pferd gesetzt. Hätte Nokia auf Android gesetzt, wäre IMO das ganze viel besser für Nokia gelaufen.

Bei Intel ist es erheblich komplizierter. Die Position die Intel 2014 bei den Clients und Servern erreicht hatte, beruhte zu großen Teilen auf der überlegenen Halbleiterfertigung und/oder den Fehlern der Konkurrenz und nur teilweise auf dem Können der CPU-Architekten bei Intel.

- Die Halbleiterfertigung von Intel war exakt auf die Bedürfnisse der CPUs (High Performance) zugeschnitten und war den Foundries im Jahr 2014 auch noch um 1 1/2 Generationen voraus.

- AMD mussten den K9 einstampfen, hatte im K10 den berühmt berüchtigten TLB Bug und dann kam mit Bulldozer (K11), einer verrückten Wette, der klassische Fehlschlag. Mit diesem Hattrick hätte AMD sich beinahe selbst abgeschossen.

- Bei den Klassischen Serveranbietern mit RISC Architektur ging es schon in den 2000er bergab. HP hat die erfolgreiche HP PA wegen Itanium eingestellt. Die anderen bis auf IBM mussten aufgeben, weil sie in Preisleistung gegen X86 nicht standhalten konnten. Allen gemeinsam war, dass sie keinen Zugriff auf eine Halbleiterfertigung hatten, die der von Intel auch nur halbwegs ebenbürdig war.

Nagilum99 schrieb:

Intel hat sich bekanntermaßen verschluckt. Das passiert, wenn man etwas überschätzt.

Es ist nicht so, dass sie sich einfach ausgeruht haben - auch wenn das Märchen sich bei einigen hartnäckig hält.

Wenn Du damit auf das 10 nm Debakel anspielst, nur weil Bob Swan die Geschichte so erzählt hat, muss sie noch lange nicht stimmen.

Es ist klar, dass 7 nm Nodes, wenn man DUV*) verwendet nur mit SAQP (Self Aligned Qudrupel Pattering) und (Self Aligned Double Patterning) umsetzbar sind.

Angaben von Wiki Chip zur Verwendung vom Patterning bei N7

https://en.wikichip.org/wiki/7_nm_lithography_process#N7

Aus einem Vergleich von Intel 4 und Intel 7:

https://www.semiconductor-digest.co...ried-and-tested-copper-with-cobalt-liner-cap/

Die Werte von Intel 7 aka 10 nm sind nicht ambitionierter als TSMC 7 nm, eher anders herum. Lediglich bei M1 liegt Intel tiefer, ansonsten liegt TSMC tiefer. 10 nm war also nicht zu ambitioniert, es könnte allerdings sein dass Intel, das Multi Patterning nicht in den Griff bekam.

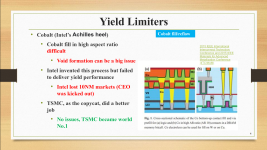

Der Schlüssel bei den Problemen mit 10 nm wird allerdings beim Einsatz von Cobalt bei M0 und M1 gesehen. Das wurde bei 10 nm aka Intel 7 eingeführt. Intel 4 ging wieder davon weg und verwendet bei M0 bis M4 enhanced Copper (eCU).

Enhanced Cooper entspricht, dem was TSMC seit 16 nm in den kleinsten Metallisierungsebenen einsetzt.

Und ein ganz wichtiger Faktor ist IMO, dass im Zeitraum bevor das 10 nm Debakel losging, sehr viele erfahrene Halbleiterexperten Intel verlassen haben. Dass es bei der Einführung eines neuen Nodes Herausforderungen und Probleme gibt, ist normal und gehört zum Geschäft. Nicht normal war, dass Intel diese Probleme erst nach einigen Jahren und mehrere Anläufen in den Griff bekam.

*) Ebenso ist die Geschichte Unsinn, dass es daran gelegen hätte, weil Intel kein EUV verwendet hätte.

- Zu dem Zeitpunkt an dem 10 nm ursprünglich fertig werden sollte, war EUV nicht für eine HVM bereit.

- TSMC hat 7 nm ohne EUV umgesetzt, also das erforderliche Multi Pattering gemeistert. Erst als 7 nm fertig war, hat TSMC in N7+ (2019) bei einigen Masken EUV eingesetzt. Und dadurch Erfahrung gesammelt, die TSMC bei 5 nm (2020) sehr geholfen haben.

- Ein Zufallsfund zu GF: https://ieeexplore.ieee.org/document/8268476, offensichtlich wollte GF es bei 7 nm zuerst auch ohne EUV probieren und erst später EUV einführen.

- Samsung hat die ersten EUV Anlagen IIRC im Jahr 2019 in die HVM integriert.

- Intel hatte schon längst EUV Anlagen in den Entwicklungsabteilungen. Intel konnte also abschätzen ob EUV HVM tauglich war oder nicht.

- Bob Swan (CEO von Januar 2019 bis Februar 2021) hatte den Plan sich von der Halbleiterfertigung zu trennen. Nach zwei Jahren bekam das Board kalte Füße und hat dann doch Pat Gelsinger geholt, mit dem man sich 2019 nicht geeinigt hat, weil er die Halbleiterfertigung weiterführen wollte. Pat Gelsinger hat eine 180° Kehrtwende hingelegt. Aber auch Pat Gelsinger hat erst die ersten EUV Systeme für die HVM erst für Intel 4 angeschafft.

Im übrigen hat EUV seine ganz eigenen Probleme. Mit EUV einen hohen Waferdurchsatz und einen hohen Yield zu erzielen, ist eine ganz besondere Herausforderung.

Alleine schon die kleinere Wellenlänge des Lichts hat auch unerwünschte Folgen. Zum Beispiel steigt die Energie der Photonen im Vergleich zu DUV um mehr als den Faktor 10.

https://general.chemistrysteps.com/calculate-energy-of-a-photon/

eastcoast_pete schrieb:

Deshalb hab ich ja "laut eigenen Angaben " geschrieben. Ganz irrelevant ist GAA bei Samsung trotzdem nicht, und erwähnen muss man sie um vollständig zu sein.

Auf die Frage nach Samsung, genügt es zu erwähnen, dass Samsung Foundry noch nichts

relevantes mit GAA geliefert hat. Obwohl Samsung schon vor fast drei Jahren bei GAA ganz laut erster gebrüllt hat.

Wenn Samsung mit 3 nm oder 2 nm etwas relevantes liefert, kann man wieder über Samsung reden. Aktuell kursieren jede Menge Gerüchte, die sich allerdings widersprechen. Und selbst von Samsung selbst hört man widersprüchliches.

Und da wir in einem AMD Thread sind:

Alle paar Monate werden Geschichten erfunden, AMD ließe demnächst bei Samsung fertigen. Mal ist die Rede von einem konkreten Produkt/Die, Mal ist die Rede AMD wechselt mit mehreren Dies oder gar bei einem kompletten Node zu Samsung.

Auf eine dieser Geschichten angesprochen hat Lisa Su zurückgefragt: "Do you believe Korean media outlets?"

Wenn wieder einmal der Blödsinn kursiert AMD ließe bei Samsung Foundry fertigen, einfach nochmal die

Pressemitteilung lesen, die dieser News zugrunde liegt.

Kazuja schrieb:

Auch ja, aber auch noch ein Haufen andere Themen:

Die gibt es ganz sicher. Das größte Thema ist die Folklore über Intel, die die Sicht verstellt.

Intels Erfolgsgeschichte mit den x86 Prozessoren hat die Schattenseite, dass Intel das Speichergeschäft aufgeben musste und dabei 1/3 der Belegschaft rausgeekelt und rausgeschmissen hat. Und massenhaft Leute rauszuschmeißen zieht sich seit dem, wie der rote Faden durch die Historie von Intel. Hier hat sich vor allem Brian Krzanich Unmut zugezogen, weil er Leute rausgeschmissen hat, um Geld für neue Geschäftsfelder frei zu schaufeln und gleichzeitig Aktien für Milliarden von Dollar zurückgekauft hat. Mit seinen Investments war Brian Krzanich nicht erfolgreich. Intel hat Altera für 16,7 Milliarden USD gekauft und diese Woche einen 51 % Anteil für 4,46 Milliarden verkauft. Während der Preis anderer Halbleiterunternehmen explodiert ist, hat es das Missmanagement von Intel geschafft den Preis von Altera zu halbieren.

Ganz besonders übel wird Brian Krzanich genommen, dass er mit dem Geld, das er auch bei der Entwicklung von Halbleiterprozessen und von CPUs eingespart hat, Drohnenhersteller gekauft hat.

Kazuja schrieb:

hab mal gelesen das leitende Ingenieure bei Intel, wie „Beamte“ nur mit Aktienanteilen von Intel aufgetreten sind.

Davon habe ich noch nie etwas gehört.

Andy Grove hatte bei Intel ein System eingeführt, das das Gehalt strikt an das Erreichen der vereinbarten Ziele bindet. Pat Gelsinger hat nach seiner Rückkehr lautstark moniert das Brian Krzanich dieses System abgeschafft hat. Pat Gelsinger hat es wieder eingeführt in seinem Bestreben zu den guten alten Zeiten zurückzukehren.

Im

Interview mit Ian Cutress für Anandtech im Juni 2021 hat Jim Keller über seine Zeit bei Intel gesagt:

Alle dachten, das Mooresche Gesetz sei tot, und ich dachte: „Heiliger Strohsack, das ist die Firma mit dem Mooreschen Gesetz! Es war wirklich lästig, wenn [als Ingenieur] dein Hauptthema war, dass [das Moore'sche Gesetz tot ist], denn ich dachte, dass es das nicht war.

Übersetzt mit DeepL.com (kostenlose Version)

Und hier hat sich IMO sowohl in der Halbleiterfertigung als auch im Chipdesign/CPU Architektur die ungesunde Haltung eingeschlichen, wenn wir (die allerbesten) es nicht (besser) hinbekommen, dann bekommen es die anderen erst recht nicht hin.

Eine weiteres Zitat aus diesem Interview über Intel:

Ich hatte gedacht, ich würde dorthin gehen, weil es dort einen Haufen neuer Technologien zu bauen gäbe. Ich verbrachte die meiste Zeit damit, mit dem Team an organisatorischen und methodischen Veränderungen zu arbeiten, z. B. an neuen CAD-Tools, neuen Methoden und neuen Wegen zur Chipentwicklung. Ein paar Jahre vor meinem Eintritt in das Unternehmen wurde die so genannte SoC-IP-Ansicht für die Chipentwicklung eingeführt, im Gegensatz zu Intels historischer monolithischer Ansicht. Um ehrlich zu sein, lief das nicht so gut, denn man nahm die monolithischen Chips, die großartigen Client- und Serverteile, und zerlegte sie einfach in Teile. Man kann sie nicht einfach in Stücke brechen - man muss diese Teile und einen Teil der dazugehörigen Methodik tatsächlich neu aufbauen.*)

Übersetzt mit DeepL.com (kostenlose Version)

Das ist nur eine von vielen Stimmen, die besagen, dass die Chipentwicklung von Intel veraltet war. Dies war nicht behoben als Jim Keller zu Tenstorent ging. Pat Gelsinger sprach im Bezug auf die Chipentwicklung von "mess" (Chaos, Durcheinander Schlamassel). Man muss sich nur das Drama mit Sapphire Rapids anschauen. Intel benötige 12 Steppings. Das ist ein Problem vor allem im Chip Design und eher nicht der Halbleiterfertigung.

*) Das Zitat zur SoC-Entwicklung muss man im Kontext zu dem sehen was AMD mit dem Infinity Fabric gemacht hat, siehe verlinktes Video unten.

Veränderungen in einer erfolgreichen Organisation sind schwer. Hier hat das Totschlagargument gegen Veränderungen Gewicht: "Das haben wir schon immer so gemacht". In Unternehmen in denen es nicht gut läuft, provoziert dieser Spruch nur eine Antwort: "Eben". D. h., das haben wir schon immer so gemacht, ist in dieser Situation ein Argument für die Änderung.

Das berühmteste Zitat von Andy Grove war: "Erfolg führt zu Selbstzufriedenheit. Selbstzufriedenheit führt zu Misserfolg. Nur die Paranoiden überleben."

Die eine Tragik war, dass Andy Grove nicht bemerkt hat dass sich die Selbstzufriedenheit*) bereits zu seiner Zeit bei Intel breit gemacht hatte. Die zweite Tragik war, dass Intel alle Inflection Points**) seit 2000 verpasst hat. Obwohl Intel duzende Milliarden USD dafür ausgegeben hat, um neue Geschäftsfelder zuzukaufen oder aufzubauen.

*) Aus Selbstbewusstsein wird Selbstüberschätzung, Geringschätzung von Konkurrenz und Kunden.

**) Inflection Points sind Ereignisse, Technologien oder Entwicklungen die Branchen grundlegend verändern. Andy Grove berühmtes Buch "Only the Paranoids Survive" hatte Inflection Points zum Thema. Wie man sie erkennt, meistert und für sich nutzt.

Kazuja schrieb:

Stell dir vor, du bis 52 Jahre alt und hast 40 Mio.$ in Intel Aktien in deinem Depot und sollst krass den Laden auf Vordermann bringen mit Innovationen. So ungefähr.

Wo ist das Problem, wenn man Ingenieur sein will? Und offensichtlich will jemand der Aktien für 42 Millionen USD in seinem Depot hat und noch als leitender Ingenieur arbeitet, immer noch Ingenieur sein.

Die Geschichten, die ich gehört habe, laufen darauf hinaus, dass sich die Intel Leute nicht vom PC lösen konnten und deshalb die Anforderungen der Mobil Phones nicht wirklich verstanden haben. Den Erfolg im PC Markt konnte Intel auf die Server ausweiten. IMO vor allem Dank der auf High Performance optimierten Halbleiterfertigungstechnik.

Aber das war es dann. Alle anderen Versuche neue Geschäftsfelder neu aufzubauen sind letztendlich gescheitert. Außerdem hat Intel vor lauter Konzentration auf den PC Markt den Embedded Markt bis auf ein paar Nischen Arm überlassen.

Kazuja schrieb:

Wenn jemand „satt“ ist und genug hat (Intel war ja Weltmarktführer Jahre lang) dann hat er nicht mehr soviel Motivation sich weiterzuentwickeln. Veränderungen einzuleiten etc.

Wer sich als Ingenieur nicht mehr weiterentwickeln will, muss den Job sofort an den Nagel hängen. In einer gesunden Firmenkultur passiert das auch.

IMO ist das Problem ein anderes und eben nicht auf individueller Ebene*). Das Unternehmen erkennt nicht, dass sich die Spielregeln ändern und dass das alte Erfolgsrezept oder Geschäftsmodell nicht mehr funktioniert. Andy Grove hat nicht umsonst von Inflection Points geschrieben. Intel wurde durch den Inflection Point Personal Computer ganz groß und unglaublich erfolgreich. Alle erfolgreichen Anbieter von Mini Computern haben den PC als Spielzeug abgetan. Sie wollten nicht wahrhaben, dass der PC ihren Markt auffressen wird. Weil sie gar nicht oder viel zu spät auf die neuen Gegebenheiten reagiert haben, wurden sie vom Markt gefegt.

*) Wenn man Mal vom Firmengründer absieht, den alle verehren und bei dem es niemand wagt zu widersprechen.

Nagilum99 schrieb:

Außerdem war Pat Gelsinger z.B. immer ein "Vollblutintelianer", der hat wohl deutlich mehr Kohle und wurde ganz sicher unfreiwillig gegangen, bevor sein Werk vollendet war.

Bei Pat Gelsinger könnte man so wie er als CEO agiert und geredet hat, sogar von Übermotivation reden.

Der neue Intel CEO macht den Job nicht wegen des Geldes, ihn reizt die Aufgabe und die Chance der Retter von Intel zu werden.

Lisa Su macht auch nicht den Eindruck dass sie demnächst aufhören will. Ihr Aktienpacket ist ein bisschen größer.

Molokai schrieb:

Ob das bei GPUs auch eine Rolle spielt?

GPUs profiteren mindestens ebenso wie CPU von neuen Nodes.

GPUs haben in der Regel große Dies. Sie werden erst dann auf dem neuen Node hergestellt, wenn die Fehlerrate des Prozesses weit genug gesunken ist. Dann wird auch bei den großen Dies eine gute Ausbeute (Yield) erreicht. Das ist der Grund, warum GPUs später auf einen neuen Node wechseln.

Kazuja schrieb:

Klar absolut, Veränderungsprozesse und Innovationen sind möglich und es gibt richtig gute Beispiele dafür.

AMD, Porsche (die Zeit unter

Wendelin Wiedeking), IBM und auch Intel wird seinen Weg gehen, denke ich.

Ich wollte mit meinem Beitrag nur darauf hinaus, dass es bei AMD und auch bei Intel mehr benötigt als „nur“ eine Frau Dr. Su.

Lassen wir Mal Jim Keller antworten, aus demselben Interview:

Alle waren der Meinung, dass das AMD-Team nicht geradeaus schießen konnte, und ich war sehr fasziniert von der Möglichkeit, einen wirklich großartigen Computer mit dem Team zu bauen, von dem alle dachten, es sei überfordert. So wie niemand dachte, dass AMD ein großartiges CPU-Designteam hätte. Aber wissen Sie, die Leute, die Zen entwickelt haben, hatten 25 bis 30 Jahre Berufserfahrung bei AMD. Das war der Wahnsinn.

Bulldozer und Zen waren dieselben Leute. Warum haben sie Bulldozer vergeigt und bei Zen sehr gute Arbeit abgeliefert?

Bei AMD brauchte es laut Joe Macri zwei Leute um die Veränderungen anzustoßen, Lisa Su und Mark Papermaster:

Joe Macri beschreibt wie wichtig Lisa Su und Mark Papermaster waren. Beide dafür gesorgt dass die Entwicklungsmethologie bei AMD neu aufgebaut wurde, was bei den CPUs die eigentliche Aufgabe von Jim Keller bei AMD war. Der macht im Interview sehr klar, dass er nicht direkt an Zen gearbeitet hat. Er hat das Team neu aufgestellt, dass Zen gebaut hat.

Der Vortrag von Joe Macri ist von 2019 und ist absolut sehenswert. Alleine die Schilderung der Probleme der Halbleiterfertigung, die seit dem Ende von Dennart's Law auftraten, ist brilliant. Ab Minute 29 driftet Joe Macri bei seiner Vision für den PC in 10 Jahren, IMO ein bisschen zu sehr ins Science Fiction ab.

In diesem Vortrag wird übrigens deutlich, dass AMD zuerst das SoC um den Infinity Fabric herum komplett neu aufgebaut hat und erst dann das SoC in Chiplets zerlegt hat. An den Schnittstellen der Chiplets musste AMD somit "nur" den Inifinity Fabric wieder verbinden. Das geschah bei den CPUs über Infinity Fabric over Package (IFOP). Strix Halo verwendet das erste Mal ein Interface in der vollen Breite des Infinty Fabrics und verzichtet auf SERDES. Das wurde auch als Sea of Wires bezeichnet.

Um ein bisschen On Topic zu werden:

Wenn Strix Halo wie viele sagen ein Vorgeschmack auf Zen 6 ist, wird Zen 6 wird das was AMD bei Zen 2 begonnen hat, auf eine ganz neue Basis stellen. Die Änderungen beim Packaging sind ebenso wichtig

Kazuja schrieb:

Die „Mannschaft“ muss mitziehen und das ist bei einem Unternehmen wie Intel manchmal nicht so einfach.

Um mitziehen zu können muss schon jemand in die richtige Richtung ziehen. Das bedeutet die Firmenleitung muss wissen in welche Richtung es gehen soll. Und das muss sie der Mannschaft vermitteln. Das funktioniert nur wenn die Mannschaft der Firmenleitung vertraut, an die Ziele glaubt und an sich selbst glaubt.

Das Problem bei Intel ist nicht in erster Linie die Mannschaft. Die Führung, die Strukturen und die Kultur sind bei Intel das Problem.

https://x.com/ctnzr/status/1737561214048186680

https://x.com/RajaXg/status/1892222720710152315

Der Kern des AMD Advanced Packaging Teams kam von Intel, auch wenn es Raja Swaminathan nur zwei Jahre bei Intel ausgehalten hat. Sie haben den Abgang von Brian Black kompensiert, der HBM entwickelt hat.

Jim Keller beschreibt im Interview mit Ian Cutress sehr gut, wie es gelungen ist die CPU-Entwickler von AMD zu überzeugen, dass sie einen high performance Kern bauen können. Im

Interview mit Mike Clark, dem letzten Interview, das Ian Cutress für anadtech gemacht hat, hat er Mike Clark auf dieses Meeting angesprochen. Mike Clark hat gesagt, dass die CPU Entwickler, die nicht überzeugt waren, gegangen sind. Das waren viele gute Leute.

Aber es war IMO wichtig dass sie gegangen sind. Sie sind nicht geblieben und haben sich den notwendigen Änderungen in den Weg gestellt. Aber das Gehen fällt bei einem Unternehmen das in den Untergang schlittert viel leichter als beim dominierten Marktführer.

mae schrieb:

Von Skylake bis Comet Lake gab es tatsaechlich keine IPC-Verbesserung, zwischen Sandy, Haswell, und Skylake aber schon.

Hier ein paar Daten dazu.

Es gibt durchaus einige Benchmarks in der Grafik, bei denen die Steigerung von Haswell (2013) zu Skylake (2015) steiler ist als die von Skylake zu Rocket Lake (2021, aber im Prinzip Ice Lake von 2019), z.B. fib. Es gibt auch andere Faelle.

Diese Grafik die Du ohne jeden Kontext her zauberst zeigt wie sich die IPC bei ein paar Microbenchmarks entwickelt hat. Microbenchmarks zeigen Auswirkungen von Änderungen der Microarchitektur oder von Optimierungen der Compiler sehr gut. Mit Microbenchmarks kann man zeigen wo eine Mikroarchitektur sehr gut ist oder wo sie Probleme hat.

Einzelne Microbenchmarks haben keine Aussagekraft über die Alltagsperformance dieser Architekturen. Und den Quasi Stillstand den alle Empfunden haben, gab es bei der Alltagsperformance.

Ich finde übrigens diese ganze Diskussion über den Performancezuwachs bei Intel in den 2010er witzlos. Schaut Euch doch Mal die jeweiligen Ankündigungen von Intel und die Tests von CB zu den einzelnen Releases an.

Vor allem überseht ihr den wesentlichen Aspekt. Durch die Explosion der Anzahl der Kerne hat sich die Charakteristik der Serverprozessoren grundlegend geändert. In den 2000er haben die Server Prozessoren massiv von den High Performance Prozessen von Intel profitiert. High Performance ist heutzutage nur noch in wenigen Nischen relevant. Heute sind für Server Prozessoren so wie bei den GPUs Prozesse notwendig, die auf wenig Power und hohe Dichte optimiert sind. Bei Notebooks sind auf wenig Power optimierte Prozesse wichtig.