stefan92x schrieb:

Andererseits springt dann hier aber der L3 schon von 32 MB auf 48 MB. Und generell gilt ja für den L3 folgendes: Er beschleunigt Anwendungen, wenn die Daten im Cache liegen. Je größer er wird, umso größer die Wahrscheinlichkeit, dass die Daten da drin nicht in absehbarer Zeit gebraucht werden.

Als Ergänzung, den Cache zu vergrößern bedeutet oft die Latenz des Caches zu erhöhen. Die Größe des Caches und seine Latenz muss sehr fein abgestimmt werden.

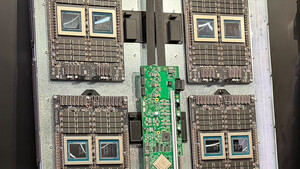

Der 3D V-Cache hat die Latenz nur ein kleines bisschen erhöht aber sehr viel mehr Cache bereitgestellt. Die die zweite Schicht des 3D V-Caches wird wiederum die Latenz erhöhen. Die Frage ist nun um wie viel steigen die Cache Hits und kann dies die höhere Latenz kompensieren?

stefan92x schrieb:

Wenn AMD wirklich das Packaging umbaut und den IF statt über das Substrat durch das Package führt, dann halte ich das für möglich.

Das Infinity Fabric ist ein On-die Bus mit bisher 256 bit Breite (32Byte/Clock). Dieser Bus wird mit ca. 2 GHz getaktet. Bei den APUs ist der Takt eher niedriger um den Stromverbrauch zu begrenzen.

Bei den Chiplet CPUs wird der Infinity Fabric als Infinity Fabric on Package (IFoP) über das Substrat geführt. Dazu verwendet AMD PCIe Serdes, die mit weniger Power arbeiten, denn sie müssen das Signal nicht über das Mainboard treiben sondern nur über das Substrat. Bei Zen 2 erfolgte übertragen das mit 2 pJ/bit. Da der IFOP AFAIU nur 16 Lanes hat, muss die Übertragungsrate entsprechend hochgesetzt werden.

Wenn AMD den Infinity Fabric doppelt so hoch taktet, steigt die Power erheblich an. Es gibt auch die Möglichkeit den Infinty Fabric breiter zu machen.

Nightspider schrieb:

Wir diskutieren hier gerade über Leaks. Wenn wir je nach Meinung plötzlich manche Aussagen abtun als Clickbait dann brauchen wir auch gar nicht mehr diskutieren.

Bei Leaks ist immer Vorsicht anfgebracht. Bei MLID ist immer große Vorsicht angebracht.

Nightspider schrieb:

MLID hatte in letzter Zeit Rechts mit AMD Leaks,

MLID hatte Glück mit den Leaks zu Zen 5, die Folie die MLID im September 2023 gezeigt hat war authentisch. Sie ist aber auch anderen zugespielt worden, aber Kepler hielt sie für Fake, weil da nur 10 bis 15 % IPC Steigerung stand.

Das was MLID zu RDNA4 verzapft hat war nicht so toll.

Nightspider schrieb:

er hat offensichtlich Quellen bei AMD.

Extrem unwahrscheinlich. Aber AMD muss Informationen mit Partnern teilen und je mehr Personen bescheid wissen, desto eher kommt was raus. Folien werden vergessen oder mache leute schauen sich im Flugzeug auf dem Notebook geheime Unterlagen an, ... Oder ein Kunde quatscht zu viel, wie der Leiter des HLRZ.

Und dann tauchen diese Infos im Web auf.

Nightspider schrieb:

Die Latenz zwischen den CCDs ist einfach zu hoch. Das wird sich aber auch bei Zen 6 ändern.

Die Messungen die zu Strix Halo veröffentlicht wurde zeigen keine Änderung der Latenzen im Vergleich zum 9950X.

Wo sollen die Änderungen auch herkommen, das einzige was entfällt sind die SERDES zwischen den Dies.

Nightspider schrieb:

Bei Zen7 EPYC soll sogar jeder CPU Chiplet V-Cache bekommen - immer. Es gibt keine CPU Chiplets mehr ohne V-Cache Layer. Dort sollen es angeblich 7 MB L3 pro Kern werden, was 75% mehr L3 wäre als bei aktuellen AMD EPYC CPUs mit 4 MB pro Kern.

Hier ist MLID teilweise zurückgerudert, es soll versionen mit L3 Cache im CPU Die geben und versionen ohne L3 cache im CPU Die. Warten wirs in Ruhe ab.