Guten Morgen,

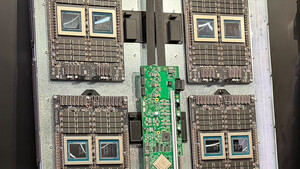

kann mir jemand die Gründe nennen warum z.B. der 8700K nur eine Die-Größe von nur 149mm² hat obwohl noch etwa ein Drittel für die IGP drauf geht? https://en.wikichip.org/wiki/intel/core_i7/i7-8700k

Während ein Skylake-X 10-Kerner schon mehr als doppelt so groß ist ohne IPG.

https://www.anandtech.com/show/1155...-core-i9-7900x-i7-7820x-and-i7-7800x-tested/6

Was genau sorgt bei Skylake-X dafür dass die Die-Fläche so viel größer ist?

Liegt das an den zusätzlichen Features der "HEDT" Plattform? und wenn ja warum ist dass dann bei AMD nicht der Fall?

kann mir jemand die Gründe nennen warum z.B. der 8700K nur eine Die-Größe von nur 149mm² hat obwohl noch etwa ein Drittel für die IGP drauf geht? https://en.wikichip.org/wiki/intel/core_i7/i7-8700k

Während ein Skylake-X 10-Kerner schon mehr als doppelt so groß ist ohne IPG.

https://www.anandtech.com/show/1155...-core-i9-7900x-i7-7820x-and-i7-7800x-tested/6

Was genau sorgt bei Skylake-X dafür dass die Die-Fläche so viel größer ist?

Liegt das an den zusätzlichen Features der "HEDT" Plattform? und wenn ja warum ist dass dann bei AMD nicht der Fall?