IDF: Intel zeigt 65nm Wafer und plant Dual Core Xeon und Itanium

Der President und COO der Intel Corporation, Paul Otellini, hat am Dienstag das Intel Developer Forum (IDF) im Kalifornischen San Jose eröffnet. Während seiner Rede betonte Otellini, dass die Konvergenz von Computer und Kommunikation nun zu einem Trend auch im Massenmarkt geworden sei.

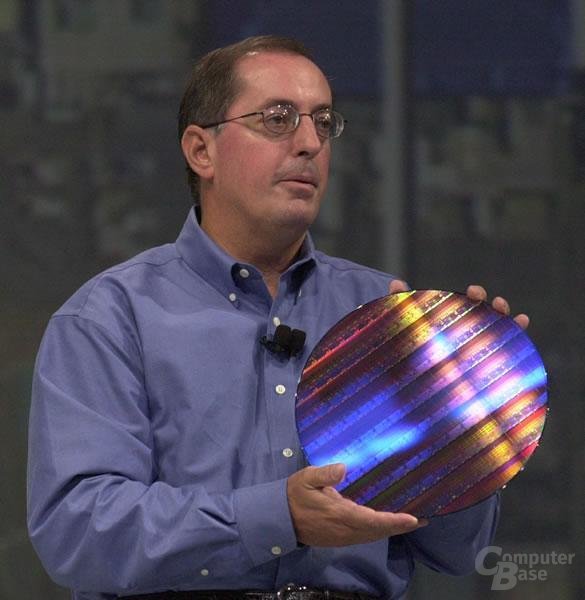

Außerdem zeigte er den ersten Silizium-Wafer mit der zukünftigen 65-Nanometer-Technologie, die neue Sicherheitstechnologie LaGrande sowie die Vanderpool Technologie, die mehrere unabhängige Softwareumgebungen in einem einzelnen PC möglich macht.

Der Ausbau der weltweiten Computer Infrastruktur mit täglich 76.000 drahtlosen Netzwerkkarten, so Otellini in seiner Rede, sei eines der Beispiele, die zeigen, dass sich die Konvergenz - Intel Bezeichnung für das zunehmende Verschmelzen aller Multimedia-Geräte - durchgesetzt habe. Ebenso die hohe Akzeptanz der Intel Centrino Mobiltechnologie zwei Jahre nach der Bekanntgabe erster Details unter dem Codenamen Banias. "Wir schätzen, dass es im Jahr 2010 mehr als 2,5 Milliarden drahtlose Handheldgeräte geben wird, in denen Kommunikationsfunktionen mit der Rechenleistung der heute fortschrittlichsten PCs vereint sind," sagt Otellini.

Die LaGrande Technologie ist eine zukünftige Erweiterung der Intel Prozessoren, Chipsätze und Plattformen, die in Kombination mit optimierter Software vor softwarebasierten Attacken auf Computersysteme schützt. Die Technologie soll in den nächsten zwei bis drei Jahren verfügbar sein. Allerdings sollen die Grundlagen dafür bereits mit dem im vierten Quartal 2003 erscheinenden Prescott-Prozessor gelegt werden.

"In einer Zeit, in der wir vom 'Virus der Woche' geplagt werden, muss es für die Industrie oberste Priorität sein, Computer durch zusätzliche Sicherheitsmechanismen auf Hardware-Basis sicherer zu machen", sagte Otellini. "Es ist jedoch wichtig einen Weg zu finden, der auch die Privatsphäre des Einzelnen respektiert."

Die Technologie mit dem Codenamen "Vanderpool" soll mehrere unabhängige Softwareumgebungen in einem einzelnen PC möglich machen - auf eine ähnliche Weise arbeiten Mainframes. Zuverlässigkeit, Flexibilität und Reaktionszeiten werden dadurch verbessert. Außerdem sollen sich Computer nach einem Crash schneller erholen können.

Im Bereich der Siliziumtechnologie packt Intel mehr Funktionen in immer kleinere Bauteile: Ab 2011 verfügen Halbleiter über Schaltkreise mit 22-Nanometern und Transistoren, die kleiner sind als ein einzelnes DNA Molekül. Otellini präsentierte zum ersten Mal öffentlich einen Intel Silizium-Wafer, der unter Verwendung des 65-nm-Herstellungsprozesses der nächsten Generation gefertigt wurde.

Im Enterprise-Bereich wird die Konvergenz neue Möglichkeiten eröffnen, wenn Anwender Datenbanken und andere Applikationen über drahtlose Verbindungen im Internet anzapfen können. Zu den Produkt-Highlights von Intel im Enterprise Computing Bereich gehören beispielsweise Pläne zur Einführung eines Dual Core Intel Xeon Prozessors MP (mit Codenamen Tulsa) und eines Multi-Core Intel Itanium Prozessors (mit Codenamen Tanglewood).

Im digitalen Heim wird die Entwicklung von Industriespezifikationen zunehmend wichtig für die gemeinsame Nutzung von Inhalten auf mehreren Geräten. Ein anderes Beispiel der Zusammenarbeit in der Industrie ist die Entwicklung des Digital Transmission Content Protection mittels Internet Protocol (DTCP/IP) Technologie. Damit können Heimanwender drahtlos geschützte Inhalte aus dem Unterhaltungssektor über eine Vielzahl unterschiedlicher Geräte zu Hause nutzen. Durch die Zusammenarbeit mit Content Providern wie Warner Brothers wird diese Technologie wahrscheinlich zu einem Eckpfeiler für die Ausweitung der Unterhaltung im digitalen Heim - zumindest wenn es nach Intel geht.