AMD plaudert über „Barcelona“

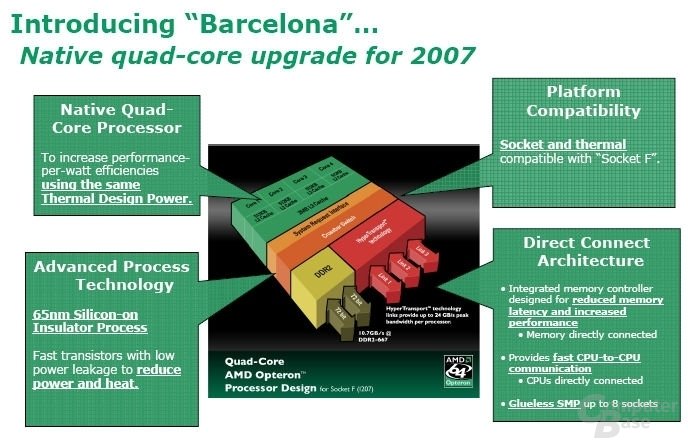

Auf dem MPF (Fall Microprocessor Forum) in San Jose, Kalifornien, hat Ben Sander, einer der „Architekten“ von AMDs neuer Quad-Core-Technik, viele Einzelheiten zum nächstes Jahr erscheinenden neuen Prozessor bekannt gegeben.

Da Intel zur Zeit die Performance-Krone mit dem Core 2 Duo inne hat, kann AMD sich nicht ausruhen und so hat Ben Sander die Öffentlichkeit genauer in AMDs Pläne eingeweiht. Viele bisherige Informationen waren mehr Gerüchte als bestätigte Tatsachen. Allerdings bewahrheitet sich auch das ein oder andere.

Fließkomma wird schneller

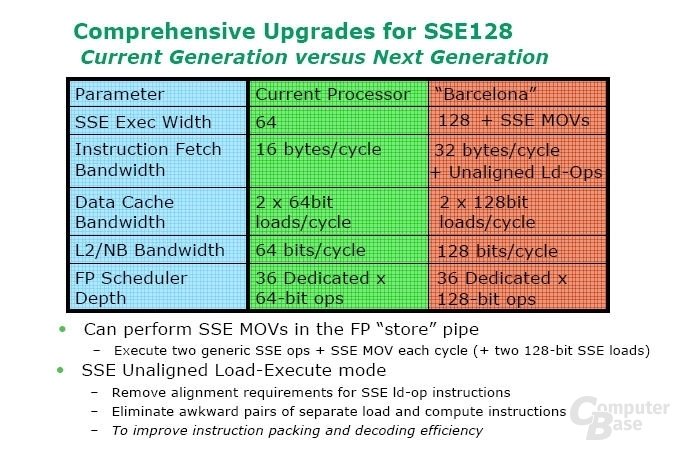

Neben den absoluten High-End-Systemen auch für wissenschaftliche Zwecke soll die Quad-Core-Technik auch für das En- und Decodieren von HD-Inhalten verwendet werden können. Beide Anwendungsbereiche sind dabei sehr belastend für die Fließkomma-Einheit des Prozessors. Gegenüber den bisherigen AMD-Prozessoren sind auch Erweiterungen der SSE-Verarbeitung vorgesehen.

In allen wichtigen Bereichen der Fließkomma-Operationen verdoppelt AMD also die bisherigen Werte. Auch wenn das vermutlich nicht mit der doppelten Leistung gleichzusetzen ist, wird sich doch eine deutliche Performance-Steigerung im FP-Bereich zeigen.

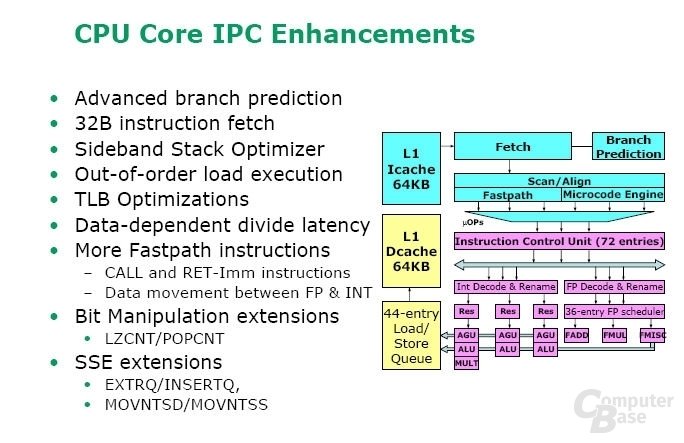

Mehr Instruktionen pro Takt

Da sich das alte Konzept mit hoher Leistung bei niedrigem Takt gut bewährt hat, arbeitet AMD auch in dieser Richtung weiter. Um den Barcelona in diesem Bereich zu beschleunigen, wird die Sprung-Vorhersage verbessert. Dazu werden unter anderem mehr bisherige Sprünge gespeichert (Branch History), eine indirekte Sprungvorhersage mit 512 Einträgen und ein doppelt so großer Return-Stack vorgehalten. Auch sollen einige Load-Instruktionen anderen bevorzugt werden können, somit eine nicht-lineare Abarbeitung erlauben. Damit sollen die Latenz-Effekte des L2-Cache reduziert werden. Der TLB (Translation Lookaside Buffer) wird dann über 1 GB große Seiten verfügen die mit 48 Bit Breite angesprochen werden. Barcelona kann damit bis zu 256 TeraByte addressieren. Dabei soll der Memory-Controller auch DDR3 und FBDIMM ansprechen können. Laut Sander wird der Quad-Core-AMD aber mit DDR2-RAM starten.

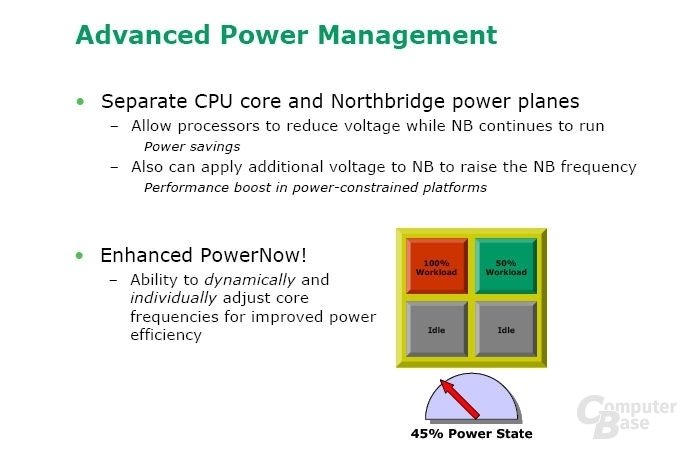

Stromsparen

Für weitere Möglichkeiten zum Energie sparen will AMD mit einer Trennung der Versorgung von Northbridge und Prozessor sorgen. Das betrifft auch die Taktung der beiden Komponenten. So kann also in Zukunft wie bei herkömmlichen Zwei-Chip-Lösungen jede Komponente einzeln angesprochen werden, was Takt und Spannung angeht. Zusätzlich lassen sich alle vier Kerne des Barcelona einzeln ansprechen, was den Prozessortakt betrifft. Reicht zum Beispiel für die Wiedergabe von HD-Inhalten ein Kern, so können alle anderen Kerne es deutlicher ruhiger angehen lassen, was sich positiv auf Wärmeentwicklung und Energieverbrauch auswirken sollte.

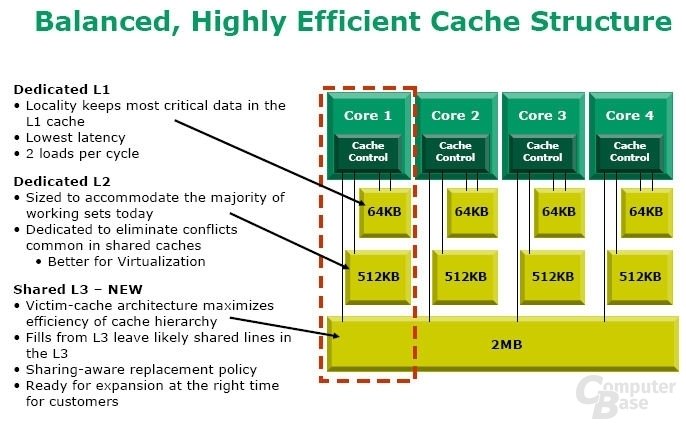

Cache

Neu wird bei AMD der L3-Cache sein, den sich alle Prozessor-Kerne teilen. Jeder Kern hat einen je 128 KB großen L1-Cache für Daten und Instruktionen. Dazu kommt ein L2-Cache mit 512 KB, der jeweils jedem Kern zur Verfügung steht. Besondere Techniken sollen dafür sorgen, das es zu weniger Konflikten und schnelleren Zugriffen kommt. Das sei vor allem auch bei Virtualisierungen von Vorteil, so AMD. Die Größe des L3-Cache ist nicht in Beton gemauert und kann je nach Bedarf des Marktes vergrößert werden.

Bestätigt hat Ben Sander die 65-nm-Technologie, in der die Barcelona-CPUs gefertigt werden sollen. Auch soll der TDP bei unter 100 Watt liegen, für ein Dual-Sockel-System ohne Grafikkarte und externe Komponenten werden etwa 240 Watt erwartet. Was aus all diesen Ankündigungen tatsächlich kommen wird, zeigt uns erst das Jahr 2007, wenn im zweiten oder dritten Quartal die neuen CPUs auf Basis des Barcelona den Markt kommen werden.