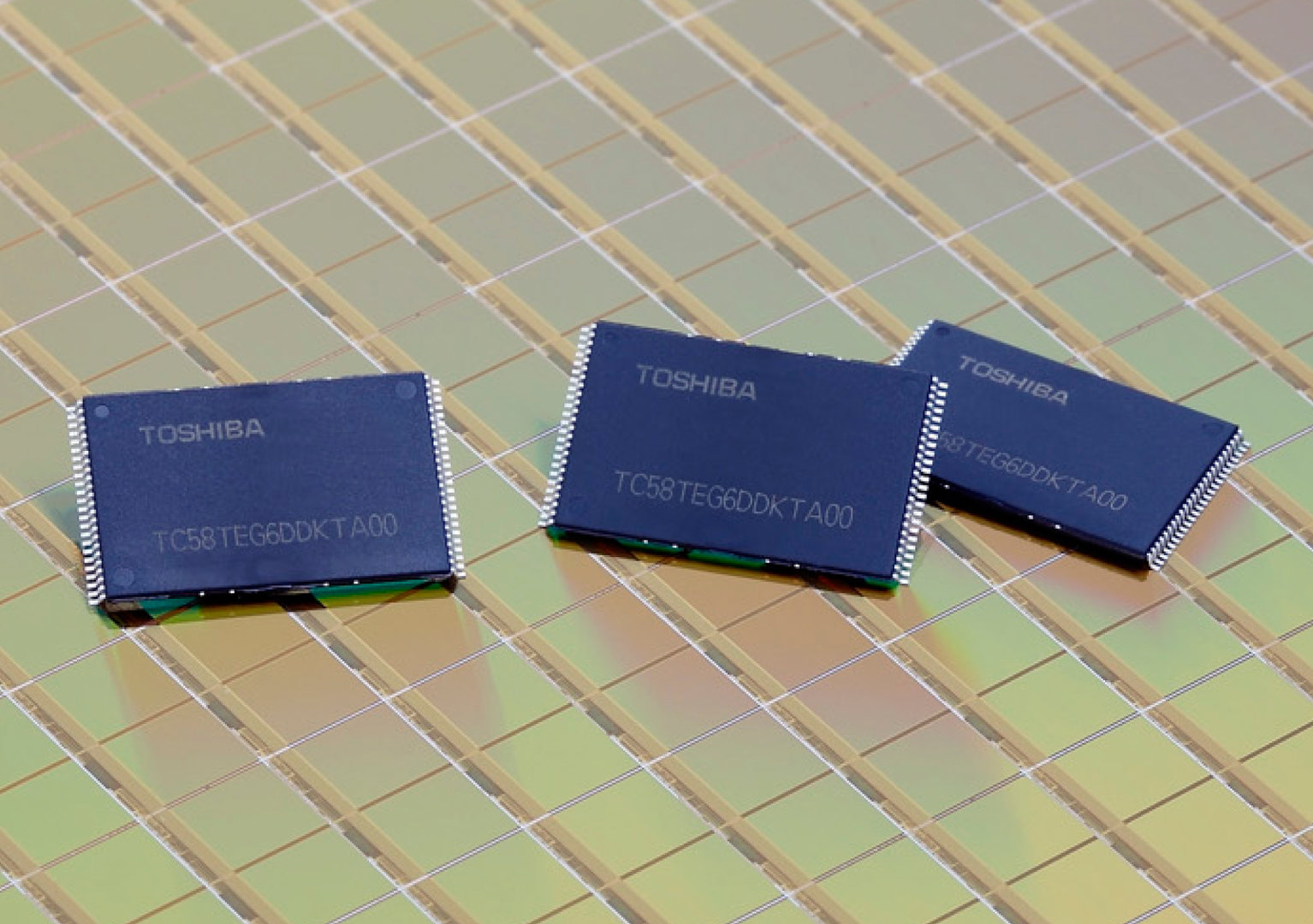

Toshiba verkleinert und beschleunigt 19-nm-MLC-NAND-Flash

Mit dem Ziel, den „kleinsten 64-Gigabit NAND-Speicher-Chip der Welt“ anbieten zu können, kündigt Toshiba den Beginn der Massenproduktion der zweiten NAND-Flash-Generation mit einer Strukturbreite von 19 Nanometern an. Erste MLC-Chips (2 Bit pro Zelle) sollen noch diesen Monat in hoher Stückzahl gefertigt werden.

Die Fläche der 64-Gigabit-NAND-Flash-Chips soll dank der optimierten Herstellungstechnik lediglich 94 Quadratmillimeter betragen. Zusätzlich soll die Schreibgeschwindigkeit pro Chip auf bis zu 25 Megabyte pro Sekunde anwachsen, was nach Angaben des Herstellers ebenfalls zum Spitzenfeld im Bereich der MLC-Chips mit 2 Bit pro Zelle gehört. TLC-NAND-Flash-Chips mit 3 Bit pro Zelle, die entsprechend mehr Daten pro Chip speichern können, befänden sich noch in Entwicklung und sollen, sofern alles reibungslos verläuft, in der zweiten Hälfte von Toshibas aktuellem Fiskaljahr, das am 31. März 2014 endet, in Massenproduktion gehen.

Bei der Fertigung von TLC-Speicherchips mit hoher Kapazität ist Samsung allerdings Toshiba bereits ein gutes Stück voraus: Im vergangenen Monat verkündeten die Südkoreaner den Beginn der Massenfertigung von 128-Gbit-TLC-NAND-Flash mit einer Strukturbreite von unter 20 Nanometern und rühmten sich mit der „höchsten Speicherdichte der Branche“.

In Bereichen wo es nicht auf eine möglichst hohe Lebensdauer der Speicherzellen ankommt – TLC-Speicher (3 Bit) verkraftet weniger Schreibzyklen als MLC- (2 Bit) und erheblich weniger Schreibzyklen als SLC-Speicher (1 Bit) – gehört TLC-Speicher die Zukunft, da dieser die höchste Speicherdichte im Verhältnis zur Chipfläche bietet und somit bei gleicher Kapazität günstiger herzustellen ist.