AMD Zen: Erster Benchmark gegen Intel und Details zur Architektur

Es ist das Highlight des IDF 2016 und es kommt von AMD: Auf dem traditionellen Gegen-Event hat CEO Lisa Su einige technische Details zur Zen-Architektur verraten. Diese gingen soweit ins Detail wie noch nie zuvor und handelten von einem neuen Micro-Op-Cache über Cache-Größen bis zu einem ersten Benchmark von Zen.

Selten zuvor waren AMD-CEO Lisa Su und ihre rechte Hand, der CTO Mark Papermaster, besser gelaunt und lockerer als am gestrigen Abend. Denn das, was AMD im Gepäck hatte, konnte überzeugen – und das wussten alle Beteiligten des Herstellers.

Zen-CPU mit 3,0 GHz

Die ersten Zen-Samples sind seit einigen Wochen aus der Fertigung zurück und erreichen bei Leistung und Energiebedarf die von AMD gesetzten Ziele. Deshalb hatte AMD nicht nur die ersten offiziellen Details zur Architektur im Gepäck, sondern auch einen Benchmark des 3,0 GHz schnellen Zen-Samples mit acht Kernen und 16 Threads sowie ein erstes Spiel in 4K.

Dabei kamen Sockel-AM4-Systeme zum Einsatz. Der Blick auf die I/O-Blende verriet, dass die Mainboards dank Videoausgängen auch mit Bristol Ridge umgehen können. Verbaut waren zudem je zwei DDR4-Speicherriegel. Ein Dual-Channel-Interface ist damit quasi bestätigt, wenngleich AMD gestern keine Aussagen zum Speicher machte.

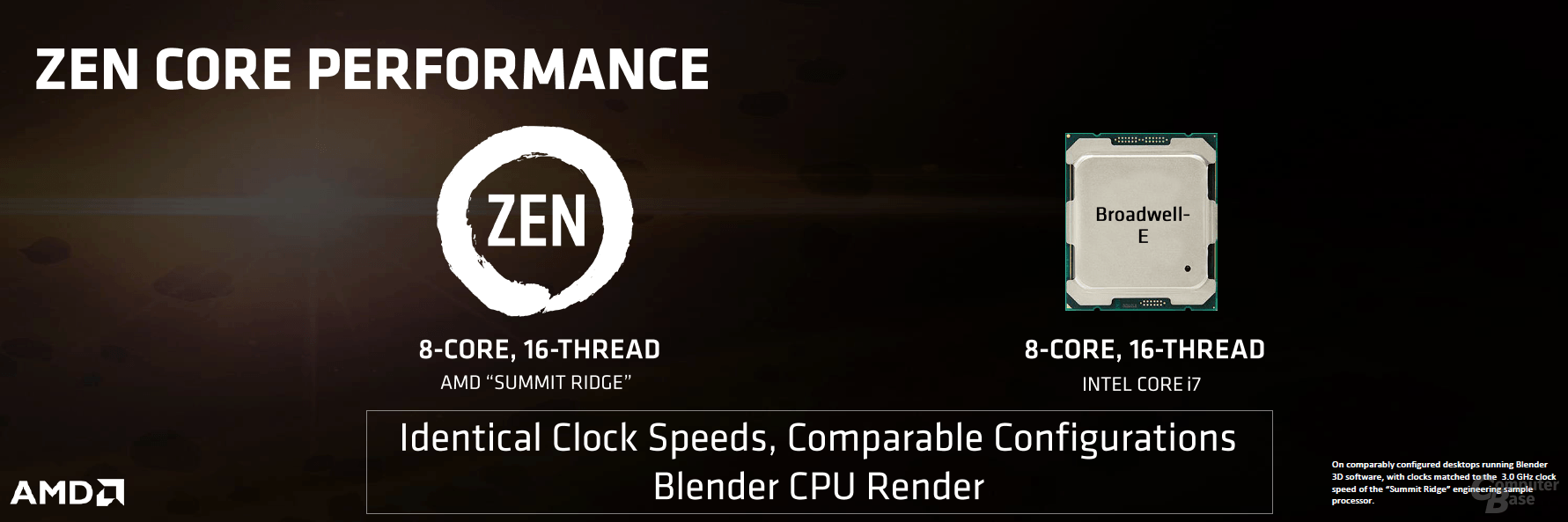

AMD Zen auf Augenhöhe mit Intels Broadwell-E

Gewählt wurde für den Benchmark-Vergleich ein Broadwell-E-Prozessor von Intel mit acht Kernen und 16 Threads, also ein Core i7-6900K. Allerdings wurde dieser auf 3,0 GHz herunter getaktet, Turbo & Co. waren zudem deaktiviert. Im Blender-Benchmark, der eine hohe Floating-Point-Leistung verlangt, war das Endergebnis ein Quasi-Gleichstand mit Zen, sogar mit minimalem Vorteil für den neuen AMD-Prozessor. Die Gerüchte vorab, dass Zen ungefähr auf dem Niveau der IPC von Broadwell liege, wurden damit untermauert. Doch das Wichtigste kam gleich hinterher: Die finalen Modelle von Zen werden bei ähnlicher TDP höher takten. Der 1.089 US-Dollar teure Core i7-6900K könnte also auch im realen Alltag geschlagen werden.

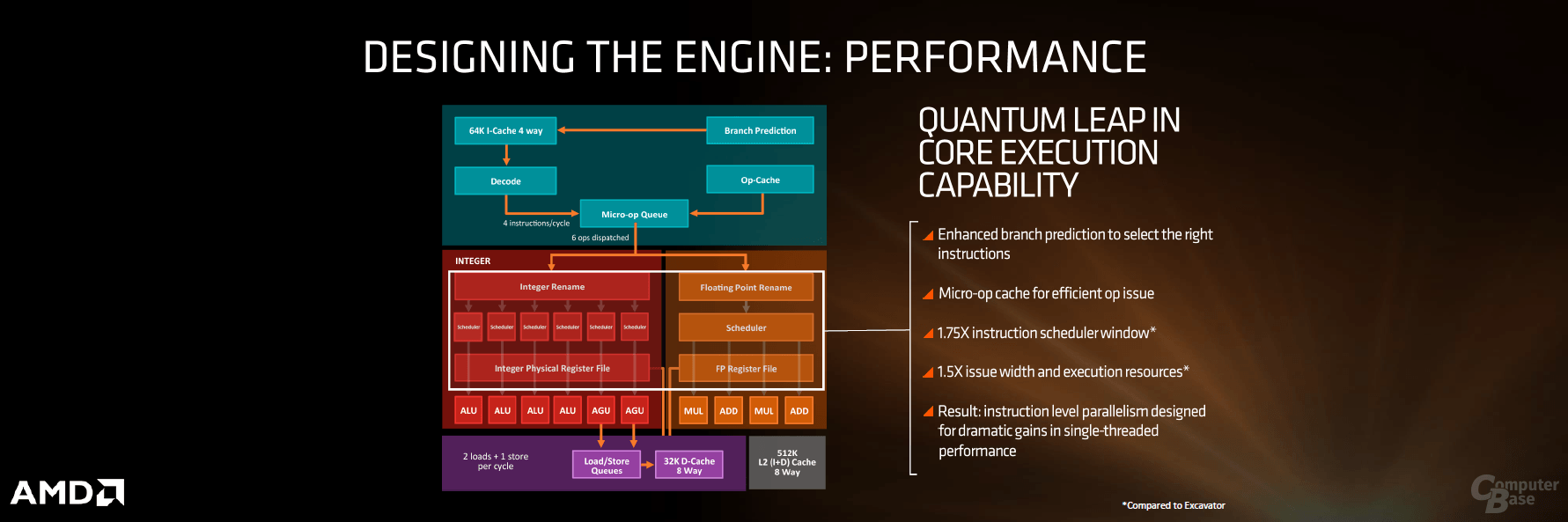

Zen jetzt auch mit Micro-Op-Cache

Mark Papermaster als CTO holte zu einem kleinen technischen Überblick aus. Auch wenn er nicht sehr tief ins Detail ging, wurden einige Fragen geklärt. Von Intel bereits seit Sandy Bridge bekannt, holt auch AMD einen Micro-Op-Cache mit ins Boot. Wie genau sich dieser verhält, ist noch unklar. Bei Intel ist der Micro-Op-Cache Teil des L1-Instruction-Caches – da dieser bei Zen beachtliche 64 KByte groß ist, spricht auch bei AMD einiges für solch einen Einsatz. Mit vierfacher Assoziativität ist der Cache zudem vermutlich sehr flott unterwegs, der parallel verfügbare 32 KByte große L1-Daten-Cache besitzt dagegen „nur“ eine achtfache Assoziativität.

Ergänzt werden diese Caches im Rechenkern mit 512 KByte L2-Cache bei ebenfalls achtfacher Assoziativität. Gegenüber dem bisherigen Moduldesign und der größten Schwäche beim Cache-Verhalten soll die Bandbreite bei der Zen-Architektur je nach Einsatzgebiet nahezu den Faktor 5x erreichen können – dazu zählt am Ende auch noch der 16 MByte große L3-Cache, der jedoch als Shared Cache zum Einsatz kommt. Das Besondere: Der L3-Cache soll auch bei APUs mit dem Codename Raven Ridge vorhanden sein, bisher wurde dieser dort immer entfernt.

Balanced Design aus Leistung und Effizienz

In vielen anderen Bereichen des Designs verwies AMD auf die kommende Woche und erklärte grob, dass die typischen Baustellen eines CPU-Designs wie die Sprungvorhersage, die Ausführungseinheiten und andere Bereiche ebenfalls massiv verbessert respektive erweitert wurden. Dabei betonte AMD mehrfach, dass es sich immer noch um ein „balanced design“ handele, das in 14 nm FinFET gefertigt auf Leistung sowie Effizienz optimiert sei. Zu dem Thema wird es auf der Fachmesse Hot Chips 28 noch eine weitere Präsentation geben, die sich intensiver der Architektur widmen wird; ComputerBase ist vor Ort. Dann dürften auch nahezu die letzten Fragen geklärt werden, wenngleich AMD auch dort noch nicht alles verraten will. Im Q&A in kleiner Runde erklärten Papermaster und Su beispielsweise zum Thema AVX-512, dass dieses nicht dabei ist. Zen wird erst einmal nur AVX-128 (und bei Zusammenarbeit AVX256) bieten. Doch gleichzeitig kam ein Wink mit dem Zaunpfahl, denn auf der neuen Roadmap ist bereits Zen+ vermerkt.

AMD hält an Ende 2016 fest

Natürlich wurden auch Fragen nach den finalen Taktraten und Preisen gestellt – auf die gab es erwartungsgemäß keine Antwort. AMD ließ sich jedoch zu zwei Tendenzen hinreißen: Final wird Zen schneller sein als jetzt gezeigt, und den Preis kommentierte Lisa Su mit einem Lächeln sowie dem Zusatz, dass der „ASP höher sein wird als bei aktuellen CPUs“. Dies war auch ein Wink an die Analysten im Raum und damit auch die Aktionäre, dass nach einer langen Durststrecke höheren Preisen dank konkurrenzfähigen Produkten nicht mehr viel im Weg stehe.

Doch bis die Produkte da sind, werden noch einige Monate vergehen. Zum gezeigten oder finalen Stepping und eventuellen Problemen gab es natürlich ebenfalls keine Antworten. Su betonte aber, dass einige Dinge aktuell noch angepackt werden. Der Marktstart ist nach wie vor für das erste Geschäftsquartal 2017 vorgesehen, und wenn alles funktioniert, könnten Ende 2016 die ersten Systeme verfügbar sein – mit OEMs sind bereits jetzt Systeme in der Mache und Mainboardhersteller erhalten erste Samples. Genau dies erklärt AMD aber auch bereits seit einigen Monaten.