Chipfertigung: Fortschritte und Innovationen in der Fertigung II

3/3FinFET: Transistoren mit Finnenstruktur

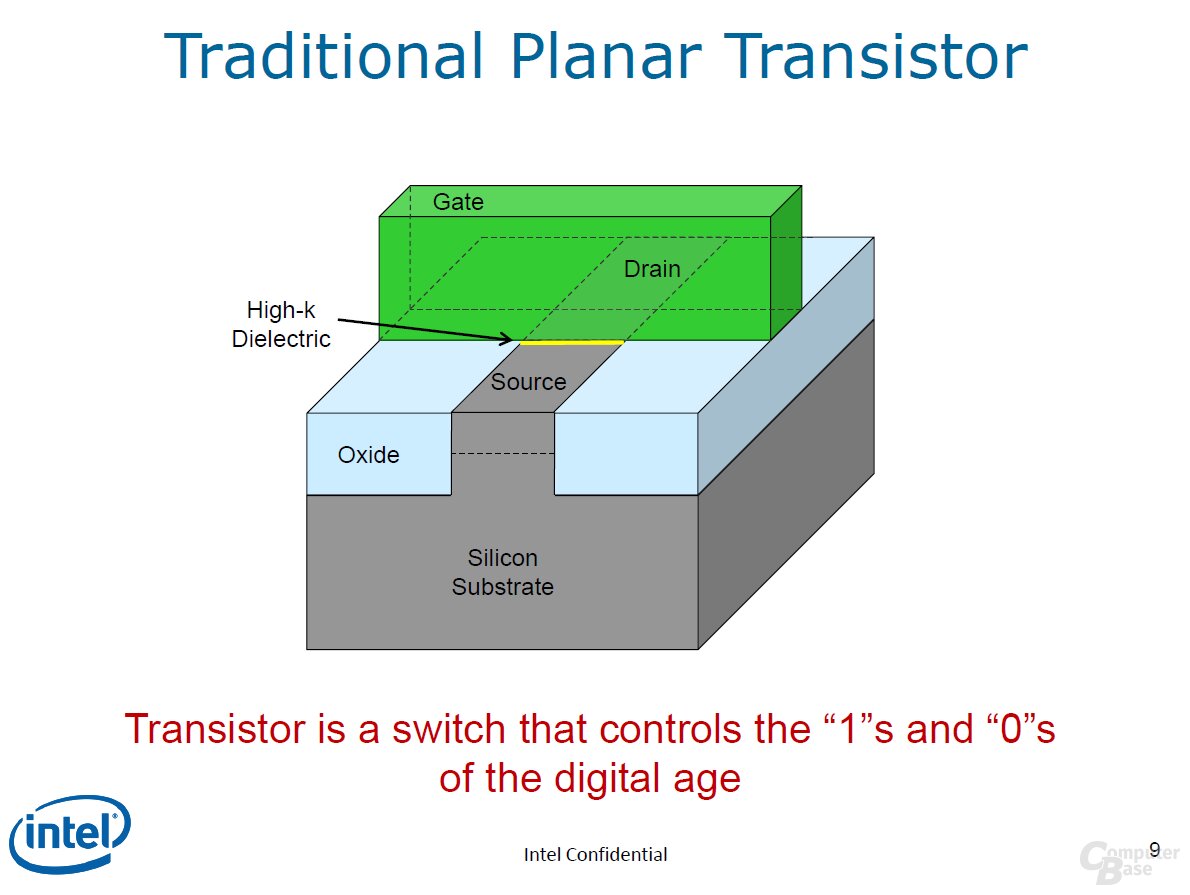

Bis zum Jahr 2012 waren FETs flach, wie in der Schematik anfangs dargestellt. Die dünne, leitfähige Schicht, die sich im eingeschalteten Zustand unter dem Gate bildet und ihn leitend macht, hat zwar mit kleiner werdenden Strukturen einen immer geringeren Widerstand. Das Gleiche gilt aber auch für den Widerstand im ausgeschalteten Zustand, wenn idealerweise kein Strom fließen sollte.

Kleinere Strukturen bedeuteten dadurch immer höhere Leckströme. Gleichzeitig entsteht der sogenannte Short-Channel-Effekt, eine Sammlung mehrerer physikalischer Effekte, die die unerwünschte Leitfähigkeit des Kanals zwischen Source und Drain weiter erhöhen.

Diesem Umstand konnte man nur durch eine Änderung der Transistorgeometrie Herr werden, weswegen im Jahr 1991 erstmals eine Finnenstruktur vorgeschlagen wurde. Intel, der erste Fertiger, der die Finnenstruktur realisierte, nannte die Technologie Tri-Gate, der Markenname hat sich aber nicht durchgesetzt. Stattdessen ist die Technologie heutzutage unter dem Namen FinFET bekannt. Im Jahr 2012 wurden FinFETs erstmalig im 22-nm-Prozess der CPUs mit dem Codenamen Ivy Bridge für ein Massenprodukt verwendet.

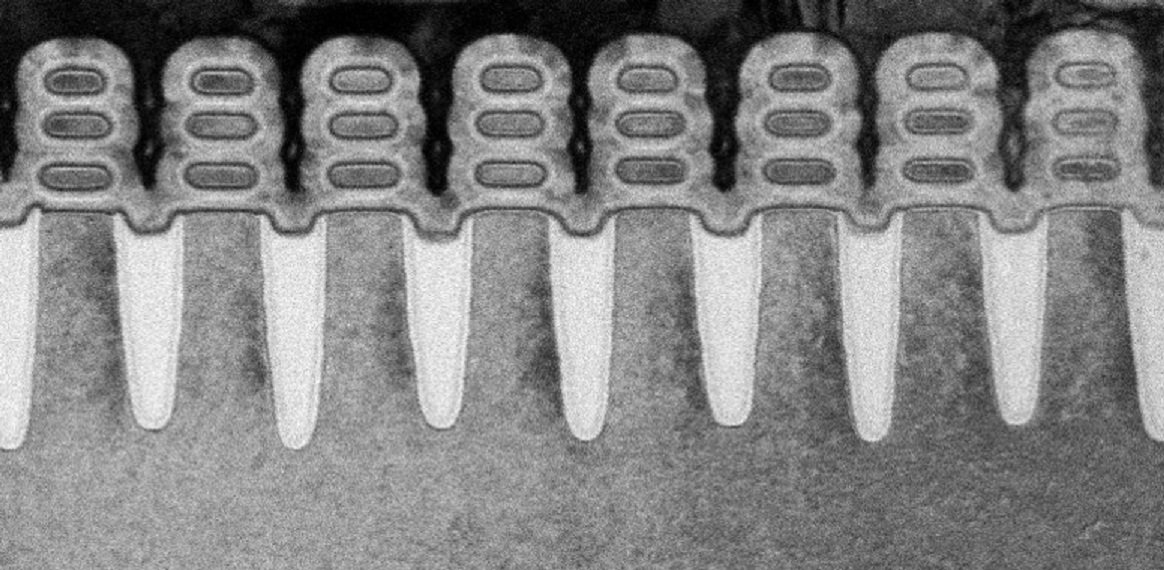

Beim FinFET ragt der Kanal unter dem Gate dreidimensional in Form einer Finne hervor. Das Oxid und der Gate-Kontakt umschließen die Finne, so dass sich bei anliegender Spannung anstatt einer gleich drei leitfähige Schichten ausbilden: eine oben und zwei an den Seiten. Das ermöglicht eine deutlich erhöhte Leitfähigkeit des Transistors im eingeschalteten Zustand. Dadurch kann die Gate-Spannung reduziert werden, was die problematischen Leckströme reduziert. Insgesamt ergibt sich aus der neuen Transistorgeometrie eine deutliche Steigerung der Schaltgeschwindigkeit bei gleicher Transistorgröße – bzw. bei gleicher Schaltgeschwindigkeit ein verringerter Flächenbedarf. Ermöglicht wurde diese 3D-Struktur durch die vorherige Einführung von ALD (siehe oben), ohne die eine mehrseitige Beschichtung der Finne nicht realisierbar ist.

Die restlichen Halbleiterhersteller zogen Jahre später nach und führten FinFET in den 14/16-nm-Prozessen ein. TSMC mit seinem 16-nm-Prozess lieferte Produkte Ende 2015, ebenso wie Samsung, der seinen 14-nm-Prozess an Globalfoundries lizenzierte.

Multipatterning: x Belichtungsschritte pro Schicht

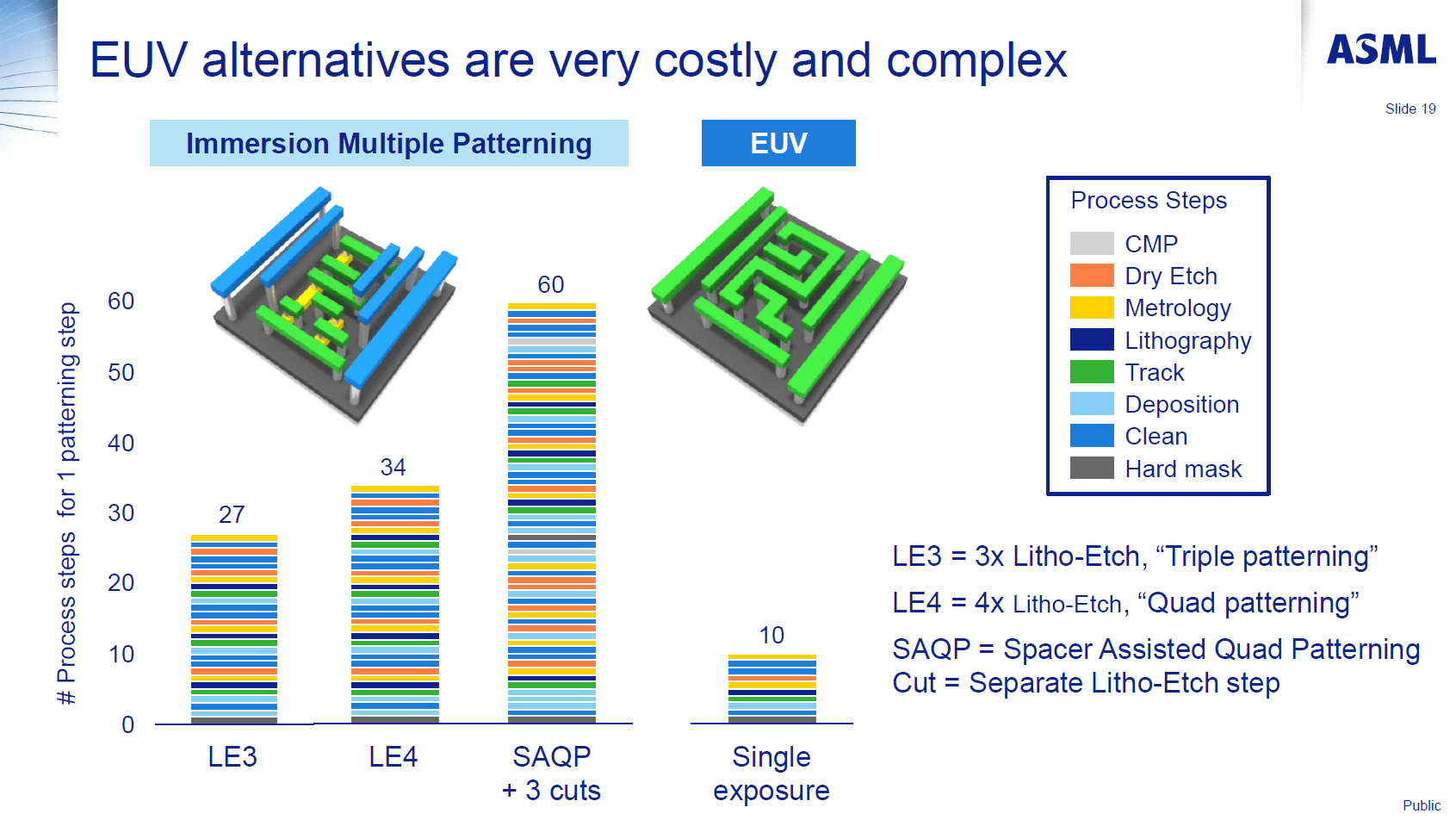

Im Wettlauf um immer kleinere Strukturgrößen wurde traditionell stets die Belichtungsquelle geändert, so dass mit kleineren Wellenlängen belichtet werden konnte. Kürzlich erst wurde mit der EUV-Belichtung (Exkurs: Chipfertigung: Was steckt hinter der EUV-Lithografie?) der erste große Schritt seit über zehn Jahren eingeleitet. Während dieser zehn Jahre musste die Fertigung allerdings weiter verkleinert werden können. Um immer mehr Transistoren auf die gleiche Fläche packen zu können, wurde Multipatterning eingeführt, bei der mehr als ein Belichtungsschritt pro Schicht verwendet wird. Durch geschicktes Ausnutzen der chemischen Eigenschaften der Materialien und Entwickler können Strukturen erstellt werden, die kleiner als die minimale Linienbreite des Belichtungssystems sind.

Ein Beispiel dafür ist die „Doppelbelichtung mit Doppelätzung“, bei der vergleichbar große Strukturen näher beieinander gefertigt werden, indem die Maske der zweiten Belichtung leicht verschoben ist. Mit zwei Belichtungsschritten erzeugt man so neue Strukturen, die im letzten Schritt die Maske für die Zielschicht darstellen. Dadurch kann man die Auflösung effektiv verdoppeln.

Eine weitere Methode ist die „selbstausrichtende Doppelstrukturierung“, bei der nur eine Maske benötigt wird, um regelmäßige Strukturen mit doppelter Auflösung zu erzeugen. Durch ein Abscheidungsverfahren, das die zuerst belichtete Hilfsstruktur sowohl von oben als auch von den Seiten beschichtet, kann die Beschichtung im Anschluss so heruntergeätzt werden, dass dort Material verbleibt, wo die Hilfsstruktur ihre Kanten hatte. Die so erzeugte Schicht hat doppelt so viele Strukturen wie die ursprünglich genutzte Maske und kann im Anschluss auf die Zielschicht übertragen werden.

Mit fortschreitender Fertigung wurden verschiedene weitere Methoden verwendet, die bei der 7-nm-Fertigung von TSMC die Nutzung von „selbstausrichtender Vierfachstrukturierung“ für einige Teile wie die Finne vorsahen. Intel bewarb seinerzeit die exzessive Nutzung von Quad-Patterning, was allerdings einen Beitrag zu der langen Verzögerung von Intels Fertigungsfortschritten leistete. Durch Mehrfachstrukturierung werden immer mehr Schritte benötigt, um eine neue Schicht auf dem Wafer zu erzeugen, was die Erstellung von Wafern in niedrigeren Fertigungsgrößen immer komplizierter und teurer macht.

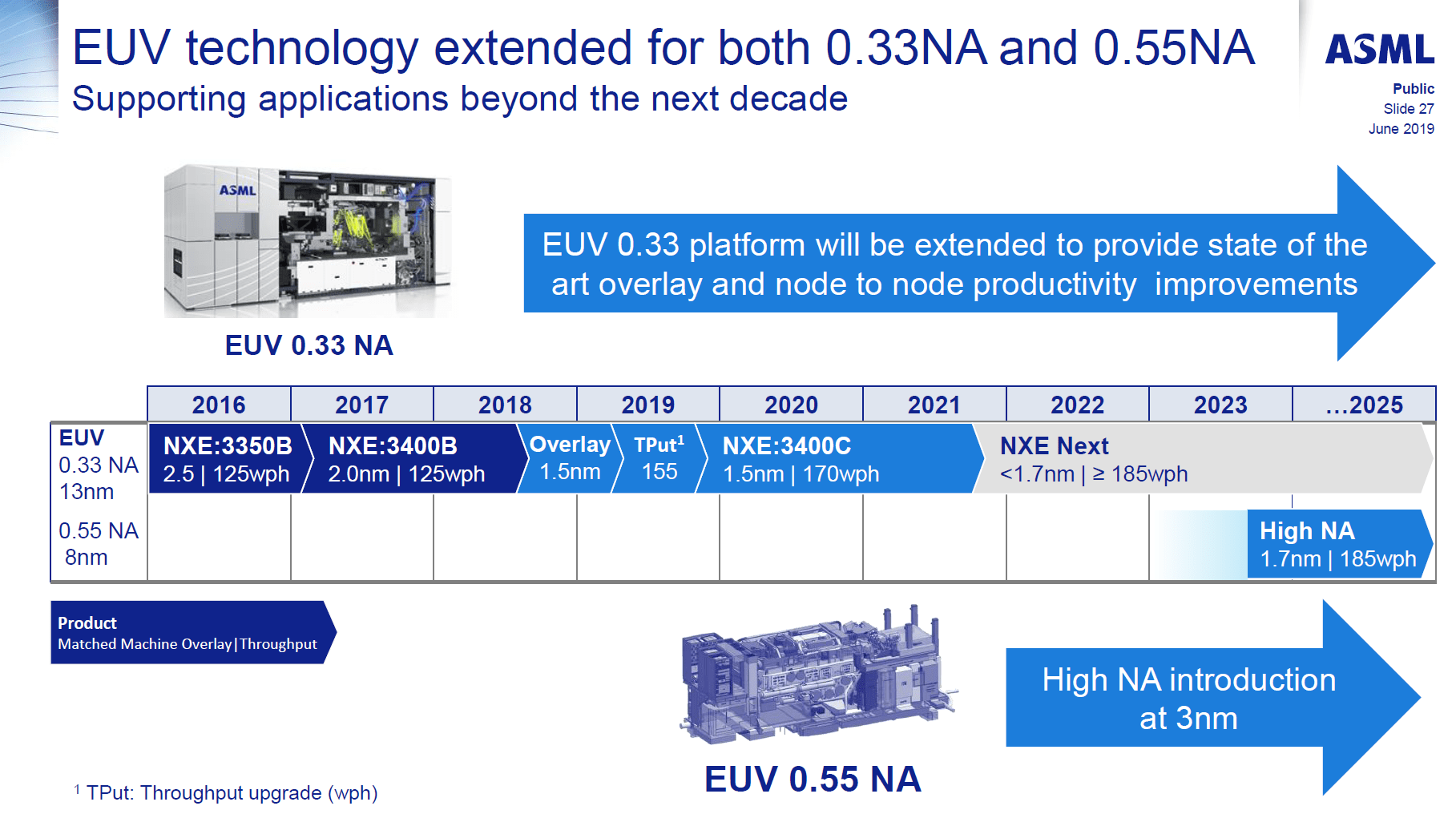

Der Wechsel auf EUV-Lithografie

Das Einsetzen von EUV als neue Belichtungsquelle sorgte schlussendlich für den Durchbruch, da viele Belichtungsschritte wieder entfallen können. EUV alleine ermöglicht bereits eine sehr kleine Fertigungsgröße von 7 nm und kleiner. In Zukunft wird allerdings, um z. B. den nächsten Schritt zu 5 nm zu schaffen, wieder Mehrfachstrukturierung angewandt. Eine besonders detaillierte Auflistung der verschiedenen Verfahren findet sich auf der englischen Wikipedia-Seite zu Multipatterning.

Gate-All-Around: Auf dem Weg zu 3 nm

Mit weiter schrumpfenden Strukturen seit der Einführung des FinFETs wurde der Short-Channel-Effekt für die Leistung des Transistors erneut relevant. Die Finnenstruktur sorgt zwar für stabile Verhältnisse im Kanal in Fertigungsgrößen bis hinunter zu 5 nm, ab ca. 3 nm muss jedoch eine neue FET-Technologie her. Die weitere Verbesserung der Transistorleistung ergibt sich, wenn man die letzte verbliebene Seite, die Unterseite des Kanals, ebenfalls mit Oxid und Gate-Kontakt umschließt. Dadurch entsteht ein Gate-All-Around-FET oder GAAFET. IBM hat dieses Verfahren erstmals 2017 veröffentlicht.

Im Fall von GAA kommt das erste Design aus dem Jahr 1988, also noch vor dem des FinFET, allerdings haben lange die unüberwindbaren Hürden in der Fertigung einen Einsatz von GAA verhindert. Der Vorteil von GAA ist die Verwendung mehrerer, vollständig vom Gate umschlossener Channels, die den Kontrast zwischen hohem Widerstand im ausgeschalteten und niedrigem Widerstand im eingeschalteten Zustand deutlich erhöhen. Dadurch kann der Transistor auch bei weiter schrumpfenden Abmessungen schnell und sauber schalten. Samsung will GAA im kommenden 3-nm-Prozess einsetzen, TSMC und Intel erst später beim 2-nm-Prozess. Allerdings musste Samsung kürzlich eingestehen, dass sein erster GAA-Prozess namens 3GAE nicht für die Massenfertigung geeignet ist und der Einsatz von GAA sich deswegen verzögern wird. Wer am Ende das Rennen um den „perfekten Transistor“ macht, ist noch offen.

Wohin geht die Reise?

Der Bedarf nach immer höheren Transistordichten und immer komplexeren Schaltungen zwingt die Halbleiterfertiger dazu, immer kleinere Strukturen herzustellen. Dabei werden wie in den Jahren zuvor immer mehr Techniken eingesetzt, die so gezielt ineinandergreifen, dass sie neue Technologiesprünge ermöglichen. Zunächst wird der Hersteller der Belichtungsmaschinen, ASML, neue Modelle mit einer erhöhten numerischen Apertur bereitstellen. Ursprüngliche Roadmaps sahen dies für 2023 und den 3-nm-Prozess vor, mittlerweile spricht das Unternehmen in seinem Jahresbericht von 2025 und 2 nm. Intel will Erstkunde eines solchen Systems im Jahr 2025 sein. In der Zwischenzeit wird weiterhin auf Multipatterning zurückgegriffen werden.

Außerdem wird GAA in die Transistorfertigung Einzug halten und konsequent weiterentwickelt werden. Samsung hat bereits Nanosheets als Nachfolger der GAA-Nanowires in Aussicht gestellt und Intel spricht von RibbonFET. Am Horizont stehen außerdem neue Materialien wie Germanium oder III-V-Halbleiter.

Wie diese technologischen Fortschritte und Innovationen dabei helfen, immer kleinere Transistoren mit geringerer Verlustleistung trotzdem eindeutig schalten zu lassen, hat dieser Artikel hoffentlich geklärt.

Weitere Artikel von ComputerBase-Leser Christoph Riedel:

- Chipfertigung: Was steckt hinter der EUV-Lithografie?

- Raytracing in Spielen VI: So werden Strahlen von GPUs beschleunigt

Dieser Artikel war interessant, hilfreich oder beides? Die Redaktion freut sich über jede Unterstützung durch ComputerBase Pro und deaktivierte Werbeblocker. Mehr zum Thema Anzeigen auf ComputerBase.