CDLABSRadonP...

Admiral

- Registriert

- Feb. 2021

- Beiträge

- 7.249

Es gab schon Fälle, in denen hat sich an den Boards technisch nichts geändert, aber zu den neuen CPUs waren sie inkompatibel. Wenn man dann ein neues Board kaufen musste, hat das zu Schäden geführt. In deiner Rechnung: Du kaufst dir das quasi gleiche (oder ein ähnliches) Board danach nochmals neu und gibst deines weiter, unterm Strich also: Doppelte Kosten. Klar, kannst du jetzt sagen, dass du doch ohnehin immer alles tauschen wollen würdest. Aber dann sollte dieser Tausch doch auch wenigstens etwas bringen. Zumindest gleiches Featureset bei geringerer Leistungsaufnahme oder sowas sollte dann drinnen sein.Uzer1510 schrieb:Naja wenn ich CPU upgrade finde ich das ehrlich gesagt nicht sooooo super schlimm wenn man auch das Board tauschen muss - entweder nutze ich die alte CPU woanders (oder familiy and friends) mit Board oder verkauf das dann halt als Bundle.

seit eh fast alles in der cpu ist braucht man doch eher selten highendboards (ausser evtl 10 GBit Netzwerk)

Dann hat man mit einem neuen Board evtl die neuen Ram Slot kontakte usw.

Ein negativer Nebeneffekt ist übrigens auch, dass die Boardhersteller dann auch ihre alten Boards schlechter loswerden und wenig Motivation haben, weitere Updates bereitzustellen. Somit verlieren die Boards dann übrigens wiederum im Gebrauchtmarkt an Wert. Am Ende gilt: Mit Ausnahme desjenigen, der die Chipsätze an die Boardhersteller zu frechen Preisen verkauft, verlieren alle. Und falls, wie es in der Vergangenheit nun einmal der Fall war, das gleichzeitig der CPU-Hersteller ist, verliert sogar vielleicht auch der, weil weniger CPUs verkauft werden.

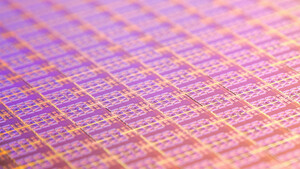

Mittels Chipletdesigns kann man übrigens als CPU-Hersteller auch wieder gut dafür sorgen, dass die neuen CPUs auch auf alten Boards laufen. Im Falle von AMD bedeutet das nämlich z.B. bloß ein angepasstes IO-DIE zu bringen und schon hätte auch Raphael noch auf AM4 Platz finden können. Vielleicht dann nur Single-CCD-Lösungen, aber immerhin. Das hätte sich übrigens auch bezahlt gemacht, dann hätte AMD viel an AM5-Murks lassen und die Plattform zu einem richtigen HighEnd-Angebot entwickeln können, bei dem klar ist: Der Grafikslot ist immer mit PCIe5 angebunden, der primäre M.2 ebenfalls; das ganze Heckmeck wäre erspart geblieben.