10 nm Class: Samsung fertigt DRAM mit weniger als 20 nm in Serie

Während bei Micron die Produktion des 20-nm-DRAMs erst anläuft, ist Samsung wieder einen Schritt weiter. Der Marktführer kündigt die Serienfertigung der ersten DRAM-Chips in einem Verfahren der 10-nm-Klasse an. Dies bedeutet eine Strukturbreite zwischen 10 und 19 nm.

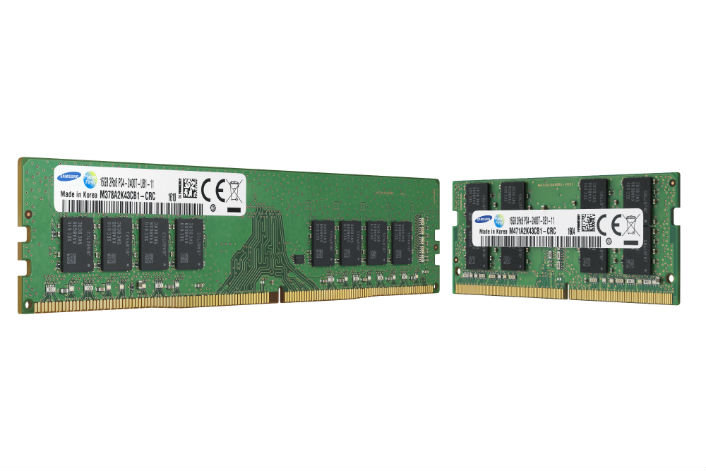

Samsung kündigt den Start der Massenproduktion der nach eigenen Angaben „industrieweit ersten“ DDR4-DRAM-Chips der 10-Nanometer-Klasse mit einer Speicherkapazität von 8 Gigabit (1 Gigabyte) an. Auch DDR4-Speichermodule (DIMM und SO-DIMM) auf Basis der neuen 8-Gb-Chips sollen bereits in Serie gefertigt werden und mit Kapazitäten von 4 bis 128 GByte zur Verfügung stehen. Entsprechende 10-nm-Class-Chips für Mobilgeräte sollen zu einem späteren Zeitpunkt folgen.

Neue Fertigung reduziert vor allem Kosten

Der Umstieg vom 20-nm-Verfahren auf die neue Generation soll nach Angaben von Samsung die Wafer-Produktivität um über 30 Prozent steigern. Mehr Chips pro Wafer bedeuten langfristig niedrigere Kosten pro Chip, wobei bedacht werden muss, dass die Entwicklung und die Umstellung auf das neue Herstellungsverfahren zunächst hohe Kosten verursachen.

DRAM der 20-nm-Generation und darunter soll im zweiten Halbjahr 2016 für sinkende Speicherpreise sorgen. Der Präsident von Nanya hatte vor einigen Wochen einen Preisverfall um bis zu 40 Prozent in diesem Zeitraum prognostiziert. Nanya selbst wird aber voraussichtlich erst 2017 in die 20-nm-Generation einsteigen.

Nebenbei bringt das neue Verfahren Verbesserungen bei Leistung und Energiebedarf mit sich. Samsung spricht von einer um 10 bis 20 Prozent reduzierten Leistungsaufnahme sowie einer Leistungssteigerung um ein Drittel von 2.400 Mbit/s (20 nm DDR4) auf 3.200 Mbit/s (10 nm Class DDR4).

Technik als Basis für die nächste Generation

Die weitere Verfeinerung des Herstellungsprozesses stellt die Ingenieure immer vor große Herausforderungen. Beim ersten Schritt in die 10-nm-Klasse sollen unter anderem eine „proprietäre Schaltkreisdesigntechnologie“ sowie die sogenannte Quadruple-Patterning-Lithografie die neue Zellstruktur ermöglicht haben. Für weitere Verbesserungen sollen Verfeinerungen der „dielectric layer deposition technology“ gesorgt haben. Damit sind hauchdünne dielektrische Schichten gemeint, deren Dicke nur wenige Ångström umfasse.

Dank Quadruple Patterning habe man bestehende Fotolithografie-Ausrüstung weiter nutzen können und musste nicht auf Techniken wie EUV zurückgreifen. Nach dem ersten Schritt in die 10-nm-Klasse, den Samsung branchentypisch als 1x bezeichnet, soll die Technik auch für die nächste Verkleinerung (1y) als Grundlage dienen.