Forschung: Kleinster SRAM-Speicher mit Surrounding Gate Transistor

Vertikale Nanodrähte (Nanowires) für den Transistor der Zukunft: Auf dem Imec Technology Forum hat Imec zusammen mit dem Startup Unisantis einen Surrounding Gate Transistor (SGT) enthüllt, der die bei vielen Firmen geplante Gate-all-around-Technik in vertikaler Ausrichtung nutzt und dadurch einen großen Vorteil bietet.

„Gate all around“ (GAA) ist bei allen großen Halbleiterherstellern fest in den Roadmaps verankert. Die Planungen für die Nutzung gehen dabei mindestens schon 30 Jahre zurück, doch die Probleme waren seinerzeit kaum lösbar. Im letzten Jahr hatte Samsung jedoch bereits vermeldet, nach der 4-nm-Fertigung erstmals GAA zu nutzen. Die Basis ist dabei der von aktuellen Transistoren auf Basis von FinFET sehr ähnlich, aber anstatt „nur“ von drei Seiten, soll – wie der Name schon vermuten lässt – Gate all around die Nanowires komplett umschließen und so den quasi „perfekten Transistor“ ermöglichen. Der Surrounding Gate Transistor (SGT) ist dabei nicht der horizontale sondern der schwierigere vertikale Ansatz, der jedoch zusätzliche Vorteile bietet.

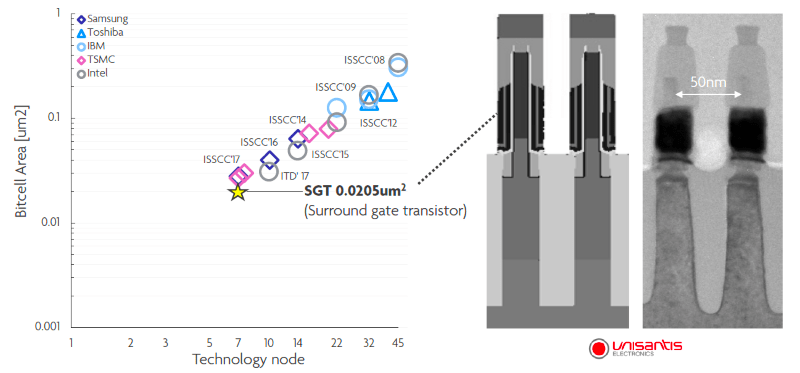

Studies show that the vertical gate-all-around SGT-based cells have a 20-30% reduced area compared to horizontal gate-all-around FETs, while also outperforming these in terms of operating voltage, standby leakage and stability.

Der Erfinder des NOR- und NAND-Flashs arbeitet nun als CTO des Startups Unisantis an der Umsetzung der Theorien, die er vor 30 Jahren selbst vorgestellt hatte. Nachdem bereits 2014 das SGT-Projekt angekündigt wurde, werden nun erste Zahlen geliefert. Mit einer Fläche einer standardisierten 6T-SRAM-Zelle zwischen 0,0184 und 0,0205 µm² wird Samsungs derzeit bester 6T-SRAM-Chip auf Basis der noch nicht verfügbaren 7-nm-EUV-Fertigung mit 0,026 µm² Fläche deutlich geschlagen. Es ist aktuell die kleinste SRAM-Zelle, die klassische Halbleiter bei der 5-nm-Fertigung inklusive EUV-Nutzung erreichen könnten – so wird auch der Bogen zu GAA bei Samsung in 4 nm geschlagen. Rein von der Fläche dürfte dies am Ende ähnlich werden, es bleiben jedoch die theoretischen Vorteile von SGT gegenüber normalen GAA.

Die 5-nm-EUV-Fertigung für DRAM, NAND-Flash und SRAM soll sich in erster Linie für dieses neue SGT-Verfahren anbieten. Für klassische Logic-Chips hingegen weniger, denn nach aktuellem Stand würde es drei dieser neuen Transistoren benötigen, um die Leistung eines vergleichbaren FinFETs zu erzielen. Eine der Baustellen am Design ist es deshalb, diese Lücke zu schließen, da sie bei ungefähr gleichen Kosten dort sonst nicht zur Verwendung kommen wird. Wie EE Times berichtet besteht die Herausforderung auch darin, das Design der Forschungsgruppen von Imec und Unisantis fertig für die Massenproduktion bei einem der großen Halbleiterhersteller zu machen. Bis zum Serieneinsatz werden deshalb noch ein paar Jahre vergehen.