Milan X mit 3D V-Cache: AMD plant CPUs der Epyc-Serie mit 768 MB L3-Cache

AMD hatte zur Ankündigung der um einen gestapelten L3-Cache ergänzten Ryzen 5000 bereits damit kokettiert, dass sich die Technologie auch in Server-CPUs gut anbieten würde. Auf Twitter gestreute Gerüchte deuten jetzt darauf hin: Milan wird als Milan X mit 768 MB L3-Cache, davon 512 MB 3D V-Cache, neu aufgelegt.

Für Ryzen 5000 ist 3D V-Cache schon offiziell

Offiziell bekannt ist, dass AMD noch in diesem Jahr mit der Produktion von Ryzen-5000-Prozessoren beginnen wird, die nicht nur die bis dato pro 8-Kern-Chiplet (CCD) belichteten 32 MB L3-Cache enthalten, sondern pro CCD weitere 64 MB. Pro CCD ergeben sich somit 32 MB + 64 MB = 96 MB Cache, ein Ryzen 5000 mit 16 Kernen und damit zwei CCDs kommt damit in Summe auf 192 MB [2 × (32 MB + 64 MB)].

Milan X erreicht mit 8 CCDs 768 MB L3-Cache

Mit Milan X scheint AMD dieselbe Technologie in naher Zukunft auch für eine Erweiterung der Epyc-Serie auf Basis der Milan-Architektur (Chiplet-I/O-Die-Ansatz mit Zen 3) zu nutzen, offensichtlich mit unveränderter Basis. In der Spitze, also auf Basis eines 64-Kern-Prozessors mit 8 CCDs, werden so 8 × (32 MB + 64 MB) = 768 MB L3-Cache möglich.

Das behauptet zumindest der in der Regel treffsichere Twitter-Nutzer ExecutableFix und hat in diesem Zusammenhang gleich vier potentielle Milan-X-Modelle beim Namen genannt: Epyc 7773X, 7573X, 7473X und 7373X mit 64, 32, 24 respektive 16 Kernen. Die nachfolgende Tabelle enthält diese Modelle sowie die anderen bisher verfügbaren Milan-Prozessoren.

| Modell | Kerne/Threads | Basistakt/max. Turbo | L3-Cache | DDR4 (1DPC) | TDP (default) | cTDP Min/Max | Preis |

|---|---|---|---|---|---|---|---|

| Kolportiere Milan-X-Modelle (Gerücht) | |||||||

| Epyc 7773X | 64/128 | 2,20/3,50 | 768 MB | 3200 MHz | 280 W | ? | ? |

| Epyc 7573X | 32/64 | 2,80/3,60 | 768 MB | 3200 MHz | 280 W | ? | ? |

| Epyc 7473X | 24/48 | 2,80/3,70 | 768 MB | 3200 MHz | 240 W | ? | ? |

| Epyc 7373X | 16/32 | 3,05/3,80 | 768 MB | 3200 MHz | 240 W | ? | ? |

| Reguläre Milan-Modelle für 2-Sockel-Systeme | |||||||

| Epyc 7763 | 64/128 | 2,45/3,50 | 256 MB | 3200 MHz | 280 W | 225 W/280 W | $7.890 |

| Epyc 7713 | 64/128 | 2,00/3,675 | 256 MB | 3200 MHz | 225 W | 225 W/240 W | $7.060 |

| Epyc 7663 | 56/112 | 2,00/3,50 | 256 MB | 3200 MHz | 240 W | 225 W/240 W | $6.366 |

| Epyc 7643 | 48/96 | 2,30/3,60 | 256 MB | 3200 MHz | 225 W | 225 W/240 W | $4.995 |

| Epyc 7543 | 32/64 | 2,80/3,70 | 256 MB | 3200 MHz | 225 W | 225 W/240 W | $3.761 |

| Epyc 7513 | 32/64 | 2,60/3,65 | 128 MB | 3200 MHz | 200 W | 165 W/200 W | $2.840 |

| Epyc 7453 | 28/56 | 2,75/3,45 | 64 MB | 3200 MHz | 225 W | 225 W/240 W | $1.570 |

| Epyc 7443 | 24/48 | 2,85/4,00 | 128 MB | 3200 MHz | 200 W | 165 W/200 W | $2.010 |

| Epyc 7413 | 24/48 | 2,65/3,60 | 128 MB | 3200 MHz | 180 W | 165 W/200 W | $1.825 |

| Epyc 7343 | 16/32 | 3,20/3,90 | 128 MB | 3200 MHz | 190 W | 165 W/200 W | $1.565 |

| Epyc 7313 | 16/32 | 3,00/3,70 | 128 MB | 3200 MHz | 155 W | 155 W/180 W | $1.083 |

| Milan-F-Modelle mit Maximal-L3-Cache | |||||||

| Epyc 75F3 | 32/64 | 2,95/4,00 | 256 MB | 3200 MHz | 280 W | 225 W/280 W | $4.860 |

| Epyc 74F3 | 24/48 | 3,20/4,00 | 256 MB | 3200 MHz | 240 W | 225 W/240 W | $2.900 |

| Epyc 73F3 | 16/32 | 3,50/4,00 | 256 MB | 3200 MHz | 240 W | 225 W/240 W | $3.521 |

| Epyc 72F3 | 8/16 | 3,70/4,10 | 256 MB | 3200 MHz | 180 W | 165 W/200 W | $2.468 |

| M-lan-P-Modelle für 1-Sockel-Systeme | |||||||

| Epyc 7713P | 64/128 | 2,00/3,675 | 256 MB | 3200 MHz | 225 W | 225 W/240 W | $5.010 |

| Epyc 7543P | 32/64 | 2,80/3,70 | 256 MB | 3200 MHz | 225 W | 225 W/240 W | $2.730 |

| Epyc 7443P | 24/48 | 2,85/4,00 | 128 MB | 3200 MHz | 200 W | 165 W/200 W | $1.337 |

| Epyc 7313P | 16/32 | 3,00/3,70 | 128 MB | 3200 MHz | 155 W | 155 W/180 W | $913 |

768 MB L3 von 16 bis 64 Kernen

Beim Blick auf die vier SKUs fällt auf: Alle sollen die vollen 768 MB L3-Cache nutzen, was – sofern Milan X die Milan-Architektur nur auf den Kopf stellt – nur dann funktioniert, wenn selbst der 16-Kern-Prozessor Epyc 7373X noch alle 8 CCDs trägt, pro CCD aber nur noch zwei von acht Kernen aktiv sind. Diesen Ansatz hat AMD allerdings auch schon bei Milan verfolgt: Die F-Modelle bieten wie die größten 8-CCD-Ausbaustufen die vollen 256 MB, weil alle acht CCDs auf dem Package zu finden sind – bis hinunter zur CPU mit nur noch 16 von 64 aktiven Kernen.

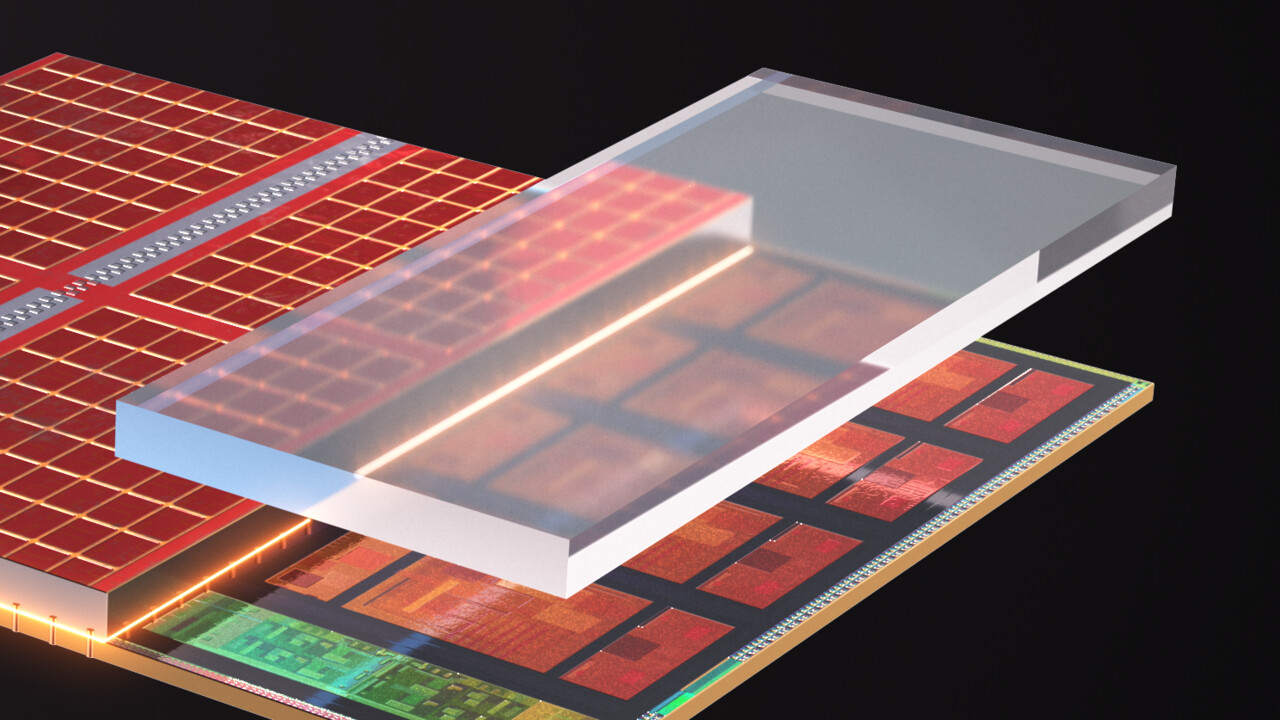

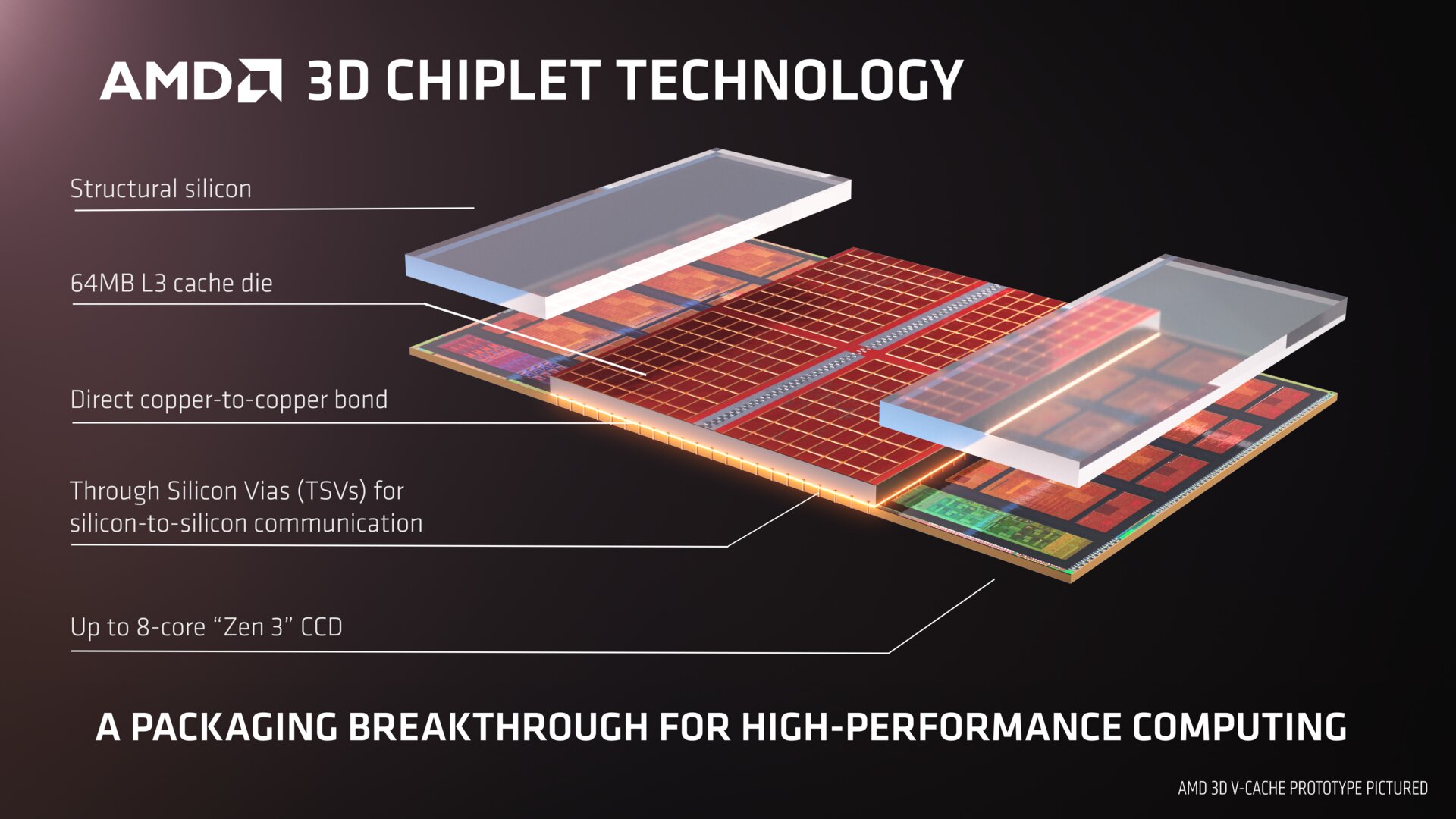

Das steckt hinter AMDs 3D-V-Cache-Technologie

Zur Vorstellung der 3D-V-Cache-Technologie im Rahmen der virtuellen Computex im Juni hatte AMD bereits im Detail über die Technologie gesprochen. Der 64 MB große zusätzliche Cache nimmt eine Grundfläche von 6 × 6 mm im CCD ein, womit er so groß wie der schon vorhandene 32 MB große L3-Cache ist.

Der aufgesetzte L3-Cache ist ein nativer 64-MB-Chip, er fungiert trotzdem als direkte Erweiterung des bestehenden L3-Caches im CCD, was keine Software-Anpassungen nötig macht, da er ohne Kontrollfunktionen und für alle der für die grundlegende Funktionalität benötigten Einheiten daherkommen kann. Da diese bereits vorhanden sind, kann AMD 64 MB reinen SRAM auf dem gleichen Raum wie zuvor 32 MB unterbringen. Zen 3 war bereits von Vornherein für diese Möglichkeit vorbereitet, die Entwicklung und Umsetzung mit Partner TSMC nahm mehrere Jahre in Anspruch, erklärte AMD.

Die Stapeltechnologie basiert auf TSVs, wie sie bereits bei diversen Stacking-Lösungen zum Einsatz kommen. Das Chipbonden erfolgt über einen direkten Kontakt der Kupferschichten, keine zusätzlichen BGA-Kontaktflächen oder ähnliches, wie sie beispielsweise Intels Ansatz mit Stacking vorsieht.

Um den zusätzlichen L3-Cache auf dem CCD unterzubringen, ohne die Höhe zu verändern, werden die CCDs der betreffenden Prozessoren in Zukunft dünner, um am Ende mit gestapeltem Zusatz-Cache wieder genau so hoch zu sein wie der I/O-Die und um letztlich unter den Heatspreader zu passen.