3D-NAND von WD & Kioxia: Auf BiCS6 folgt BiCS+ mit viel mehr Leistung

Kioxia und Western Digital entwickeln den BiCS Flash genannten 3D-NAND gemeinsam. Auf dem Investor Day hat Western Digital sowohl über den bald erscheinenden BiCS6 als auch dessen Nachfolger „BiCS+“ gesprochen, der einen „Quantensprung bei der Leistung von NAND“ darstellen soll.

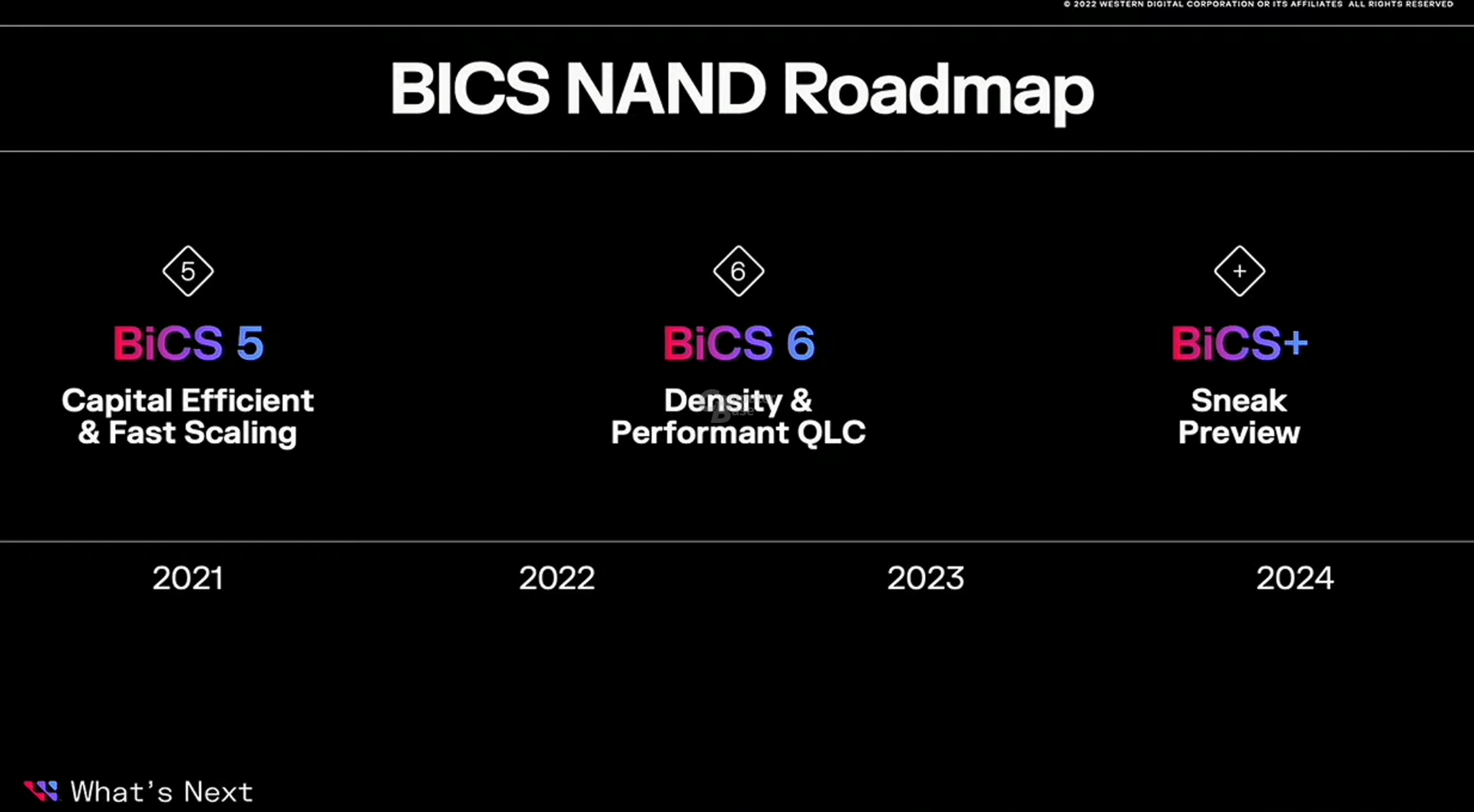

Aktuell wird zum Großteil die fünfte Generation (BiCS5) mit 112 Zellschichten in den Werken von Kioxia und Western Digital produziert, die auch in immer mehr SSDs der beiden Hersteller zu finden ist. Zum Jahresende soll dann die Produktion des Nachfolgers BiCS6 beginnen und 2023 hochgefahren werden.

BiCS6 als kleinste und schnellste QLC-Variante?

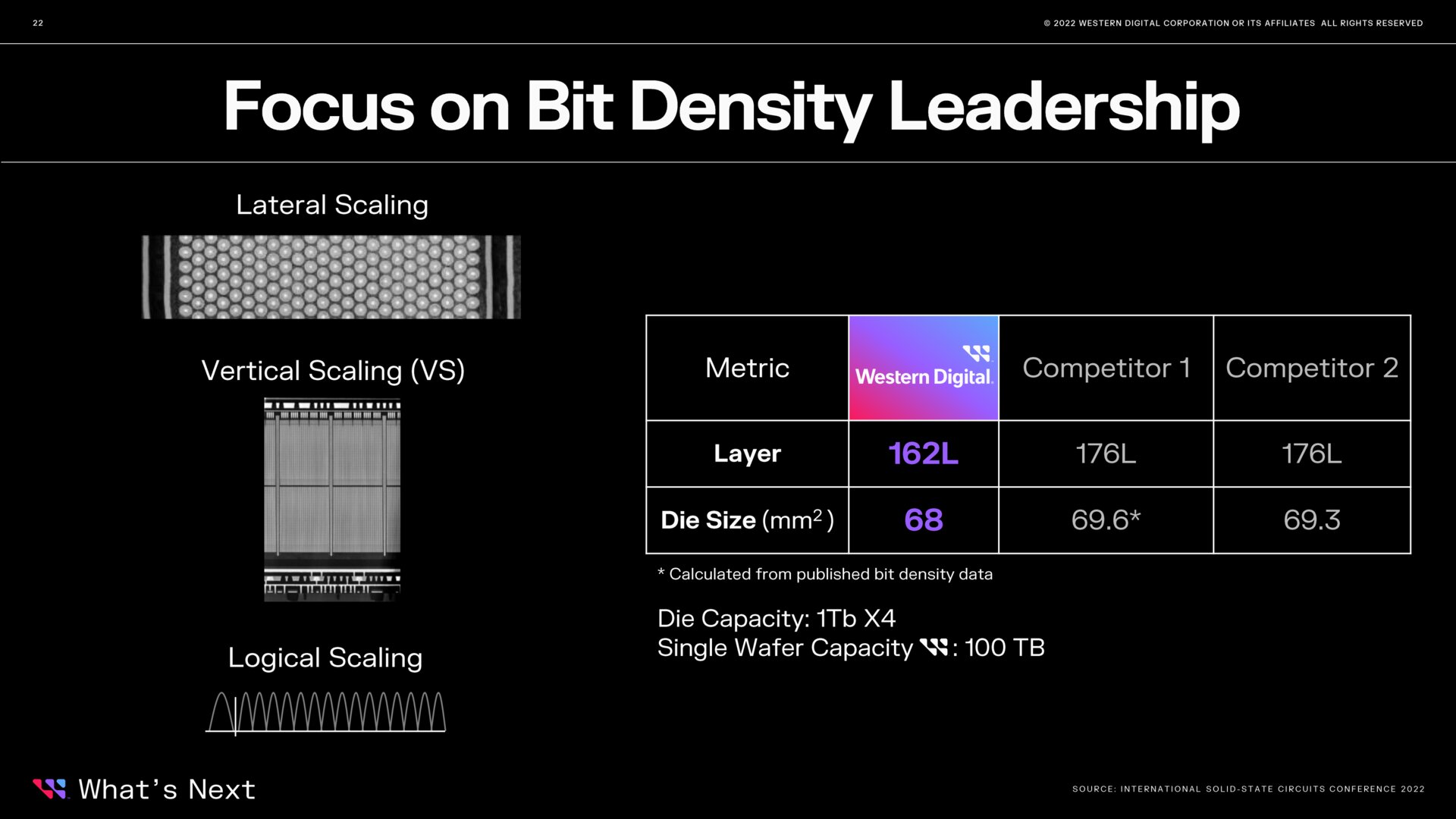

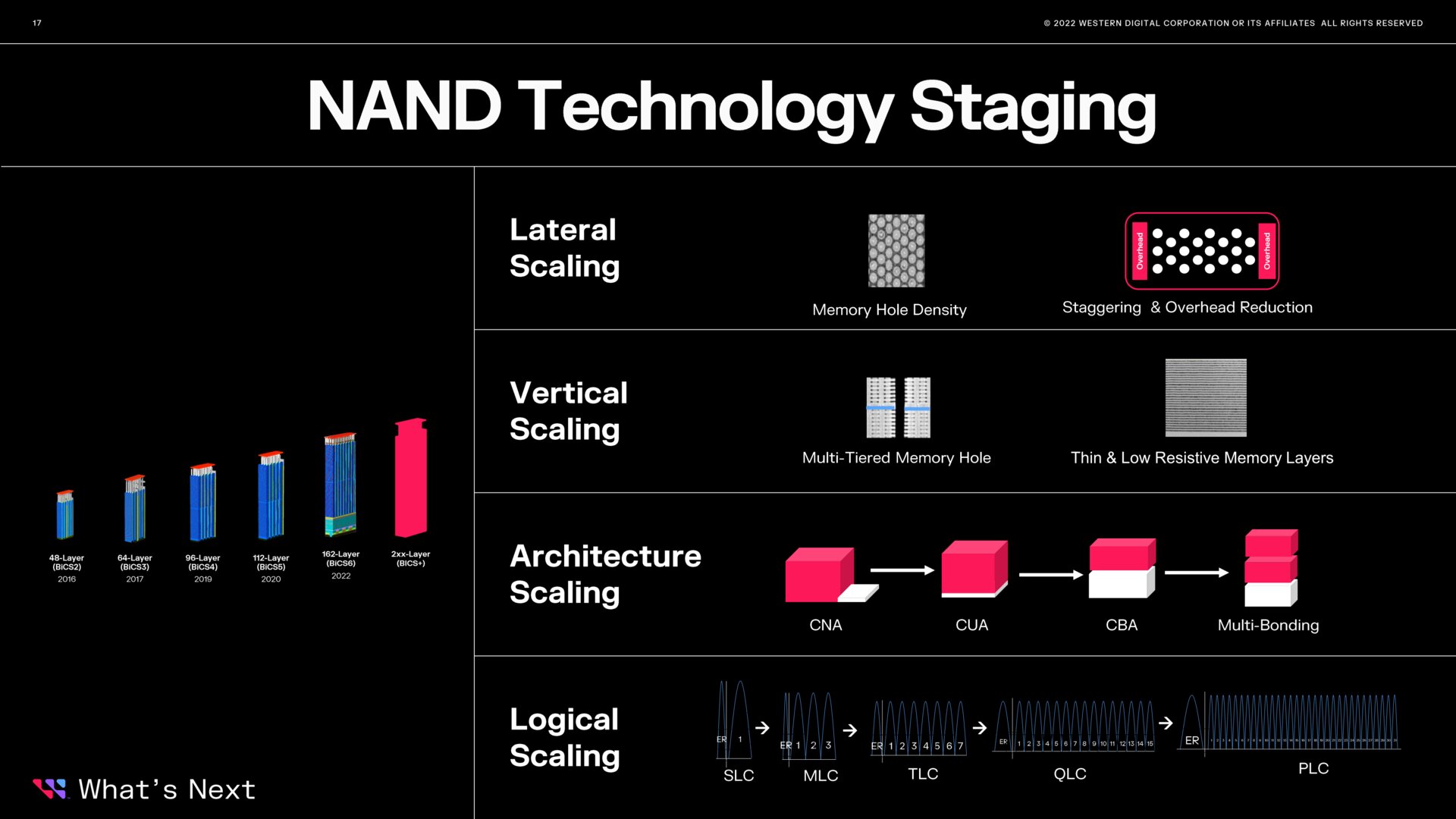

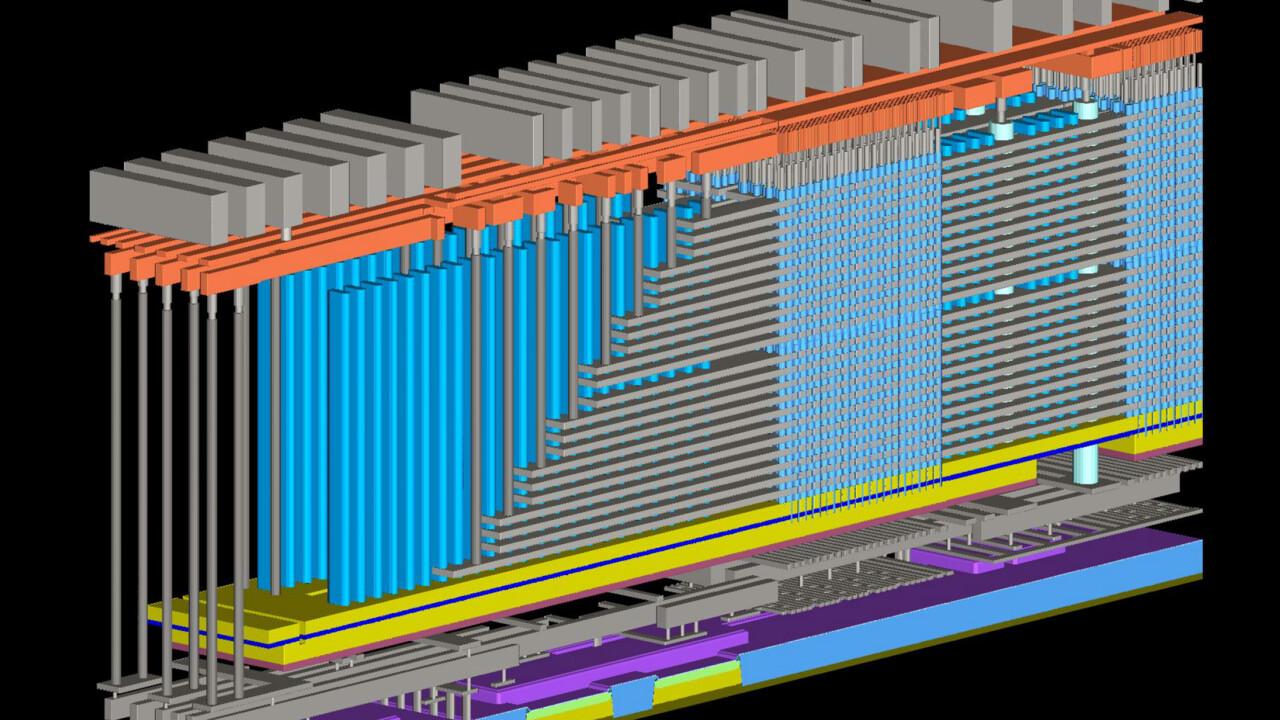

BiCS6 (Titelbild als Schema) besitzt 162 Word-Line-Layer und damit weniger als die Konkurrenten Micron, Samsung und SK Hynix, die auf 176 Layer setzen. Doch nur auf die Zahl der Ebenen kommt es nicht an, denn viele weitere Faktoren wie die Größe der Zellen und deren Abstand bestimmen die Eigenschaften des NAND-Flash.

Das hat auch Siva Sivaram, der President of Technology & Strategy von Western Digital, in seiner Präsentation auf dem Western Digital 2022 Investor Day betont. Mehr Layer bedeuten keineswegs automatisch eine höhere Flächendichte in Gigabit pro Quadratmillimeter. Zumindest die QLC-Variante des BiCS6 soll mit 68 mm² sogar aktuell das kleinste QLC-Die mit 1 Terabit Speichervolumen in der Branche darstellen. Umgerechnet wären dies rund 15,1 Gb/mm² und damit mehr als bei Intels 144-Layer-QLC (13,8 Gb/mm²) oder dem neuen 176-Layer-QLC von SK Hynix (14,8 Gb/mm²). In einer Tabelle vergleicht Western Digital mit einem weiteren Konkurrenten mit 176-Layer-QLC, bei dem es sich um Micron handeln dürfte.

Zuvor hatten Western Digital und Kioxia stets nur von der schnelleren, aber deutlich größeren TLC-Variante von BiCS6 gesprochen. Auf der neuen, aber knappen Roadmap ist von „Dichte und performantem QLC“ die Rede. Die große Schwäche von QLC-NAND, das langsame Schreiben, soll zumindest gemindert werden. Die Charge-Trap-Zellen des QLC-BiCS6 sollen sich mit 60 MB/s beschreiben (program) lassen. Das ist mehr als das Sechsfache gegenüber BiCS4 (BiCS5 gibt es nicht als QLC) und immer noch 50 Prozent mehr als bei Intels 144-Layer-QLC.

| Intel | Intel/Micron | Micron | Kioxia/WD BiCS4 | Kioxia/WD BiCS6 | Samsung V5 | SK Hynix V5 | SK Hynix V7 | |

|---|---|---|---|---|---|---|---|---|

| Typ (Bit/Zelle) | QLC (4 Bit) | |||||||

| Kapazität | 1 Tbit | 1 Tbit | 1 Tbit | 1,33 Tbit | 1 Tbit | 1 Tbit | 1 Tbit | 1 Tbit |

| Planes | 4 | 4 | 4 | 2 | 4 | 2 | 4 | ? |

| Layer (WL) | 144 | 96 | 176 | 96 | 162 | 92 | 96 | 176 |

| Die-Fläche | 74,03 mm² | 114,6 mm² | ? | 158,4 mm² | 68 mm² | 136 mm² | 122 mm² | ? |

| Dichte | 13,8 Gb/mm² | 8,9 Gb/mm² | ? | 8,5 Gb/mm² | 15,1 Gb/mm² | 7,53 Gb/mm² | 8,4 Gb/mm² | 14,8 Gb/mm² |

| Read (tR) Average | 85 µs | 90 µs | ? | 160 µs | ? | 110 µs | 170 µs | ? |

| Read (tR) Max | 128 µs | 168 µs | ? | 165 µs | ? | ? | ? | ? |

| Write (tPROG) | 1630 µs | 2080 µs | ? | 3380 µs | ? | 2 ms | 2150 µs | ? |

| Program | 40,0 MB/s | 31,5 MB/s | ? | 9,7 MB/s | 60 MB/s | 18 MB/s | 30 MB/s | ? |

| I/O | 1,2 Gb/s | 0,8 Gb/s | 1,6 Gb/s | 0,8 Gb/s | 2,0 Gb/s | 1,2 Gb/s | 0,8 Gb/s | ? |

| Block Size | 48 MB | 96 MB | ? | 24 MB | ? | ? | 24 MB | ? |

BiCS+ mit großem Leistungssprung

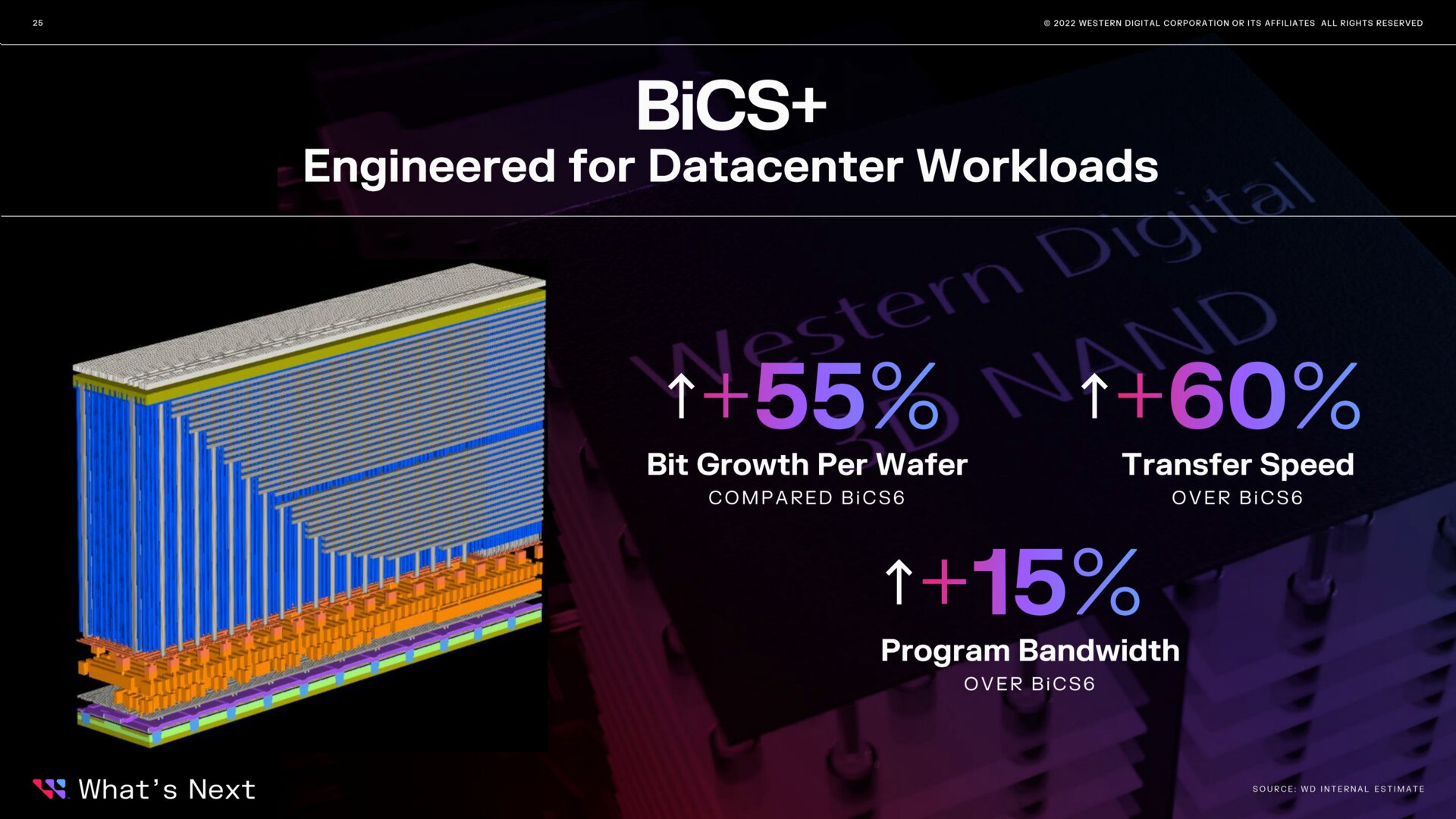

Den Zyklus von etwa 1,5 Jahren zwischen den Generationen wollen die Partner einhalten und so soll die nachfolgende Generation Ende 2023 präsentiert werden. Statt von BiCS7 spricht Western Digital von „BiCS+“. Die Anzahl der Layer soll wie bei Samsungs V-NAND V8 auf über 200 ansteigen. Durch die abermals gesteigerte Flächendichte werden 55 Prozent mehr Bit pro Wafer in Aussicht gestellt.

Noch größer soll die Steigerung bei den Transferraten ausfallen: Nicht weniger als 60 Prozent Plus werden hier genannt. Das Programmieren der Zellen soll um immerhin 15 Prozent schneller erfolgen.

Sivaram zeigte sich euphorisch und sprach von einem „Quantensprung bei der Performance von NAND“. Doch bleiben weitere Details sowie entsprechende Vorstellungen der Konkurrenz abzuwarten.

Auch die langjährige Partnerschaft mit Kioxia in den drei Joint Ventures, die verschiedenen Wege zur weiteren Steigerung der Flächendichte von NAND sowie die im Vergleich zur Konkurrenz geringeren Ausgaben für die Steigerung der Bit-Dichte waren Themen der Präsentation.

Mit insgesamt sieben Werken, davon allein sechs am Standort Yokkaichi (Japan), produzieren Western Digital und Kioxia gemeinsam über 500.000 Wafer mit NAND-Chips pro Monat. Damit liegt ihr Anteil an der weltweiten Produktion bei etwa 30 Prozent.