3D DRAM: Samsung plant mit 16 Layern für 2030

3D-NAND mit gestapelten Speicherzellen gibt es schon lange, an 3D DRAM forscht die Branche wiederum immer noch. Laut einem Bericht aus Südkorea rechnet Samsung mit dem Jahr 2030 für einen kommerziellen Start. Der Hersteller wolle 3D DRAM mit bis zu 16 Ebenen (Layer) schaffen. Micron versuche sich bisher an der Hälfte.

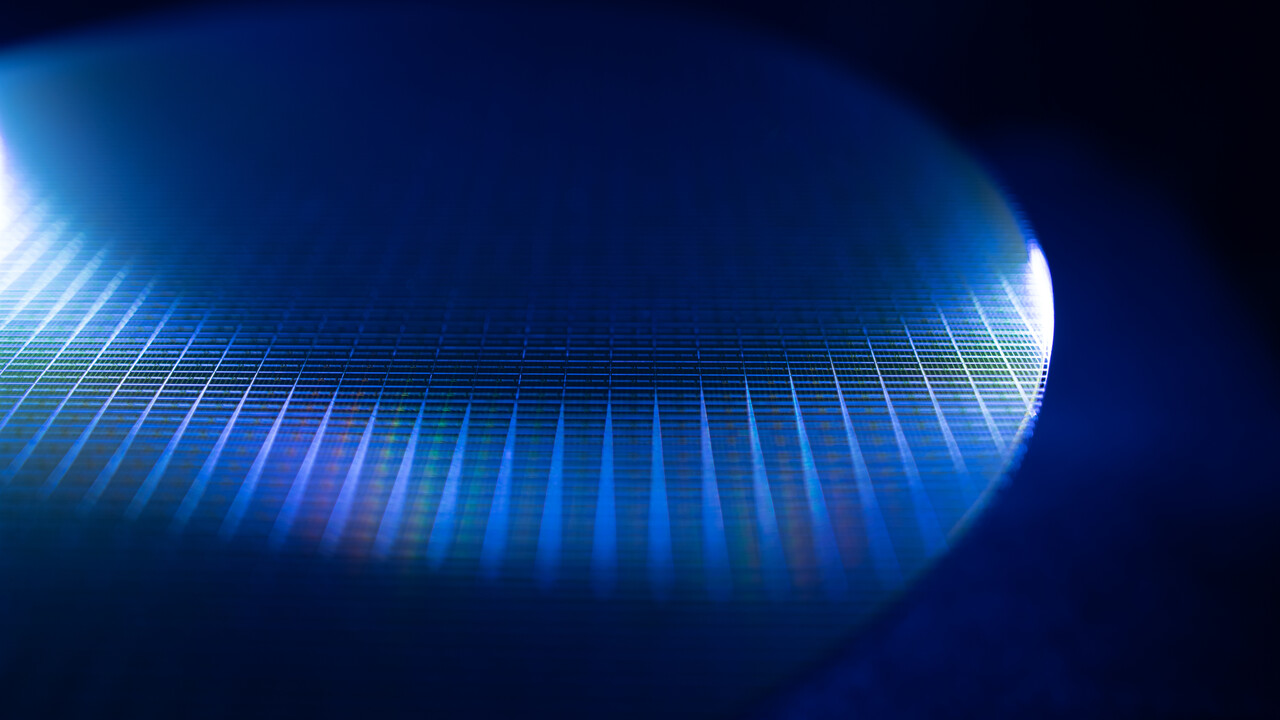

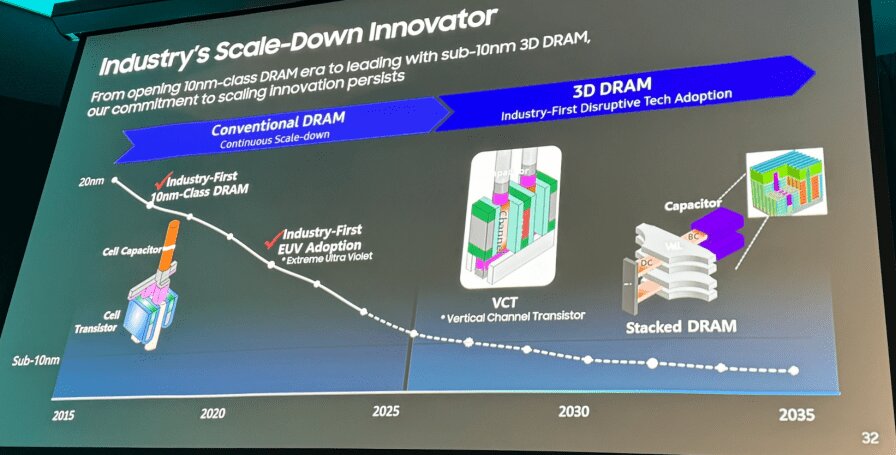

Auf das Thema 3D DRAM hatte vor einem Jahr das Startup NEO Semiconductor Aufmerksamkeit gelenkt, indem es das Konzept des „World’s First 3D NAND-Like DRAM“ alias „3D X-DRAM“ präsentierte. Schnell wurde bewusst, dass natürlich auch die großen DRAM-Hersteller ähnliche Ansätze verfolgen. So hatte Samsung bereits von seinem „Vertically stacked DRAM (VS-DRAM)“ gesprochen. Auf der MemCon 2024 gab es dann sogar eine Samsung-Roadmap zu sehen, auf der 3D DRAM erstmals gezeigt wurde. Der erste Schritt ist ein Vertical Channel Transistor (VCT), bevor der eigentliche Stacked DRAM folgt.

Etwa ab 2030 will Samsung 3D DRAM anbieten

ZDnet Korea berichtet in dieser Woche vom International Memory Workshop (IMW) 2024 über den Stand der Entwicklung bei Samsung. Demnach soll es bereits nächstes Jahr die ersten Musterchips mit VCT-Design geben. Grob für das Jahr 2030 werde der kommerzielle Start für 3D DRAM angepeilt. Dann will Samsung 16 Layer stapeln, wobei noch völlig offen ist, wie viel Speicherkapazität damit möglich wäre. Beim High Bandwidth Memory werden schon jetzt DRAM-Dies gestapelt. Beim 3D DRAM besteht wiederum der Die selbst aus einzelnen Ebenen mit Speicherzellen.

In dem Bericht heißt es, dass führende Unternehmen wie Samsung bis zu 16 Layer beim 3D DRAM erwägen. Nur Micron führe noch Versuche mit 8 Layern durch. Laut Samsung sind unter anderem neue Materialien nötig. Zusätzlich soll das sogenannte Waferbonden zum Einsatz kommen, mit dem zwei Wafer vollflächig miteinander verbunden werden. Dieses Verfahren wird mittlerweile auch bei manchem 3D-NAND genutzt.