LatinoRamon schrieb:Da hier ja einige schlaue Leute von nanos/Architektur/Qualität/Fertigungsprozess und Leistung u.s.w. was posten dann könnt ihr das mir ja mal erklären was für ein vorteil oder nachteile (keine Ahnung) die niedrige nano technologie hat? wird ja auch irgendwann eine32 nm-Silizium Technologie geben, oder erklärt mir doch mal was genau die Bedeutungen haben wie z.b. up to four 16 bit Hyper transport oder split power planes, 8 Bit breiten I/O-Anschluss, 4 Double Precision (128 Bit) Gleitkommaoperationen, Bit-Manipulation (LZCNT/POPCNT), HyperTransport-Anbindung Version 3, Optimierungen der Sprungvorhersage und den Ausführungseinheiten und was genau die Vorteile von diesen Verbesserungen sind und auch vom L3 Cache der eingesetzt wird?! wieviel MB reicht aus um die Leistung zu steigern? Könnt ihr mir da helfen? Ich meine, da die meisten ganz genau wissen welcher CPU mehr Preis/Leistung und Qualität ereicht kennt ihr ja die genauen Bedeutungen und könnt ja danach vergleichen, oder? Also mich würde das freuen wenn ich zu diesem Thema ne genaue erklärung bekommen würde und empfehlt mir bitte nicht irgendeine Internet Seite. Ich möchte das gerne von euch, mit euren eigenen Worten erklärt bekommen, wenn es möglich währe? Bitte!

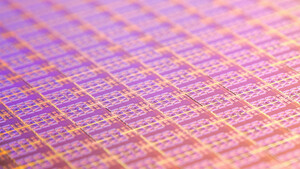

- 32nm = Gatelänge im Transistoren Gatter. Um eine solche Strukturbreite zu erreichen muss man physikalisch sehr tricksen. Einige Tricks heißen Stretched Silicon (auseinandergezogenes Silizium Atomgatter), SOI (eine Isolatorschicht ermöglicht kleinere Transistoren und somit kürzere Schaltzeiten) usw. Verschiedene Hersteller verwenden verschiedene Tricks die verschieden viel bringen, ein Vergleich nur über die Strukturbreite ist als einfach Blödsinn.

- 4 16Bit HT Links sind einfach mehr als jetzt. Ein Opteron 8xx bietet z.Z. maximal 3 HT Links.

- Split Power Planes bedeutet, dass jeder Kern sein eigenes Powermanagement bekommt und jeder Kern separat getaktet werden kann

- Keine Ahnung wo du den 8 Bit I/O Anschluss hast

- 4x 128Bit Gleitkomma Operationen: Im SIMD Modus (siehe wiki) können 4 128Bit genaue Fliesskommazahlen gleichzeitig erzeugt werden. Das hat aber keinen Einfluss auf Skalare Berechnungen, wie sie in einer CPU am meisten benötigt werden.

- Die angesprochenen Bit Manipulationen sind Erweiterungen der SSE Einheiten, die direkt von Hand programmiert und/oder in Compiler eingebaut werden können um die Performance zu verbessern.

- HT3 ist einfach die 3. Version des HT Links, der einfach höher getaktet ist.

- Verbesserte Sprungvorhersage: Die Sprungvorhersage ist im Prinzip eine Tabelle, die aufgrund von vorhergehenden Sprüngen Einträge speichert. Anhand dessen kann ermittelt werden, welcher Sprung folgt und dieser wird dann schonmal in die Pipeline geschoben. Ist der Sprung trotzdem falsch, wird das berechnete Ergebnis verworfen. Je mehr Einträge in der Tabelle, desto genauer die Sprungvorhersage.

- Optimierungen in den Ausführungseinheiten kann vieles heißen, gemeint ist hier aber der OOO Teil der Einheiten, also nicht das was während sondern was vor und nach der Berechnung mit Daten und Befehlen passiert.

- L3 Cache: Einfügen einer weiteren Cache Hierarchie. Das hat zur Folge, dass man den L2 Cache schneller aber dafür kleiner gestalten kann. Wie gut dieses Konzept ist wurde bei Intels Gallatin Kern (Pentium 4EE im Northwood Zeitalter) schon mit grossem Erfolg gezeigt. AMDs L3 Cache ist ähnlich wie beim Gallatin, nur exklusiv gehalten und ist jeweils für 2 Kerne designt, nicht nur für einen.