RKCPU schrieb:

Gerüchte zu Zen-7-Architektur: AMD soll mit A14-Fertigung und neuen Kern-Varianten planen - Hardwareluxx

https://share.google/so8YXYcWYux54n8GY

Das basiert auf MLID. Was er da mit A14 erzählt passt nicht zu dem was er zum Launchdatum (Ende 2027 Anfang 2028) erzählt.

Technology Leadership Dr. Yuh-Jier Mii, TSMC North America Symposium

N2 ist 2025 und AMD kommt 2026 mit Zen6, A14 ist 2028 AMD könnte also frühestens Ende 2028 mit Zen 7 auf A14 kommen, eher 2029. Was sehr sehr spät für Zen 7 wäre.

RKCPU schrieb:

Zen 7 (1,4 nm) soll 2 statt 1 MB L2 bekommen, dafür den ganzen L3 als 4nm Chiplett darunter.

Hier ist er inzwischen zurückgerudert, es soll Varianten mit ausgelagertem L3 geben und Varianten mit inkludiertem L3.

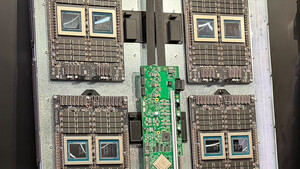

Was er gezeigt hat war ein Zen 7 dense Chiplet mit 33 Kernen. Was sehr komisch anmutet.

RKCPU schrieb:

Auch die Stromversorung von unten kommt dann.

Die Stromversorgung kommt immer von unten, oder meinst Du Backside Power Distribution Network?

Backside Power wäre A16. Backside Power Distribution Network mit A14 kommt erst 2029.

RKCPU schrieb:

Bei Zen 7 steigt via DDR6 die Bandbreite, vielleicht sogar noch kräftiger via 192 Bit Anbindung.

Das warten wir Mal in Ruhe ab.

Der LPDDR6 Standard ist wohl fertig aber noch nicht veröffentlicht.

Zum DDR6 Standard gibt es noch keine Anzeichen. Warten wir erst Mal in Ruhe ab, wann der DDR6 Standard veröffentlicht wird. Einstweilen hat DDR5 durch CUDIMM noch einiges Potential, ebenso wie die Server mit MRDIMM auf DDR5 genügend Potential haben.

Also wieso sollte sich die JEDEC mit DDR6 beeilen?

RKCPU schrieb:

Unklar bei Zen 6 noch N2 - dann EPIC - oder N2X für Alle. Bzgl. Timing könnte der 12-Core in N2X kommen für ultimative Single-Core Performance, beim EPIC weniger wichtig.

Hier ist gar nichts unklar. Zen 6 wird N2.

Alles andere mit N2 ist 2026 noch nicht in HVM. N2X kommt erst 2027, nach A16. Wenn ich das Diagramm oben ansehe ist es wahrscheinlich die 2. Jahrehälfte 2027. Da erzählen wieder Leute, die keinen blasen Schimmer haben, Blödsinn.

Außerdem ist es sehr fraglich, dass AMD N2X einsetzen wird. Das wäre nur denkbar, wenn AMD unterschiedliche CCDs für Ryzen und EPYC fertigen ließe. Die X-Prozesse haben höhere Leakströme, das ist nur akzeptabel, wenn man ohnehin vor hat über die Kotzgrenze zu gehen. Für Server ist es ein No Go. Für die meisten Desktopsysteme ist es ebenfalls kontraproduktiv.

AFAIK verwendet AMD bei den CPUs ausschließlich HD-Zellen. Wenn AMD nicht einmal die HP-Zellen der Standardprozesse verwendet, wieso sollte dann AMD auf einen Spezialprozess mit höhere Spannung, höherer Frequenz und höherer Power gehen?

Es gibt weit interessantere Fragen zu Zen 6:

- Zen 5 kann mit realistischen Code maximal eine IPC von 5 erreichen, kommt Zen 6 mit der maximale IPC näher an die theoretisch möglichen 6?

- Setzt AMD tatsächlich übergreifend Advanced Packaging bei Zen 6 ein? Wie nutzt AMD die dadurch verringerte Package Power?

- Nach dem aktuellen Stand der Informationen gibt es nur 96 Kerne bei den EPYC mit classic Kernen. Turin classic hatte 128 Kerne.Wie schließt AMD diese Lücke?

- Das Turin dense CCD hat 32 Kerne, so wie es heißt alle in einem CCX, wie bekommt AMD das hin?