IDF: Intel rüstet sich für 1.000.000 Cores

Intel hat im Rahmen des IDF ein weiteres Detail seiner Nehalem-Prozessorfamilie bekannt gegeben: Sie enthalten einen neuen Interrupt Controller, der je nach Betriebsmodus für weit über 1.000.000 Prozessoren gerüstet ist.

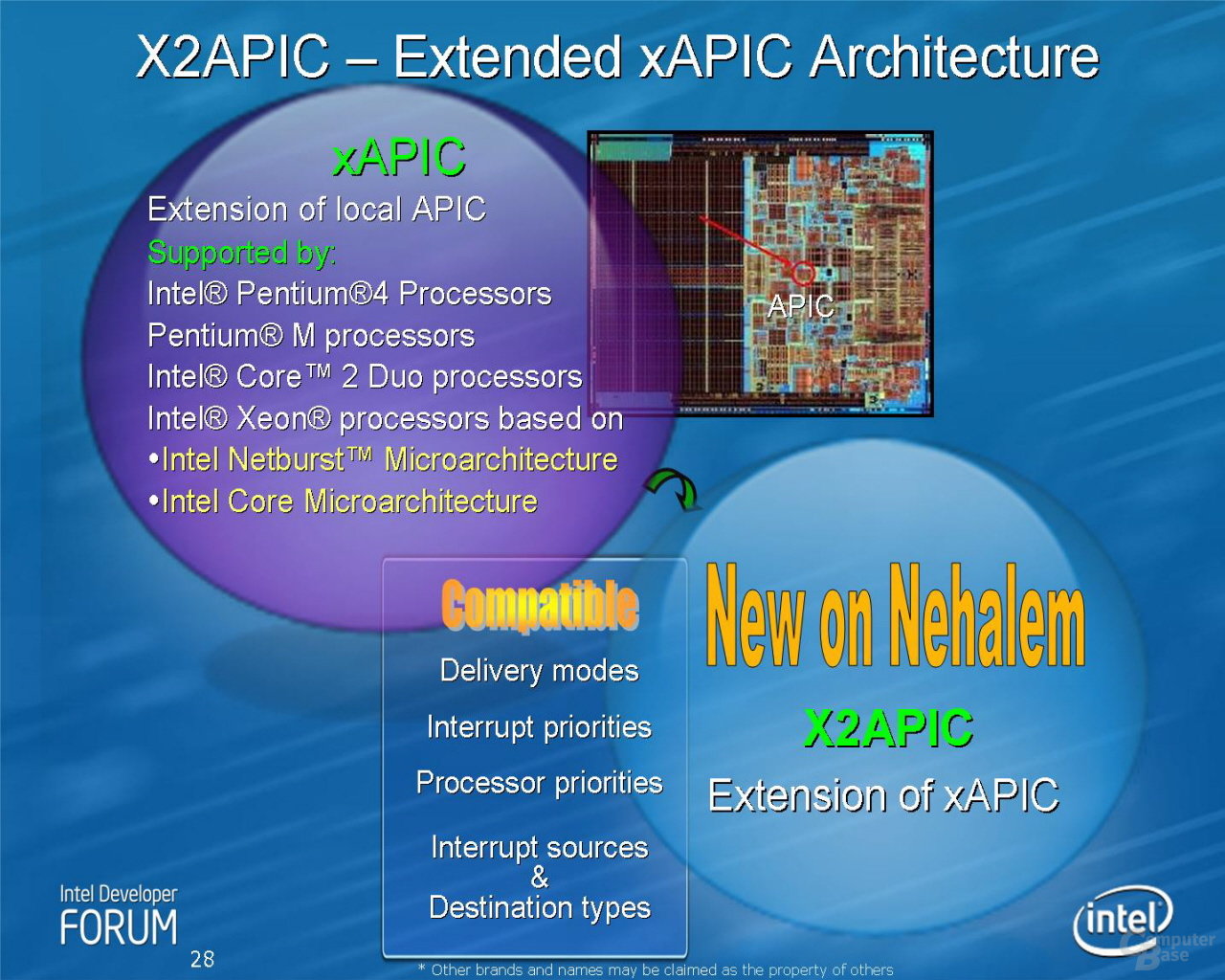

Im Rahmen der Präsentation „Buckle Up: It is Penryn Inside!“ hat Stephen S. Pawlowski, Senior Fellow und Leiter der Architekturplanungsgruppe innerhalb Intels, eine weitere, bisher noch nicht bekannte Neuerung von Nehalem verraten: er hat einen neuen Advanced_Programmable_Interrupt_Controller (APIC).

Interrupts dienen innerhalb des Prozessors dazu, den Prozessor über Ausnahmesituation zu informieren und die Ausführung bestimmter Routinen, der so genannten Unterberechungsbehandlung, zu veranlassen. Interrupts können verschiedene Ursachen haben. Neben Zeitgebern kann z.B. die Tastatur (bzw. der Tastatur-Controller) dem Prozessor mitteilen, dass ein neues Zeichen im Tastaturpuffer vorhanden ist und dieses auf der Stelle in den Hauptspeicher übertragen werden muss – der Prozessor unterbricht dabei sofort seine aktuelle Arbeit. Interrupts können auch verschiedene Prioritäten besitzen und sind für die Funktion eines modernen Prozessors unbedingt erforderlich.

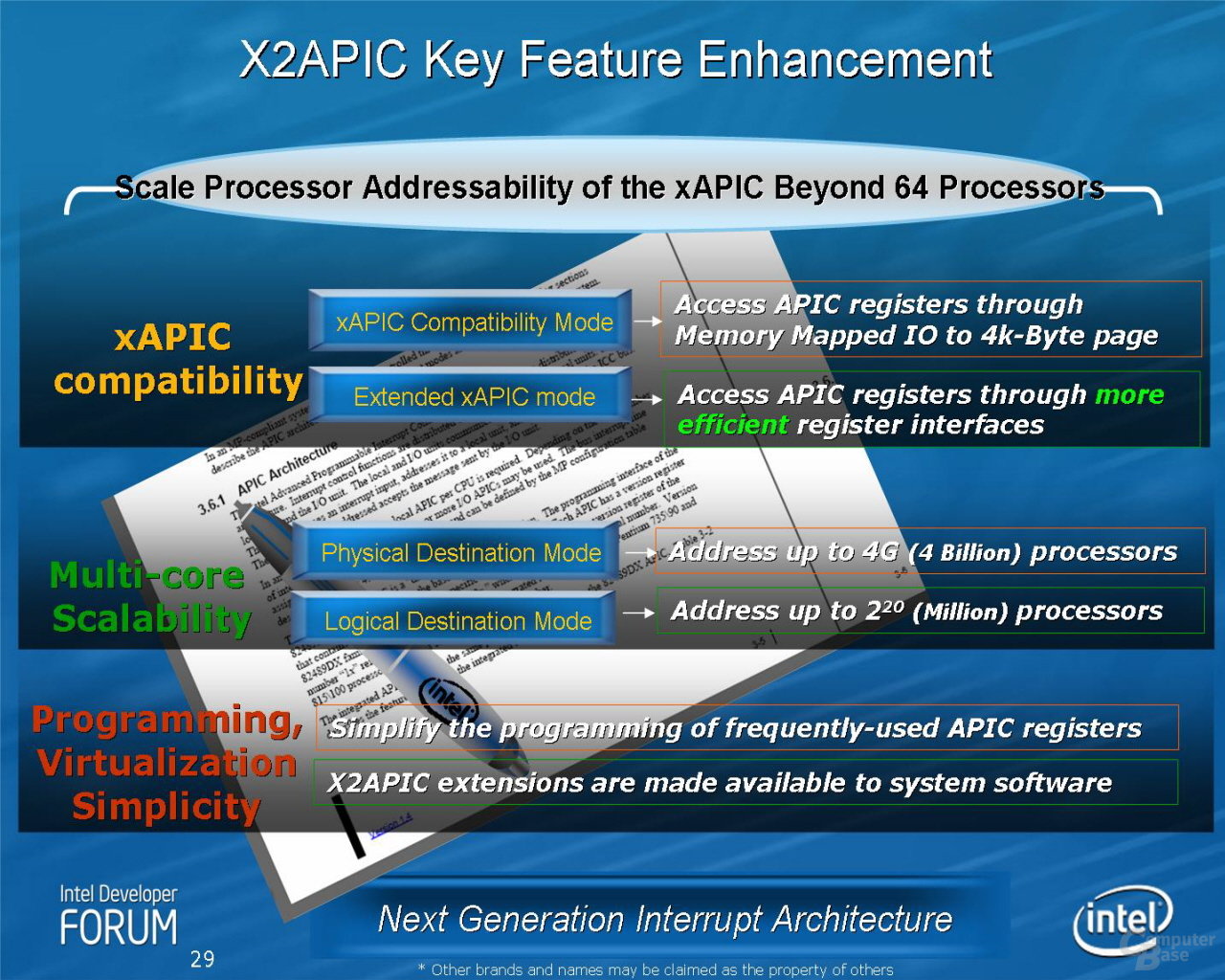

Der aktuelle APIC im Pentium 4 und Core 2 Duo ist im Vergleich zu seinen Vorgängern bereits ein Extended APIC (xAPIC). Er wurde interessanterweise schon 1994 für den erst im Jahr 2000 eingeführten Pentium 4 (Netburst-Architektur) entwickelt und unterstützt im von Windows nahezu ausschließlich genutzten „Logical Destination Mode“ innerhalb eines Computers bis zu 64 Prozessorkerne (im Vortrag ist von 60 die Rede), seien sie virtuell (Multithreading) oder real (Multicore). Für die mit Nehalem und den späteren Architekturen geplanten Prozessoren und Konfigurationen ist das offenbar nicht mehr genug.

Mit Nehalem hält daher Extended xAPIC (X2APIC) Einzug. Mit ihm werden einige Einschränkungen des xAPIC beseitigt. Im von Windows genutzten Modus werden bis zu eine Millionen Prozessoren unterstützt, im „Physical Destination Mode“ sind es sogar bis zu vier Milliarden. Auch an Virtualisierung wurde gedacht, so dass in einigen Fällen (z.B. das Ändern der Interrupt-Priorität) kein VMEXIT anschließendes VMENTRY mehr nötig ist (Details sind der Rede von Pawlowski zu entnehmen). Zu guter Letzt kann der neue X2APIC über Memory Mapped I/O oder Machine Specific Registers (MSR) angesprochen werden – bislang wurde nur der erste Fall unterstützt.

Pawlowski sieht sich mit der Unterstützung für 1.000.000 Prozessoren/Threads für die Zukunft bestens gerüstet.