Samsung: Massenfertigung von 3D-NAND mit 3 Bit gestartet

Samsung, als Vorreiter bei der Fertigung von NAND-Flash-Speicher mit dreidimensionalem Aufbau, ist der Konkurrenz einen weiteren Schritt voraus. Das Unternehmen kündigt den Beginn der Massenproduktion von 3D-NAND mit 3 Bit pro Speicherzelle (TLC) an.

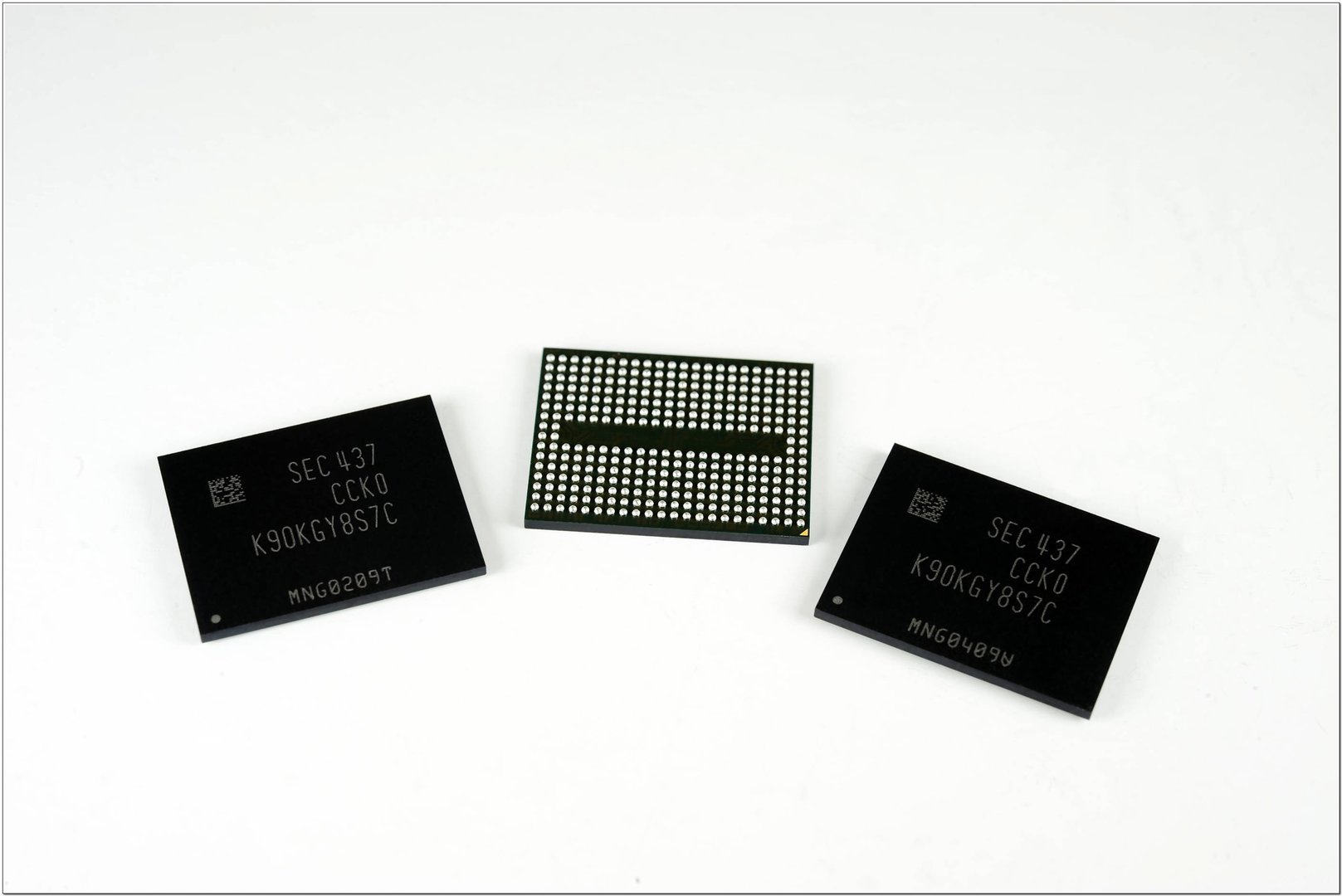

Der „3-Bit V-NAND“ basiert auf der zweiten Generation der V-NAND-Technik mit 32 übereinander liegenden Zellschichten. Ein Die bietet eine Kapazität von 128 Gigabit. In Relation zur Chip-Fläche wird eine deutlich höhere Speicherdichte als mit planarem (2D) TLC-Speicher erreicht. Angaben zur Chip-Fläche werden zwar nicht gemacht, jedoch deutet die „mehr als verdoppelte Wafer-Produktivität“ darauf hin: „Compared to Samsung’s 10 nanometer-class 3-bit planar NAND flash, the new 3-bit V-NAND has more than doubled wafer productivity.“

Mehr Gigabit pro Fläche bedeutet kleinere Dies und damit mehr Dies pro Wafer und entsprechend niedrigere Kosten pro Chip. Der 3-Bit-V-NAND soll in günstigen SSDs für Konsumenten wie der noch für dieses Jahr erwarteten 850-Evo-Serie Verwendung finden. Eine konkrete Produktankündigung gibt es bisher nicht, jedoch zeigte der Hersteller auf der IFA bereits eine Attrappe der 850 Evo. Die 850 Pro mit 2-Bit-V-NAND kam rund zwei Monate nach dem Start der Massenfertigung des dreidimensionalen MLC-Speichers auf den Markt.

Andere NAND-Fertiger wie IMFT, SK Hynix und Toshiba/SanDisk werden voraussichtlich erst ab dem kommenden Jahr 3D-NAND in hoher Stückzahl produzieren.