Intel Skylake: Grafikeinheiten der Gen9 mit Änderungen im Detail

Ungewohnt schweigsam gab sich Intel bisher zur neuen Skylake-Architektur. Bei Einführung der ersten CPU-Modelle wurden testende Redaktionen für weitere Informationen auf später vertröstet. Öffentlich einsehbare Dokumente geben nun aber einige Details zu den integrierten Grafiklösungen der Gen9 preis.

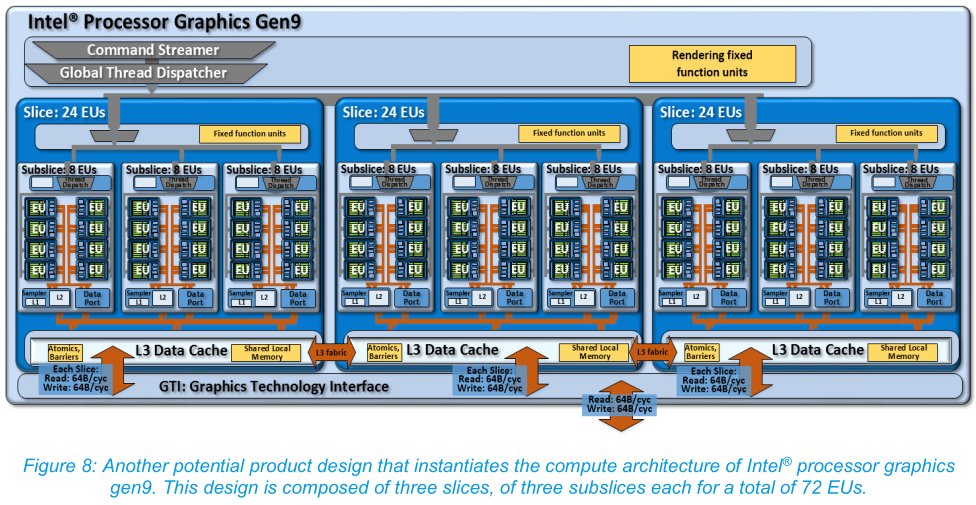

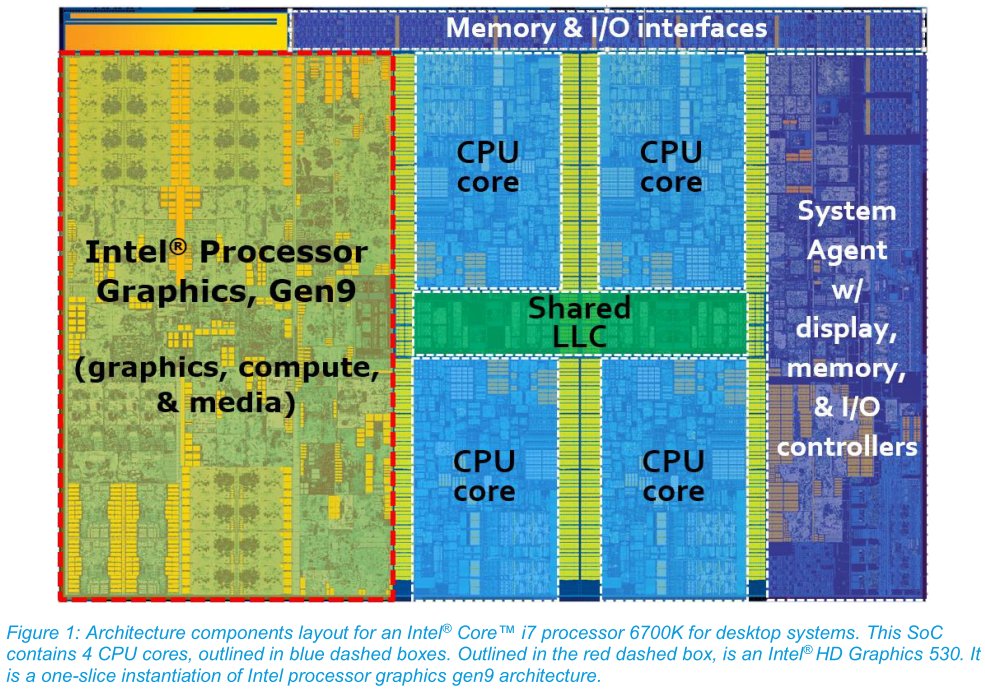

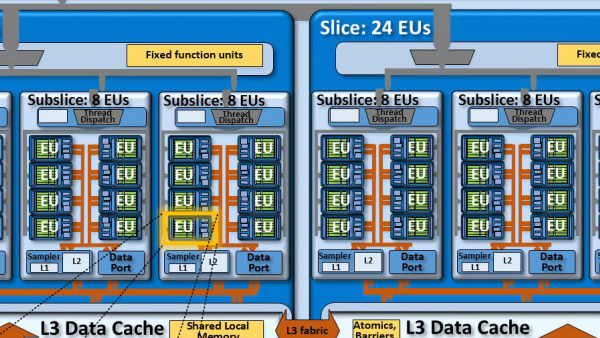

Gehören die integrierten Grafikeinheiten bei den Broadwell-CPUs noch zur Gen8, hält mit Skylake die Gen9 Einzug. Am grundlegenden Aufbau mit Slices, Subslices und Execution Units (EUs) ändert sich gegenüber der Gen8-Grafik von Broadwell nichts. Jeweils acht EUs bilden dabei ein Subslice. Ein Slice besteht in der Regel aus drei Subslices und somit 24 EUs, Varianten mit weniger Subslices sind aber denkbar. Während bei Broadwell der Maximalausbau aus zwei Slices mit insgesamt 48 EUs besteht, führt Intel mit Skylake eine vierte Stufe (GT4) ein, die drei Slices und entsprechend 72 EUs bietet.

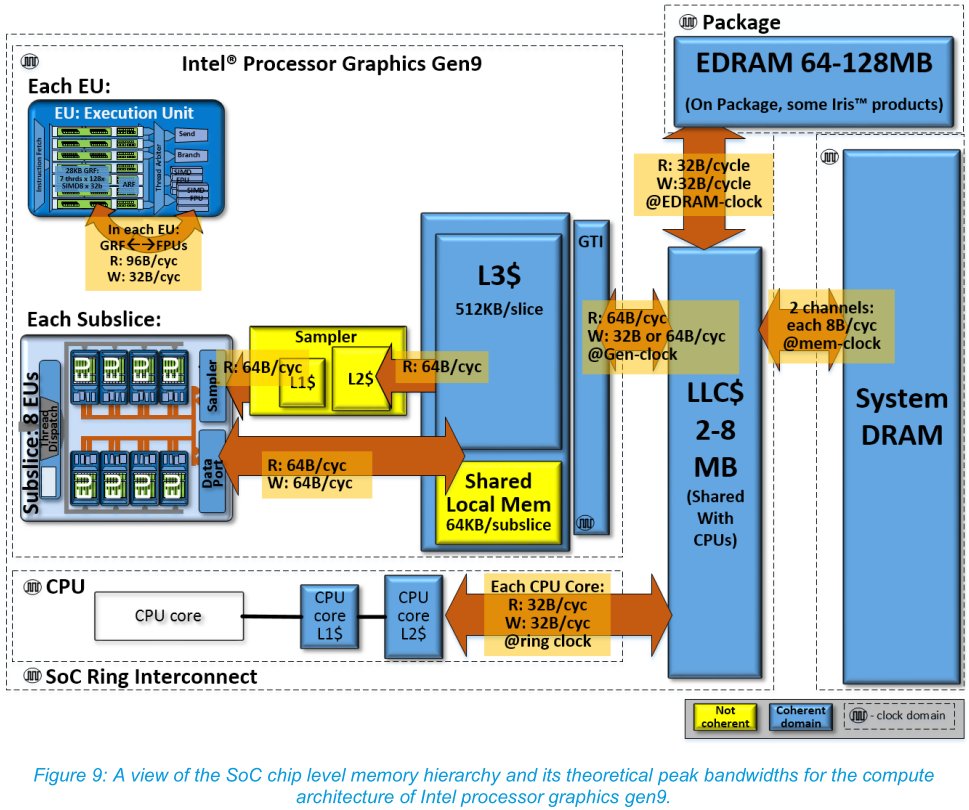

Bahnbrechende Änderungen gibt es auf Seiten der Architektur nicht. Intel spricht daher von „Verfeinerungen an der Mikroarchitektur“, die vor allem die Speicherhierarchie betreffen. Dazu zählen unter anderem neue Verwaltungsrichtlinien für das LLC-Management und eine Vergrößerung des verfügbaren L3-Cache auf 768 KByte pro Slice, wovon 512 KByte für Anwendungsdaten zur Verfügung stehen. Der EDRAM-Controller ist zudem in den System Agent umgezogen und befindet sich so in unmittelbarer Nachbarschaft mit dem Display-Controller, was bei der Bildwiederholung für niedrige Latenz und Effizienz sorgen soll. Verbesserungen im Bereich der Energieverwaltung werden angeführt, die zu einer reduzierten Leistungsaufnahme bei bestimmten Low-Power-Modi bei der Medienwiedergabe führen können.

Die geringen Unterschiede zwischen der Gen8 und der Gen9 werden auch an Intels Diagrammen zur Speicherhierarchie sowie den Tabellen zur theoretischen Leistung pro Takt deutlich. Die folgende Bildstrecke ermöglicht den direkten Vergleich.

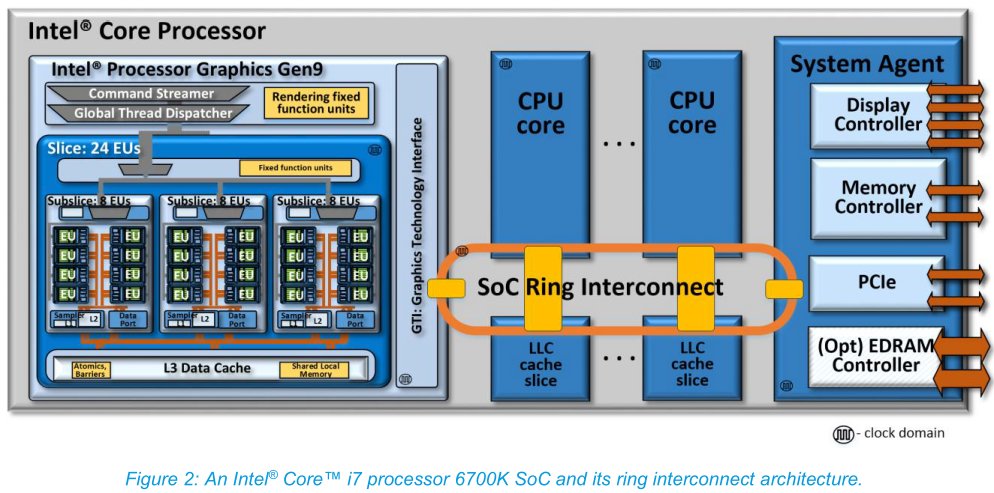

Die Skylake-Prozessoren setzen wie auch die Vorgänger Broadwell und Haswell auf eine Architektur, bei der CPU-Kerne, Grafikeinheit und System Agent über den sogenannten SoC ring interconnect miteinander verbunden sind. Dahinter verbirgt sich eine bi-direktionale Ringverbindung mit einem 32 Byte (256 Bit) breiten Daten-Bus. Für die verschiedenen Bereiche – CPU-Kerne, Grafik und Ringbus – ist eine Clock-Domain mit eigenem Frequenzbereich vorgesehen. Zum System Agent zählen die Controller für Display und Arbeitsspeicher, PCIe Express sowie den optionalen EDRAM, der nur bei bestimmten Skylake-CPUs zum Einsatz kommt. Über den System Agent laufen damit sämtliche externe Verbindungen vom und zum Prozessor.

Den Last Level Cache (LLC), also die letzte und langsamste Cache-Stufe des Prozessors, teilen sich CPU und GPU, mit dem Ziel, die Latenz zum DRAM zu verringern und um einen höheren Datendurchsatz (effective bandwidth) zu erzielen. Der LLC ist wie bei Haswell in Abschnitte (Slices) unterteilt, die jeweils einem Kern zugeordnet sind. Dennoch dient der LLC auch als großer gemeinsamer Cache über den Ringbus.

Nähere Details zu den Neuerungen bei der CPU-Architektur werden im Rahmen des IDF in den kommenden Tagen sowie mit der Markteinführung der breiten Skylake-Produktpalette ab September erwartet.