Intel Goldmont Plus: Große Überarbeitung ebnet Weg für ein 32-Kern-SoC

Intels Gemini Lake brachte die neue Architektur-Ausbaustufe Goldmont Plus in den Low-Cost-Markt, doch dahinter steckt noch mehr. Neue Details zeigen, dass die Architektur auch den Weg für einen Denverton-Nachfolger mit 32 Kernen frei macht.

Ein großes Plus

Intels Prozessorstarts sind in der letzten Zeit mit wenigen Informationen versehen, insbesondere die Details zur Architektur werden kaum noch öffentlich preisgegeben. Über eine aktualisierte Fassung des Optimization Manual (PDF) gibt Intel nun aber doch Einblicke, die offenbaren, dass sich bei Goldmont Plus (GLM+) gegenüber Goldmont (GLM) und Silvermont mehr geändert hat, als gedacht.

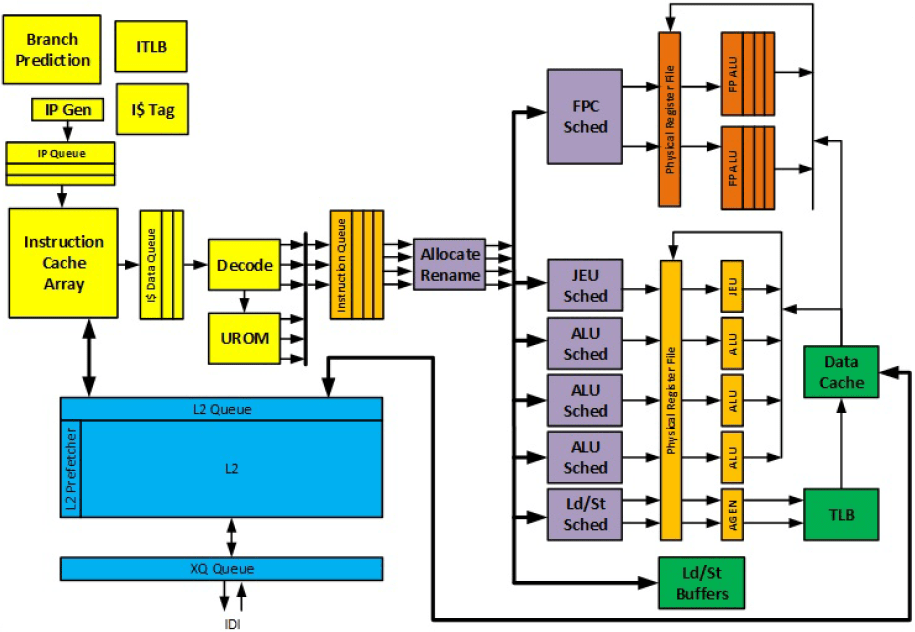

Im Front End wurde wie üblich an der Sprungvorhersage gefeilt, doch im Back End sind die großen Änderungen zugegen. So bleiben die Fetch- und Decode-Einheit beim 3-way-Design, doch ab dem Instruction Queue geht es mit vier Zuweisungen weiter. Zudem wurde der integer execution cluster (IEC) auf vier Ports verbreitert, am vierten Port hängt zudem eine weitere jump execution unit (JEU), die eine schnellere Sprungvorhersage bietet.

Parallel dazu wurden nahezu alle Buffer vergrößert (Reorder, Load, Store) und die L2-Caches ausgebaut. Während der reguläre L2-Cache bereits verdoppelt wurde, wird der L2-Precode-Cache sogar auf 64 KByte vervierfacht. Dabei handelt es sich in beiden Fällen um einen Shared Cache und macht nun klar, warum selbst die kleinsten Gemini Lake bereits vier MByte haben: Es gibt nur diesen einen Quad-Core-Die.

Mehr Bandbreite, geringere Latenzen

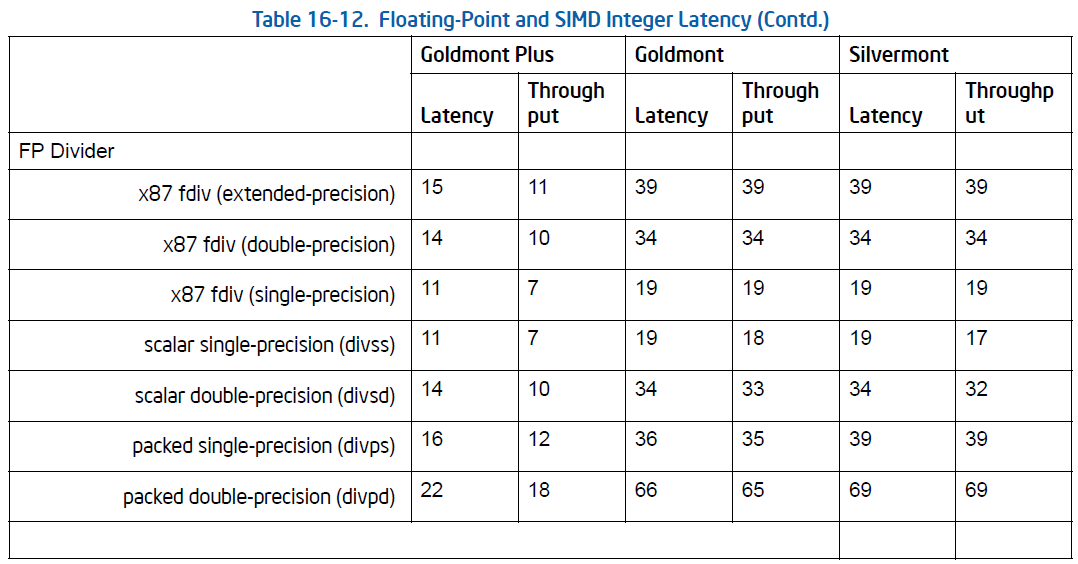

Für die Programmierer, für die der Leitfaden gedacht ist, zeigt sich die größte Änderung aber beim floating point divider. Dieser wurde ebenfalls überarbeitet, um moderne Instruktionen (radix-1024) schneller umzusetzen, was sich bei der gestiegenen Bandbreite und deutlich geringeren Latenzen zeigt. Erste Benchmarks reagieren bereits auf die Anpassungen und zeigen Ergebnisse mit großen Zugewinnen.

Vier-Kern-Cluster ermöglichen theoretisch einen 32-Kern-SoC

Auch das gesamte interne Design wurde umgestellt. Es ist nun auf vier Kerne mit 4 MByte L2-Cache als geteilte Ressource ausgelegt. Zuvor wurde intern eine Hierarchie von zwei Kernen mit je zwei MByte L2-Cache genutzt. Diese auf den ersten Blick wenig interessante Information öffnet jedoch neue Wege, wie Wikichip erklärt. Denn bereits mit der ersten Atom-Architektur-Auskoppelung für den professionellen Markt, Codename Avoton, nutzte Intel dieses modulare System, um vier Zwei-Kern-SoC zu einem Acht-Kern-SoC zu verschmelzen, die über ein intra-die interconnect (IDI) mit dem System Agent verbunden sind und so auch mit den anderen Clustern kommunizieren.

Denverton als aktuelle Generation Atom C3000 ging noch einen Schritt weiter: Acht dieser Zwei-Kerner bereits auf Basis der Goldmont-Architektur wurden zum ersten 16-Kern-SoC. Mit der jetzigen Verdoppelung auf vier Kerne würde bei einem gleichen Schritt der erste 32-Kern-SoC in diesem Bereich von Intel aufgestellt werden können. Ein weiterer Ausbau von acht auf zwölf Zusammenschaltungen würde sogar ein 48-Kern-SoC ermöglichen und so eventuell ein Gegenstück zu den neuen ARM-Server-Prozessoren mit ähnlicher Kern-Anzahl bilden. Dieses Einsatzgebiet würde stark von den Anpassungen am Cache und den generellen Überarbeitungen profitieren. Doch dabei handelt es sich nur im frühe Gerüchte, deren Umsetzung noch offen ist.