Flash-Speicher: Sk Hynix hat seinen „4D‑NAND“ vorgestellt

SK Hynix zeigt sich kreativ und nennt die kommende 96-Layer-Generation seines 3D-NAND schlicht 4D-NAND. Eine bahnbrechend neue Entwicklung verbirgt sich dahinter allerdings nicht. Wie schon andere Hersteller packt SK Hynix künftig die Chip-Logik in eine eigene Ebene unter den Speicherschichten.

SK Hynix macht aus 3D-NAND „4D-NAND“

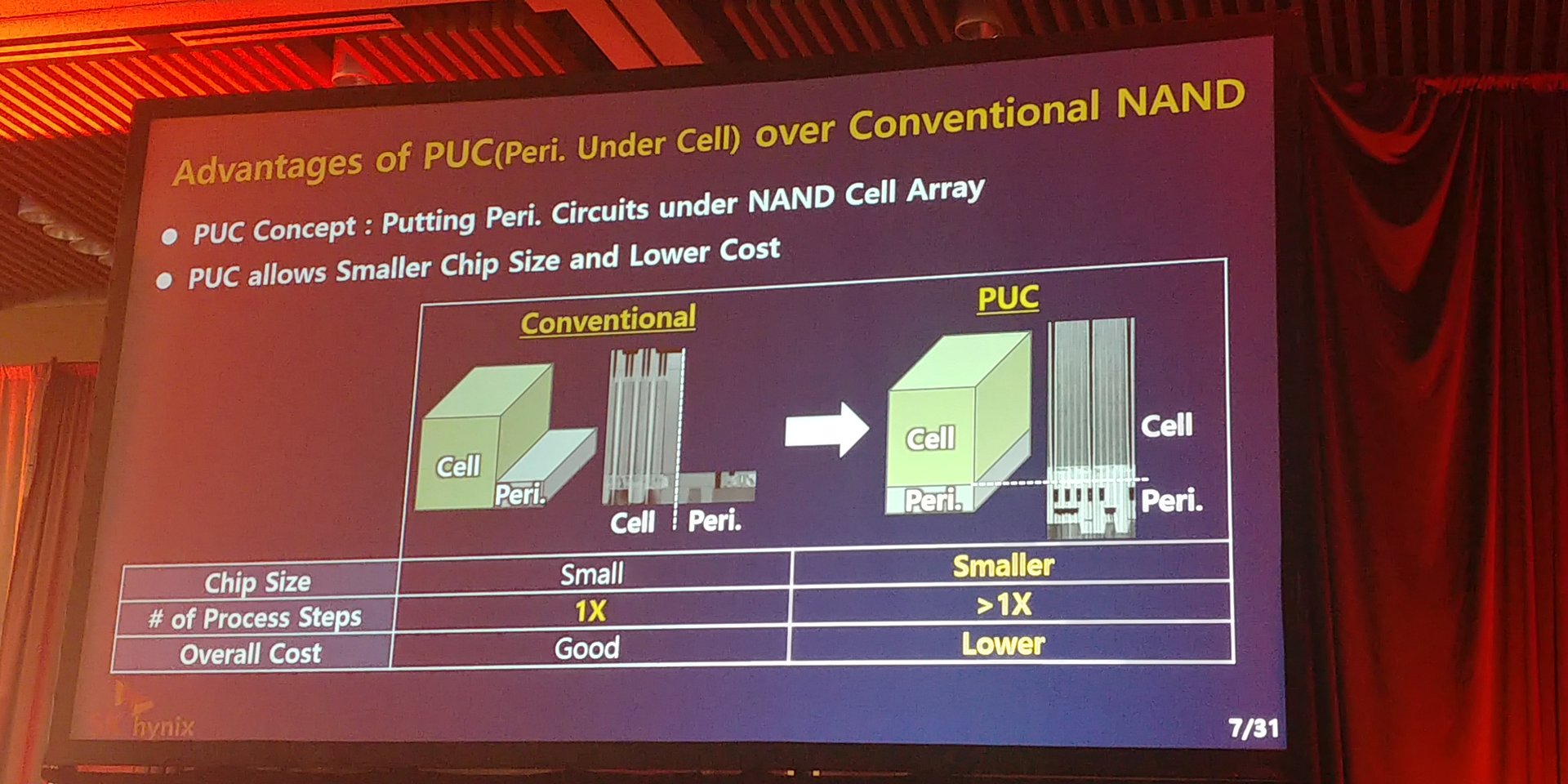

Intel und Micron hatten diesen Ansatz als CMOS under Array (CuA) zuerst verfolgt und die Chip-Peripherie unter die Schichten (Layer) ihres 3D-NAND gepackt. Dadurch lässt sich gegenüber der herkömmlichen Bauart, bei der der I/O-Bereich am Rand des Chips platziert ist, Fläche einsparen. Kleinere Chips bedeuten niedrigere Kosten.

Der Unterschied zum 3D-NAND von Intel und Micron besteht in der grundlegenden Architektur. Intel und Micron verwenden als einzige NAND-Hersteller eine Floating-Gate-Technik, während alle anderen, Samsung, Toshiba und Western Digital sowie SK Hynix, stattdessen auf Charge-Trap-Flash (CTF) setzen. Die Kombination aus CTF und „Periphery Under Cell“ (PUC) nennt SK Hynix nun 4D-NAND.

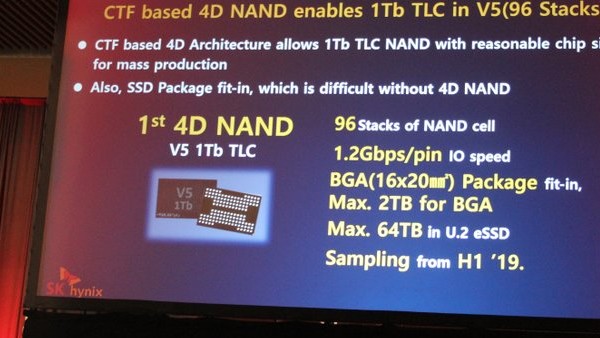

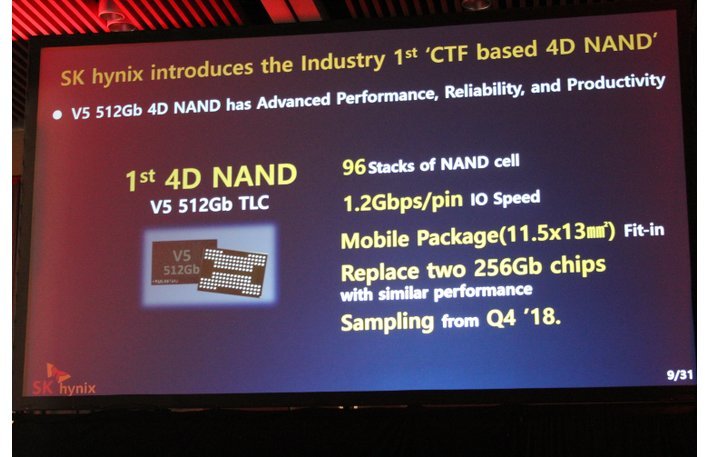

Die V5 genannte Generation des 3D-NAND von SK Hynix erhöht die Zahl der Speicherebenen von 72 auf nun 96 Layer. Es handelt sich um TLC-3D-NAND mit drei Bit pro Speicherzelle, der in Varianten mit 512 Gbit und später 1 Terabit pro Die gefertigt wird. Auch die Datenrate des V5 von SK Hynix wurde angehoben und beträgt nun 1,2 Gbit/s. Samsungs fünfte Generation V-NAND soll dagegen schon 1,4 Gbit/s erreichen. Der chinesische Neuling YMTC hat sogar 3 Gbit/s in Aussicht gestellt, allerdings ist dies noch Zukunftsmusik.

-

SK Hynix: 96-Layer-3D-NAND V5 („4D-NAND“) mit 512 Gbit als TLC-Version (Bild: Tom's Hardware)

SK Hynix: 96-Layer-3D-NAND V5 („4D-NAND“) mit 512 Gbit als TLC-Version (Bild: Tom's Hardware)

SK Hynix verspricht Leistungssteigerungen von 25 und 30 Prozent beim Lesen und Schreiben gegenüber Generation V4 mit 72 Layern. Die Energieeffizienz soll sich sogar mehr als verdoppeln, hier spricht der Hersteller von „150% mehr Bandwidth/Power“. Für niedrigere Kosten soll die um 30 Prozent reduzierte Chip-Fläche sorgen.

V5 kommt erst als TLC und später als QLC

Im vierten Quartal 2018 will SK Hynix die ersten 512-Gbit-Chips des V5-3D-NAND alias „4D-NAND“ zur Bemusterung bereitstellen. Samples der 1-Terabit-Variante sollen innerhalb des ersten Halbjahres 2019 bereit stehen.

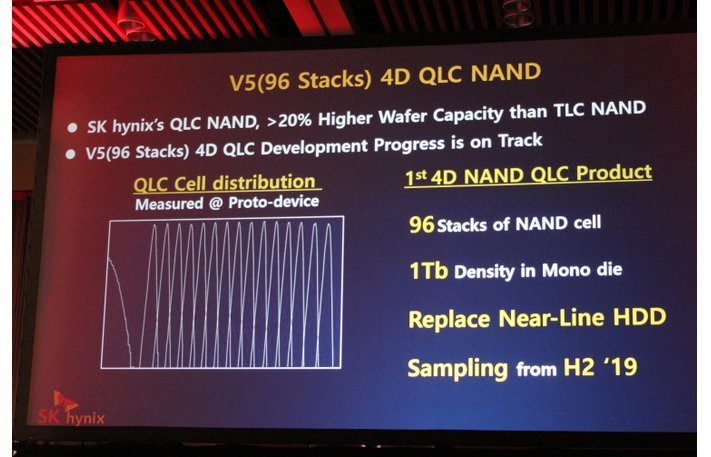

Im zweiten Halbjahr 2019 soll dann die Bemusterung des ersten QLC-NAND (4 Bit pro Zelle) von SK Hynix folgen. Hierfür hat der Hersteller eine Variante des V5-3D-NAND mit 96 Layern vorgesehen. Bei erneut 1 Terabit Speicherkapazität soll das QLC-Design mehr als 20 Prozent der benötigten Wafer-Fläche einsparen. Bis dahin haben die anderen Hersteller längst Produkte mit QLC-NAND auf dem Markt. Intel und Micron haben ihren QLC-Flash schon Ende Mai vorgestellt, der in ersten SSDs wie der Micron 5210 ION und der Intel SSD 660p steckt. Auch Samsung, Toshiba und Western Digital sind bei QLC-NAND weiter als SK Hynix.

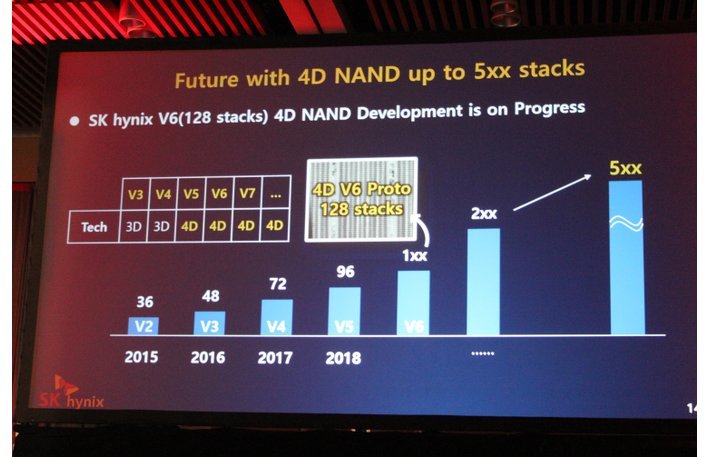

SK Hynix hat noch einen Blick in die Zukunft gewagt und für Generation V6 erwartungsgemäß 128 Layer angekündigt. In Ferner Zukunft soll die Zahl der Zellschichten auf über 500 steigen, so die Prognose des Herstellers.

Erste SSDs mit neuem NAND und ein neues Übertragungsprotokoll

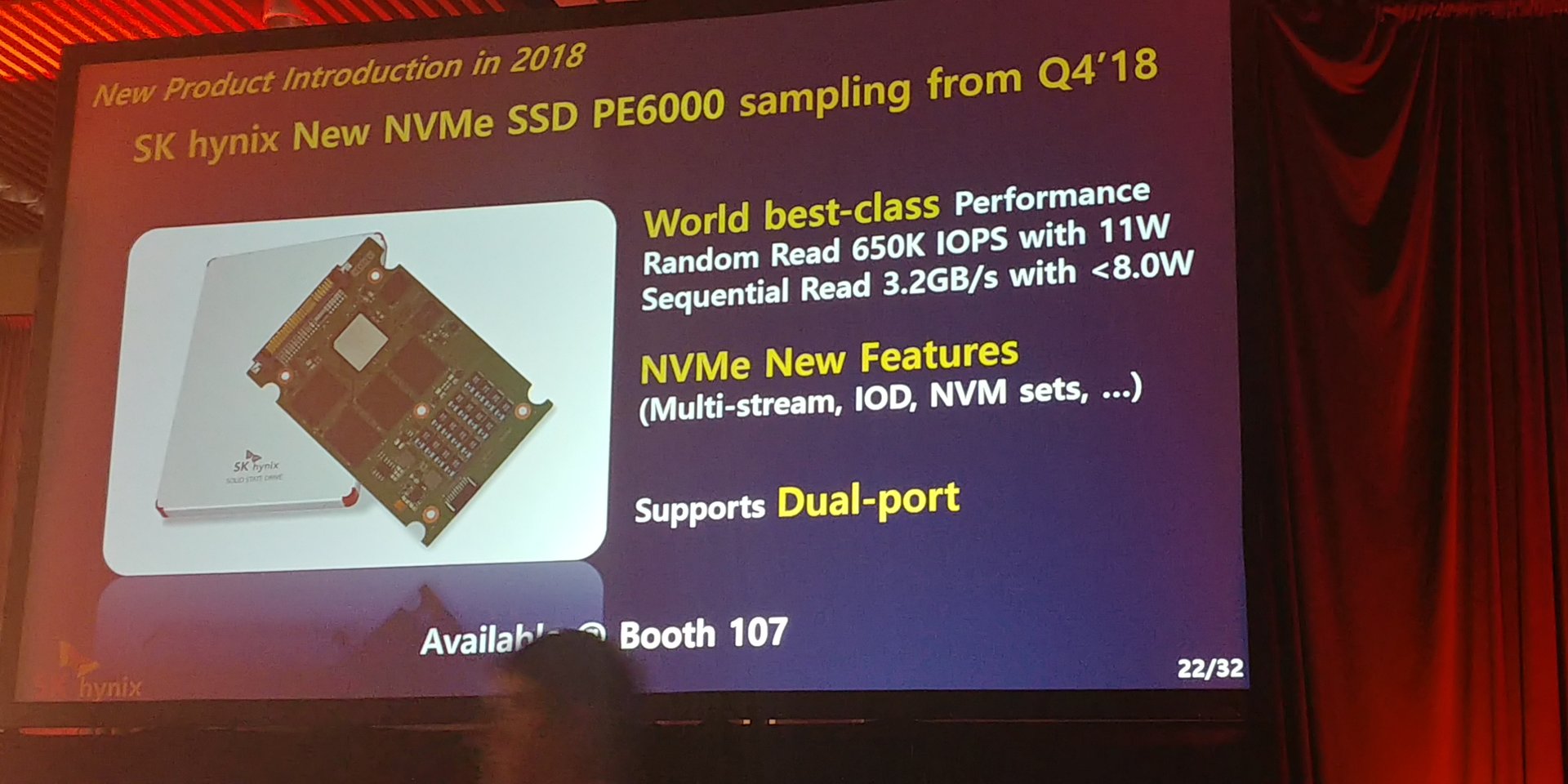

Im Bereich der SSDs von SK Hynix wurden neue Produkte für Unternehmen vorgestellt. Darunter ist mit der SE4011 eine SATA-SSD mit 72-Layer-3D-NAND und mit der PE6000 eine NVMe-SSD mit U.2 und 650.000 IOPS, die schon den 96-Layer-NAND besitzen soll.

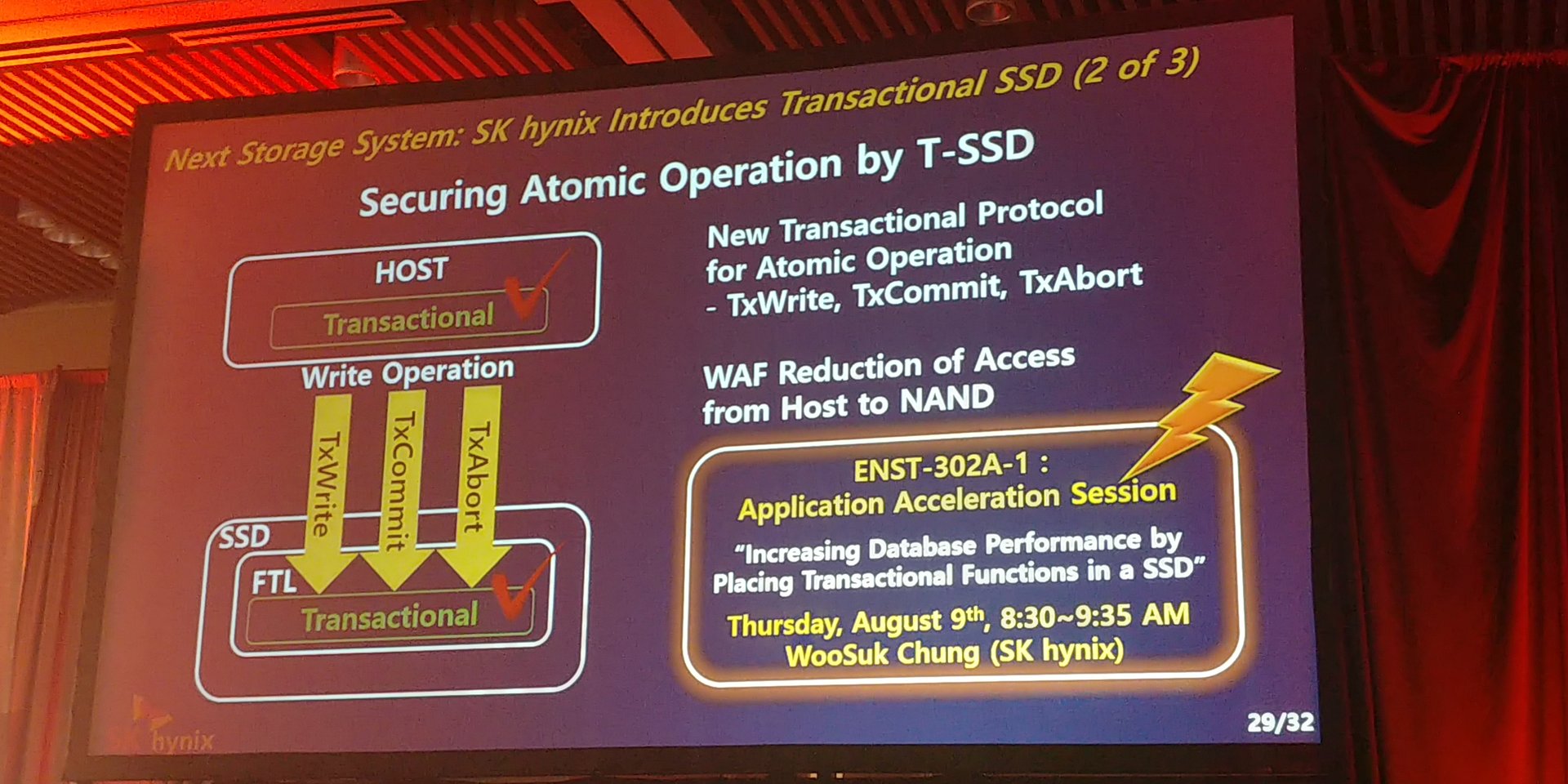

Ferner arbeitet SK Hynix an einem neuen Übertragungsprotokoll: Die „Transactional SSD“ soll 40 Prozent mehr Transaktionen pro Sekunde erreichen und die Write Amplification um 30 Prozent reduzieren.

Weitere Informationen sind der Berichterstattung von AnandTech und Tom's Hardware zu entnehmen, die beim Flash Memory Summit vor Ort waren.